基于Dragonboard 410c的总线控制之SPI(一)

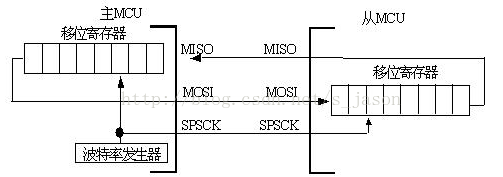

SPI是另一种常用的总线,可靠性相对于I2C和UART来说,稍差一些,可以实现全双工同步通信,标准是4线,分别是:SDI(数据输入)、SDO(数据输出)、SCLK(时钟)、CS(片选)。根据不同的场景和需求,也可以使用3线。速度可以达到50MHZ,

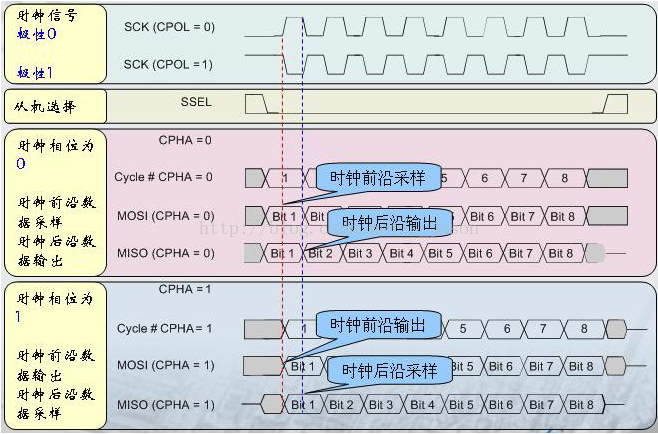

SPI有4中模式,只有当通信双方处在相同模式下才能正常通信。这4种模式由CPOL(时钟极性)和CPHA(时钟相位)来决定的。

CPOL=1:当SCLK=1时处于空闲状态,有效状态是SCLK处于低电平时。

CPOL=0:当SCLK=0时处于空闲状态,有效状态是SCLK处于高电平时。

CPHA=1:数据采样在第二个边沿,数据发送在第一个边沿。

CPHA=0:数据采样在第一个边沿,数据发送在第二个边沿。

例如:

CPOL=0,CPHA=0:此时空闲状态SCLK为低电平,数据采样在第一个边沿,即SCLK由低电平向高电平跳变时,也就是上升沿采样,下降沿发送数据

CPOL=0,CPHA=1:此时空闲状态SCLK为低电平,数据采样在第二个边沿,即SCLK由高电平向低电平跳变时,也就是下降沿采样,上升沿发送数据

CPOL=1,CPHA=0:此时空闲状态SCLK为高电平,数据采样在第一个边沿,即SCLK由高电平向低电平跳变时,也就是下降沿采样,上升沿发送数据

CPOL=1,CPHA=1:此时空闲状态SCLK为高电平,数据采样在第二个边沿,即SCLK由低电平向高电平跳变时,也就是上升沿采样,下降沿发送数据

SPI没有像I2C和UART那样的起始/终止信号,所以只能通过控制时钟线保持高/低来停止数据的传输。