一文读懂“JESD204B”之链路建立与xilinx IP仿真

一、初识

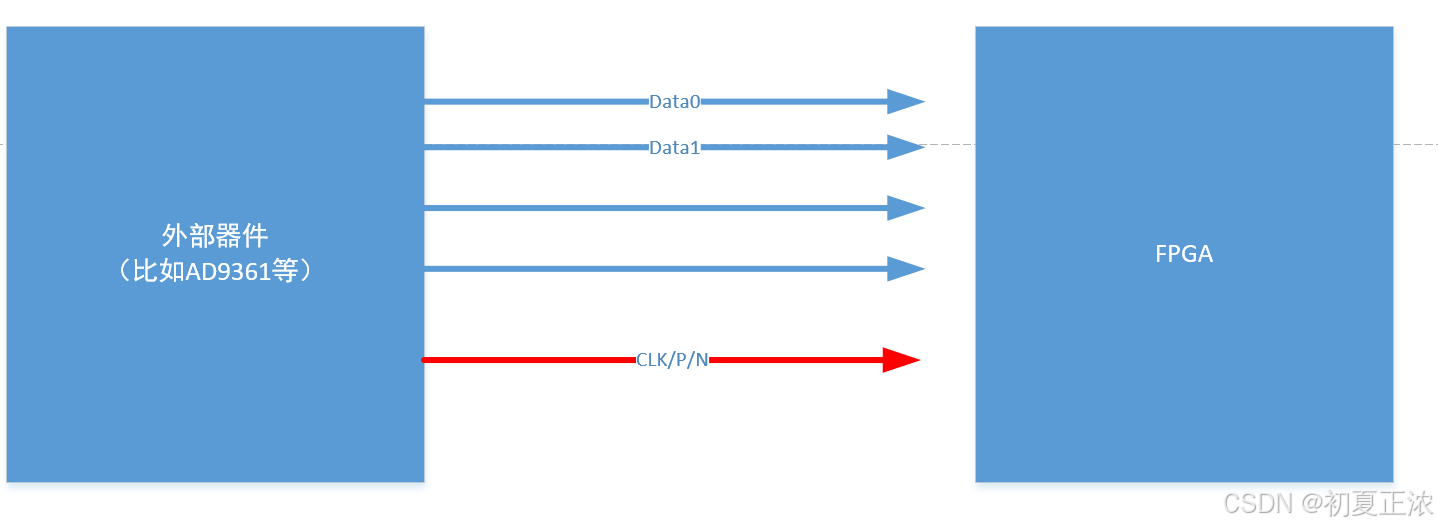

JESD204B 是由JEDEC(电子器件工程联合会)制定的高速串行接口标准,主要用于数据转换器(ADC/DAC)与数字处理器(如FPGA、ASIC)之间的数据传输。在JESD标准出来前,常用的是传统的LVDS接口:LVDS(Low-Voltage Differential Signaling,低压差分信号)是一种广泛应用的物理层电气标准,用于高速、低功耗的差分信号传输,但是在使用LVDS接口时,对阻抗和多通道时延要求比较严格,因为LVDS使用的是源同步接口,允许时钟和多个数据通道同时传输,时钟信号和数据保持确定的相位关系,同时由发送端(图中的外部器件)传输至接收端(比如FPGA)。接收端利用对端传送来的时钟信号作为采样时钟,对数据位进行采样。在采样过程中,只要保证接收端时钟信号与接收数据满足一定的建立/保持时间,数据即可被正确接收。

图 1 源同步LVDS接口

因此我们可以知道,LVDS对各通道的时延要求是比较高的,因此PCB布线要求也比较严格,差分对需阻抗匹配(100Ω±10%)和等长控制(长度差1 ps可能导致采样偏差。。

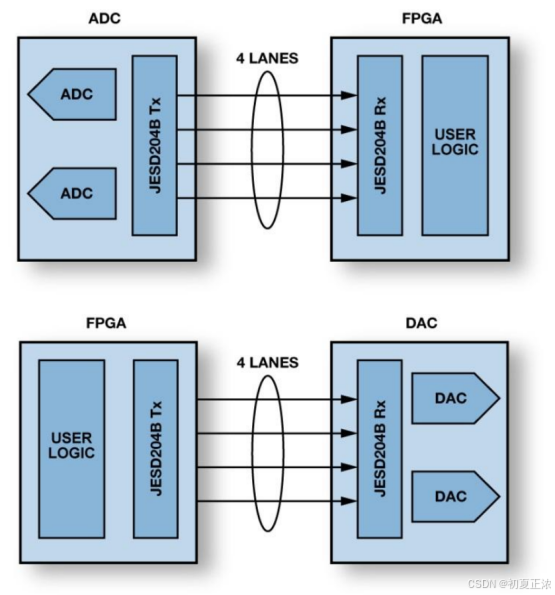

对于JESD204B协议而言,它为多通道高速数据转换器设计的端到端协议标准,含完整的同步和校验机制,是一种高速串行接口标准,该协议支持高达12.5 Gbps的数据速率。物理接口上,它依靠的是高速收发器进行数据收发同步与校验,即串行收发数据,这也就意味着数据接口路由所需电路板布线空间更少,适用于需要高带宽和高可靠性的应用场景,相比与LVDS它的线更少,建立与保持时序要求更低及转换器和逻辑器件的封装更小。因此在高速AD/DA芯片中很常用,并且在通信AD/DA IC中,未来将会越来越主流。其使用率正在稳步上升,并且有望成为未来转换器的协议标准。

JESD204B 行业标准用于串行接口的开发,旨在以高效和节省成本的方式解决将 最新的宽带数据转换器与其他系统 IC 连接的问题。其动机是通过使用可扩展的高速串行接 口来标准化接口,从而减少数据转换器与其他设备,比如 FPGA(现场可编程门阵列)和 SoC(片上系统)之间的数字输入/输出数量。

。

图 2 JESD连接

二、JESD204B结构

JESD204B协议层协议层主要包括四层,分别为:物理层、链路层、传输层、应用层。

物理层是基础,它基于高速SerDes(如Xilinx GTY、GTX)的电气接口,支持多通道绑定。

物理层之后就是链路层,主要包括处理加扰(SCRAMBLING)、8B/10B编码、链路同步(CGS/ILAS);传输层主要是数据对应关系其中包括定义数据映射规则(如采样分帧、通道分配),应用层:用户得到最终IQ数据。、

JESD204协议定义了三种子类模式(Subclass 0/1/2),用于解决多器件时钟同步与确定性延迟问题链路建立。

(小小提示一下:接下来的术语可能你暂时看不太懂,比如什么LMFC,sysref,确定性延时等,没关系,你看完后文你就懂这里术语的意思了,在这儿你只需要大致知道这几个子类区别是什么就行啦,嘻嘻)

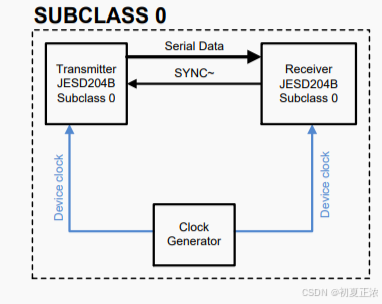

Subclass 0

- 无全局同步信号:依赖设备自身时钟(Device Clock)的相位对齐,通过本地多帧时钟(LMFC)实现单器件内的多通道同步。

- 无确定性延迟:不同器件的LMFC可能随机偏移,无法保证跨器件的固定延迟。

图 3 Subclass 0

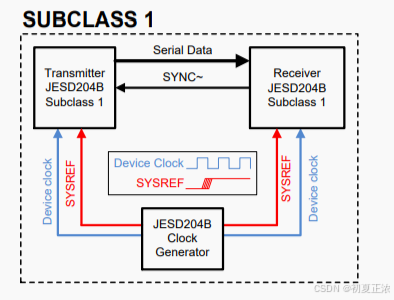

Subclass 1(用的比较多的类,也是本文的重点)

- 全局同步信号(SYSREF):所有器件(FPGA、ADC、DAC)接收同一SYSREF信号,对齐各LMFC的相位。

- 确定性延迟:链路建立后,数据传输延迟固定(±1 LMFC周期),支持多器件纳秒级同步。

图 4 Subclass 1

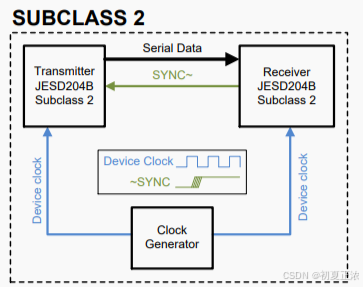

Subclass 2

- 运行时重配置:支持在不复位链路的情况下,动态调整LMFC相位或数据传输参数(如延迟补偿)。

- 确定性延迟+动态性:在Subclass 1的基础上,增加了链路状态机(如重新同步请求)。

图 5 Subclass 2

综合对比 ,总结一下:

特性

Subclass 0

Subclass 1

Subclass 2

同步信号

无

SYSREF

SYSREF

确定性延迟

不支持

固定延迟(±1 LMFC周期)

固定延迟+可动态调整

多器件同步

仅单器件

全局对齐

全局对齐

动态重配置

不支持

需复位链路

支持运行时调整

复杂度

低(已过时)

中(需SYSREF管理)

高(状态机及动态逻辑)

前面铺垫了这么多,接下来的才是重头戏,请各位看官,准备好瓜子儿 、茶水,坐好听我细细数来~

三、链路层同步机制建立

Jesd204b的物理层是基于高速串行收发器进行的,因此物理层对于本文而言是比较通用的,在XILINX FPGA中,不管是aurora、万兆网、SRIO等都是基于高速串行收发器进行的,后面我会考虑出一篇文章专门说下GT收发器。

在本文中,我就跳过了物理层,直接进入链路层,这才是JESD204B的重点。

首先,我们假设一下,在上面图2中,我们作为FPGA这一侧,我们想把外部AD芯片的IQ数据完整读取过来,我们应该怎么做,我觉得你应该会想到:首先我得知道什么时候,AD芯片会传数据过来,其次我得知道数据线上传过来的是啥数据,最后我得知道这些数据是怎么排列的,我要怎么去发数据......,如果你是这么想的,那么恭喜你,你已经初步知道JESD204B的链路建立的规则了.......(猝不及防的惊喜,略带怀疑的想法:真这样?)

由于JESD204协议中,常用的就是Jesd204b subclass1 ,因为它既优化了subclass0中的缺少确定性延时不足,也为subclass2的动态调整打下了基础,所以在该文中主要说明的是subclass1,在其链路建立过程中,总共分为三个阶段:

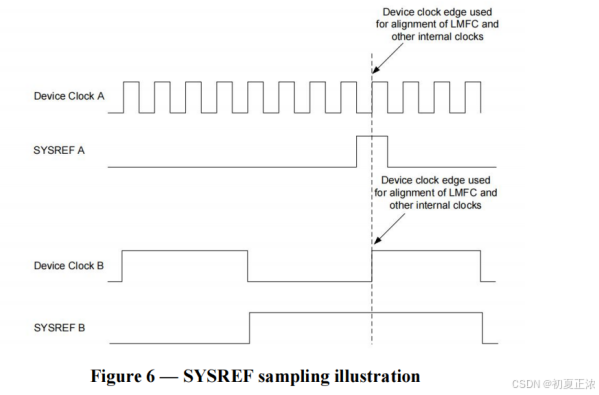

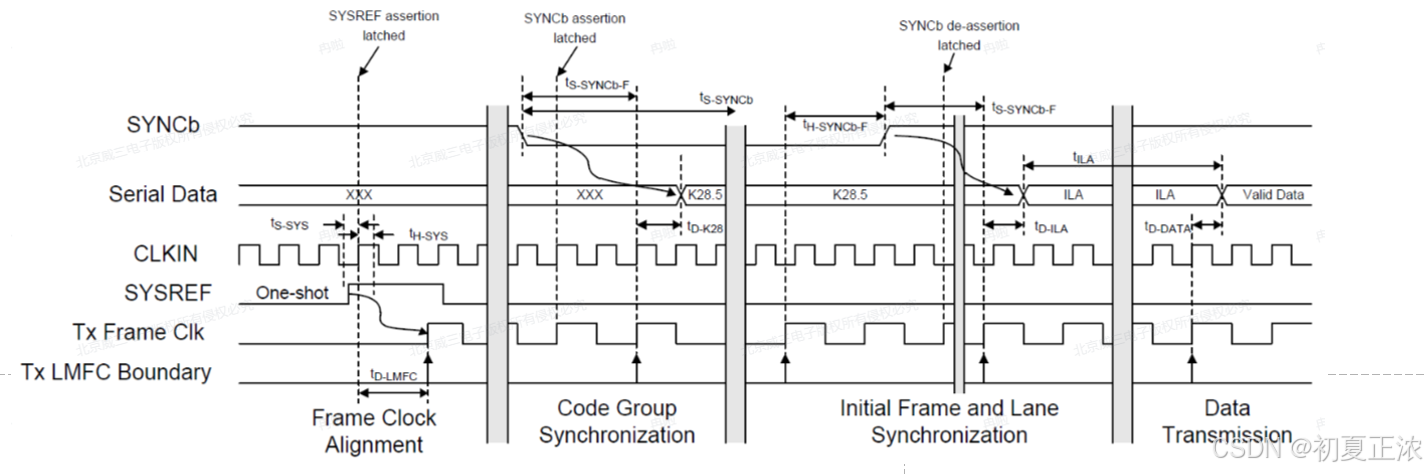

第一个阶段为SYSREF阶段:这个阶段是干啥的呢?通俗点说,就类似于百米比赛中的发令枪,当监测到sysref时,就开始正式进行同步流程,这个信号是怎么来的呢?如图13所示,外部的时钟源为AD芯片和FPGA提供device clk和sysref,这个device clk就相当于基准时钟源,所有的链路建立都以该时钟为基础,Device Clock经过分频后得到帧时钟Frame Clk和多帧时钟LMFC,该阶段中主要是检测sysref的状态,对于检测sysref的状态也有两种方式,第一种是oneshot,即只需要捕获一次sysref就行,时钟源只需要在开始前提供几个周期的sysref信号,下一次再提供则是整体架构复位之后重新link时才会提供,另外一种是continue模式,即SYSREF信号以固定频率(通常与LMFC同频)持续发送,器件在每个SYSREF上升沿动态校准LMFC相位,这种常用于多器件同步。

One-Shot模式:适合短期运行、环境稳定的小型系统,强调低功耗和简单设计。

Continuous模式:用于高精度、多器件、长时间运行的工业场景,通过持续校准保障同步稳定性。

同时,在使用时要确保sysref与device_clk的相位满足建立/保持时间。

图 6 SYSREF时序要求

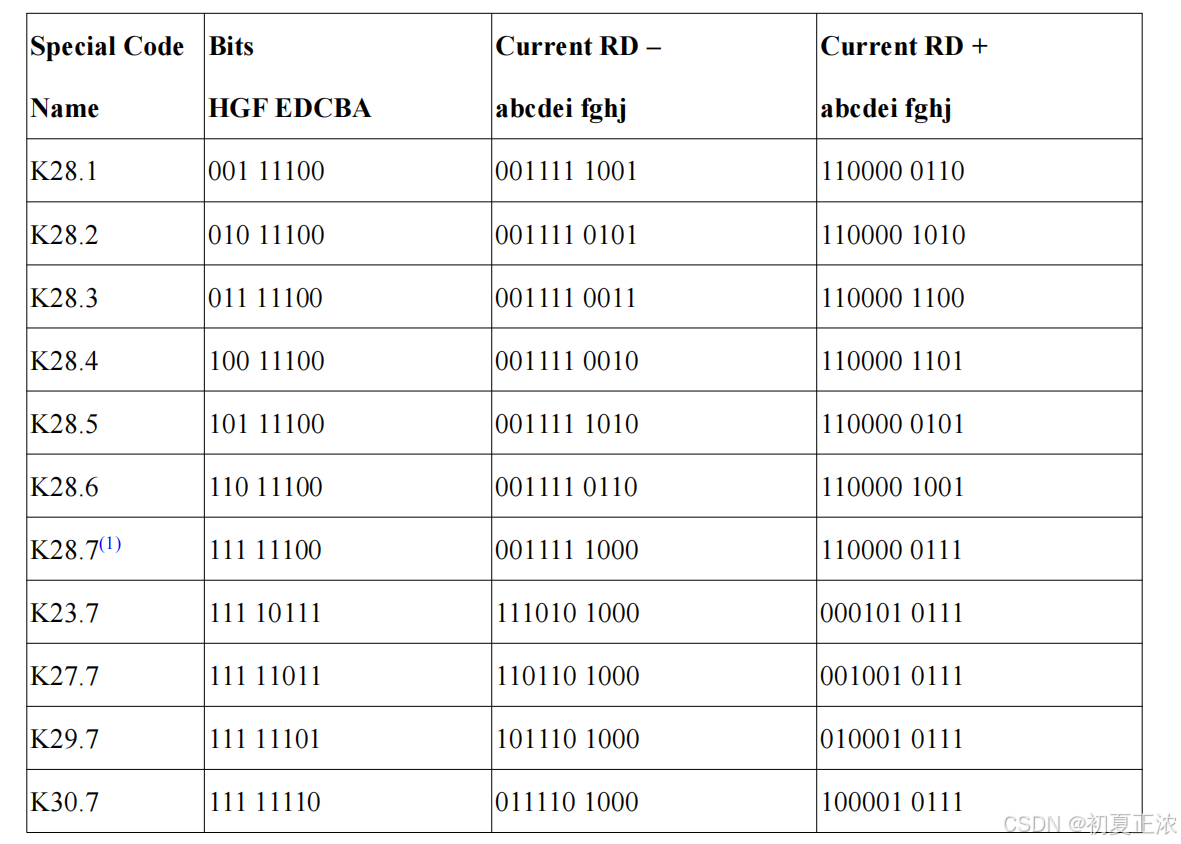

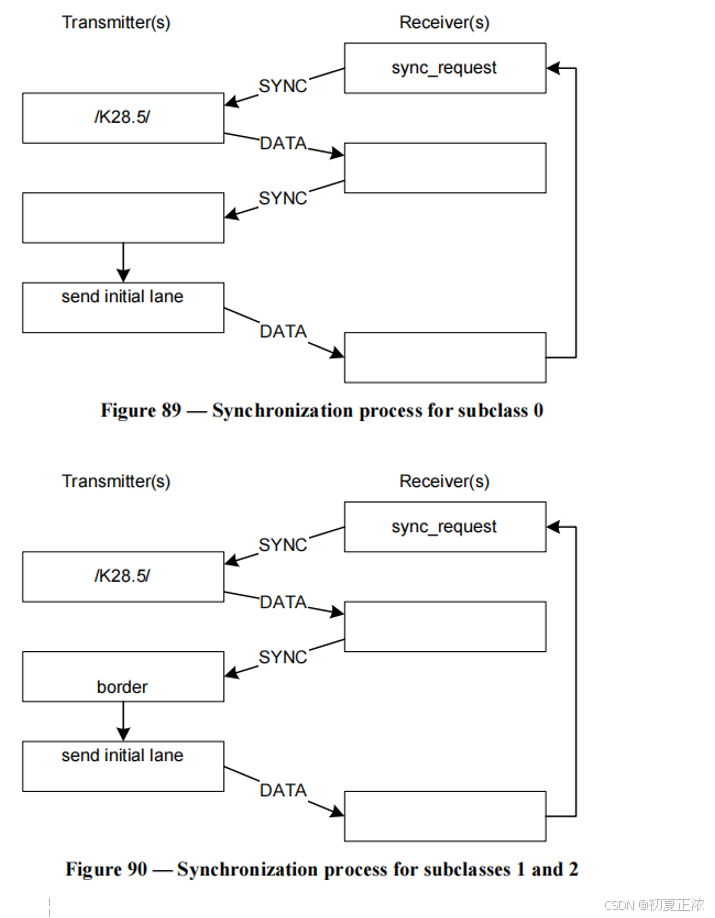

第二个阶段为组码同步阶段(code group synchronization)在subclass1中是tx发送K28.5,当rx连续收到4个K28.5时(但是在xilinx IP的仿真中是识别到20个K码),则会把sync拉高,准备进入第三个阶段ILAS阶段(IInitial lane alignment sequence)。简单解释一下就是:当rx收到连续的n个个K28.5时,会告诉TX:“我已准备OK,流程可以继续往下走了”,那他是怎么告诉TX的呢?会把sync拉高。当TX捕捉sync信号的改变时,TX会在下一个本地多帧时(LMFC)边界上启动ILAS阶段。

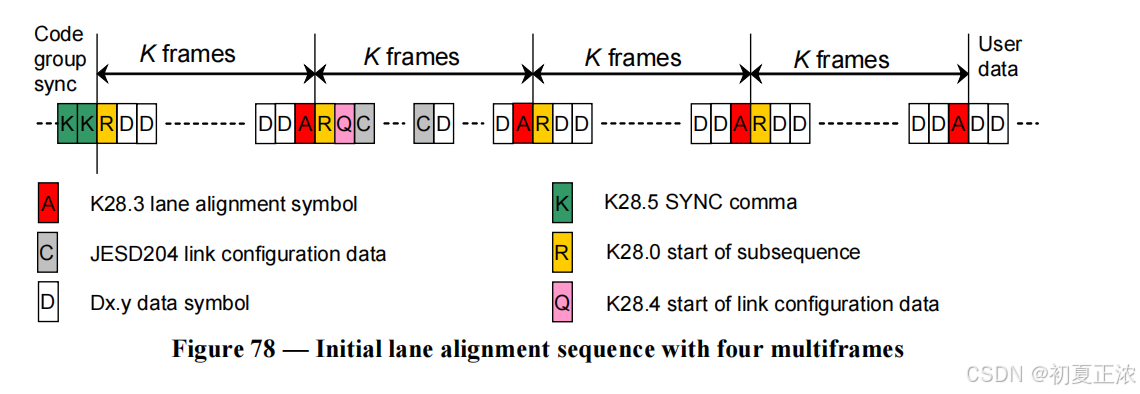

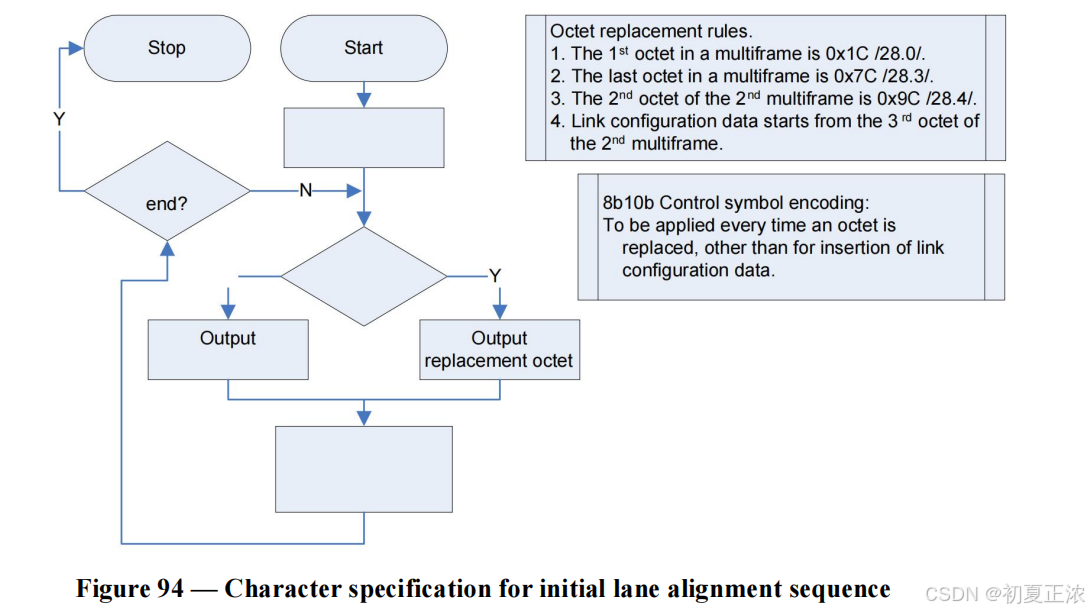

第三个阶段为初始通道对齐阶段(Initial lane alignment sequence),在该阶段里主要完成通道对齐,在该阶段中,主要发送4个多帧,即4个帧序列,如图7中:“K frame”,

图 7 ILAS同步说明

图 8 K码序列表

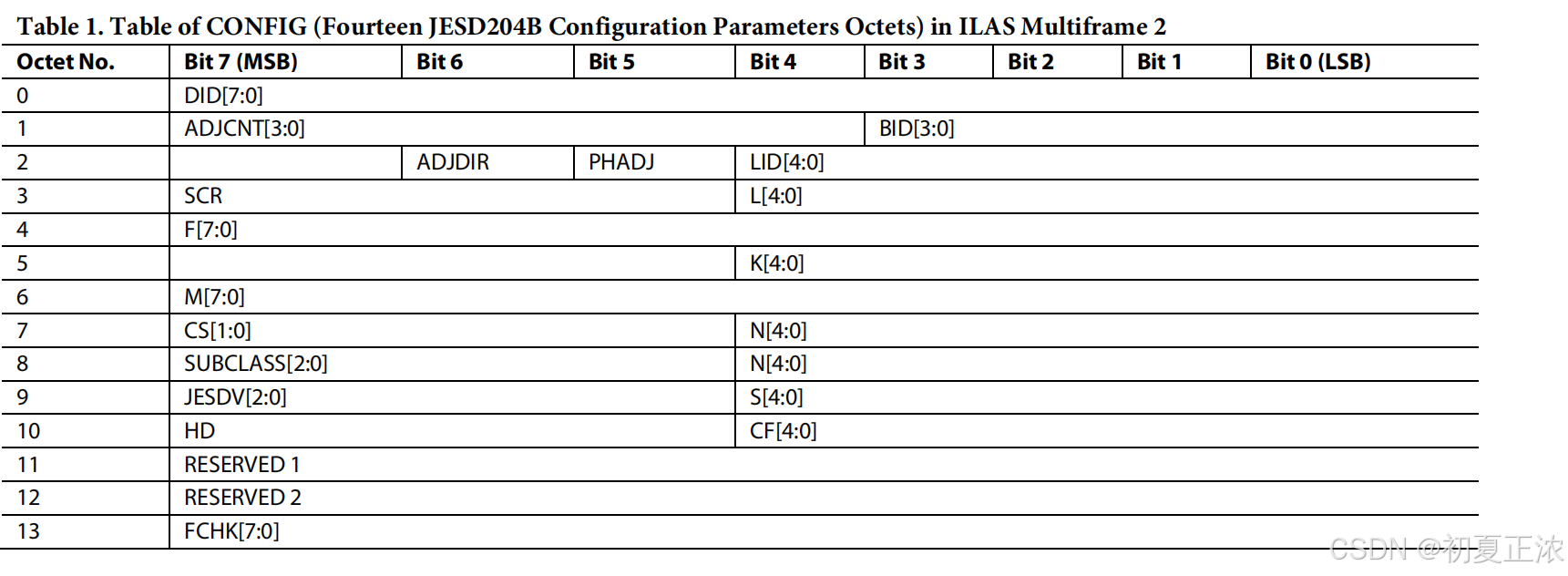

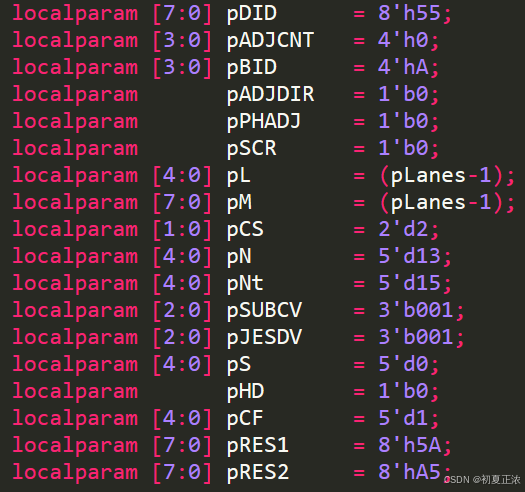

这个序列是有一定的规则的:比如多帧是以K码K28.0开头,D数据为累加数,A为多帧结束标志,第二个多帧的前14个C数据为配置数据等。并且累加数也有其特定的规则,怎么去累加,控制字符算不算累加数等,图9介绍了配置数据的具体说明,每个配置参数的具体含义可去看手册《JEDEC STANDARD-Serial Interface for Data Converters》。

图 9 多帧累加数规则

图 10 配置数据详解

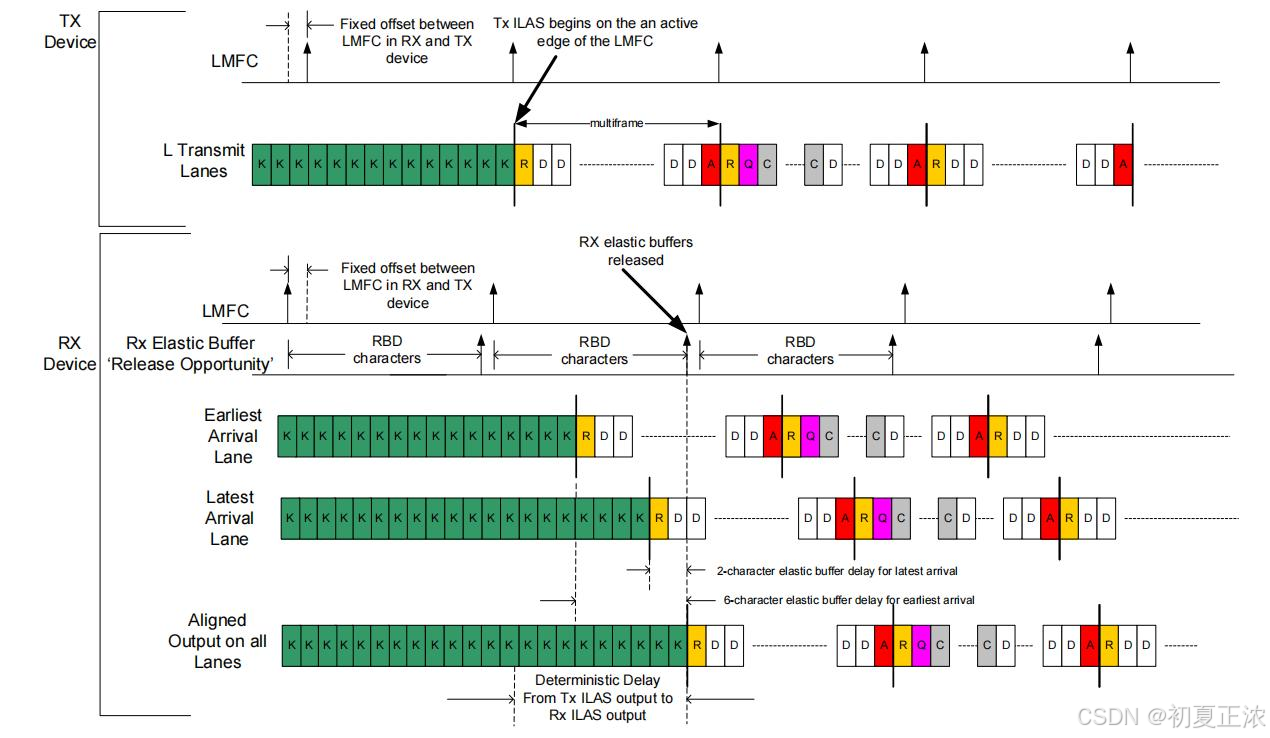

说到这里,可能大家对单通道的对齐有初步理解了,单对于JESD204B来说,它是如何保证多通道对齐的呢?

多通道对齐

由于每个通道的时延不一致,检测到多帧的时间也不一致,因此如上图接收端检测到字符/R/(K28.0)之后,接收端会把/R/(K28.0)后面的数据存入一个深度可设置的BUFFER中,当下一个LMFC边沿到来,且所有通道的BUFFER中都有数据时,所有通道的BUFFER数据开始输出,从而实现通道间的数据对齐。

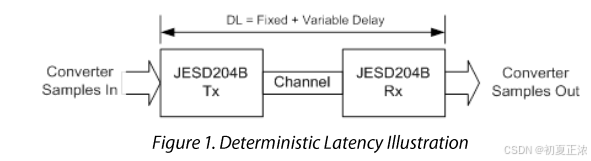

说到多通道对其那就必须要补充一下确定性延迟:JESD204B 标准定义了确定性延迟(DL),它表示帧式样本到达串行发送器时与帧式样本从 串行接收器输出之间的时间差。如图所示

在 JESD204 系统中,确定性延迟包括固定延迟和可变延迟。可变延迟是由于数字处理块中 时钟域之间的任意相位关系在电源周期之间不一致而产生的。即确定性延迟被定义为从 TX 设备的并行帧数据输入到 RX 设备的并行帧数据输出

因此整个链路建立的流程就如图10和图11所示:

图 11 子类0-2的同步过程

图 12 同步具体流程

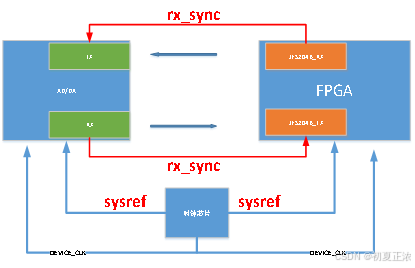

现在的整体架构如图13所示,常见的芯片有AD9009,9371,等芯片

图 13 整体架构

四、Xilinx IP的仿真

4.1 IP设置

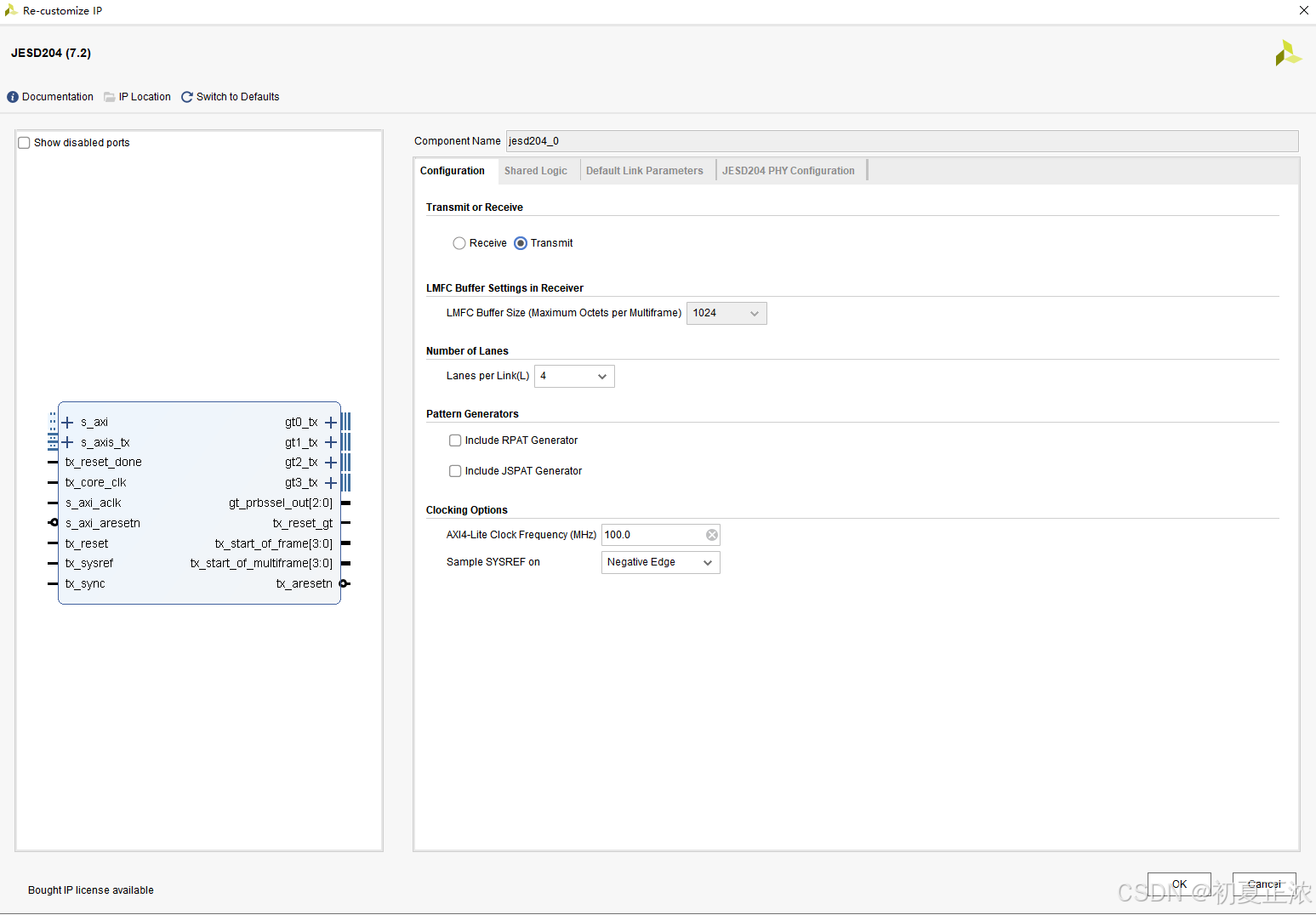

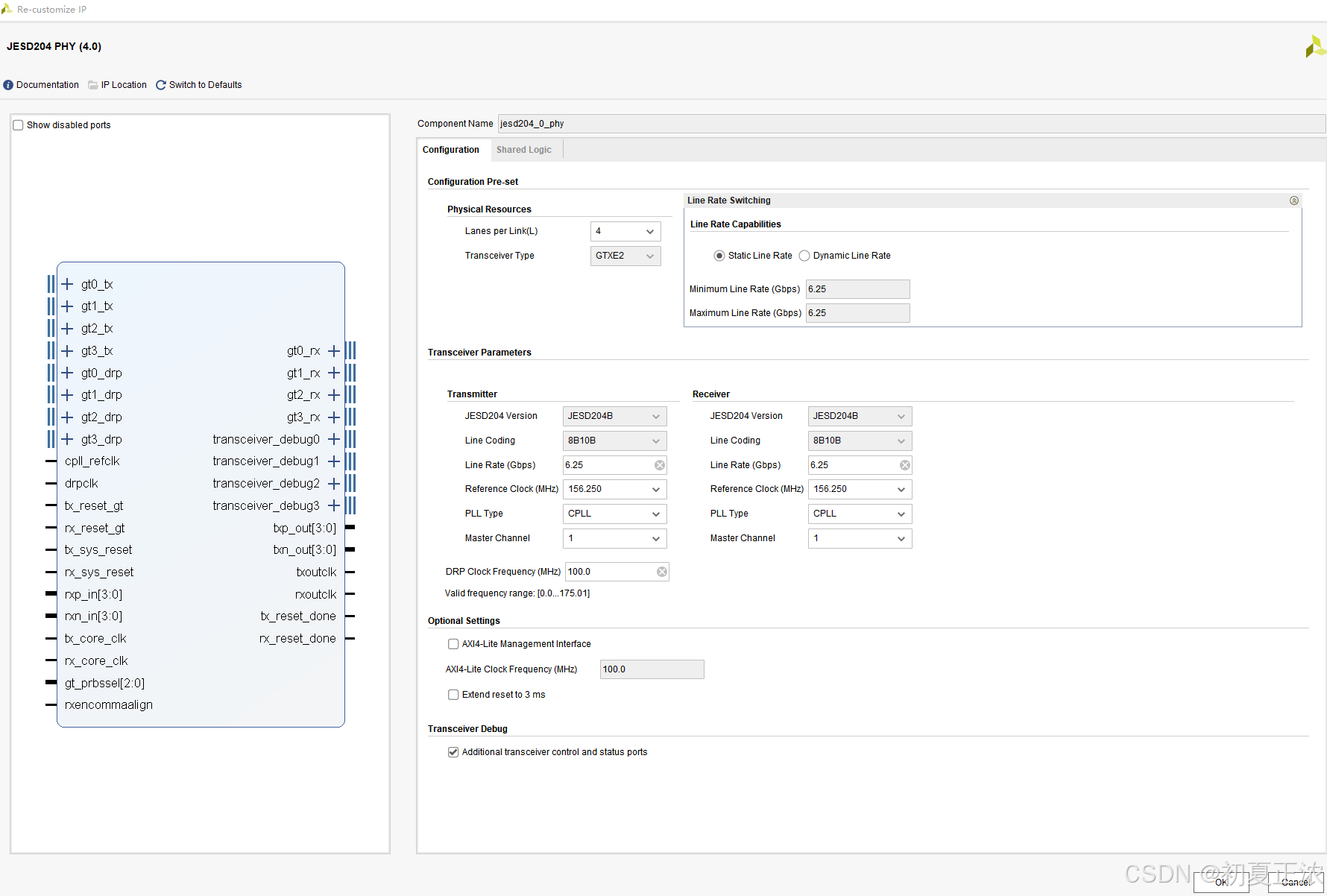

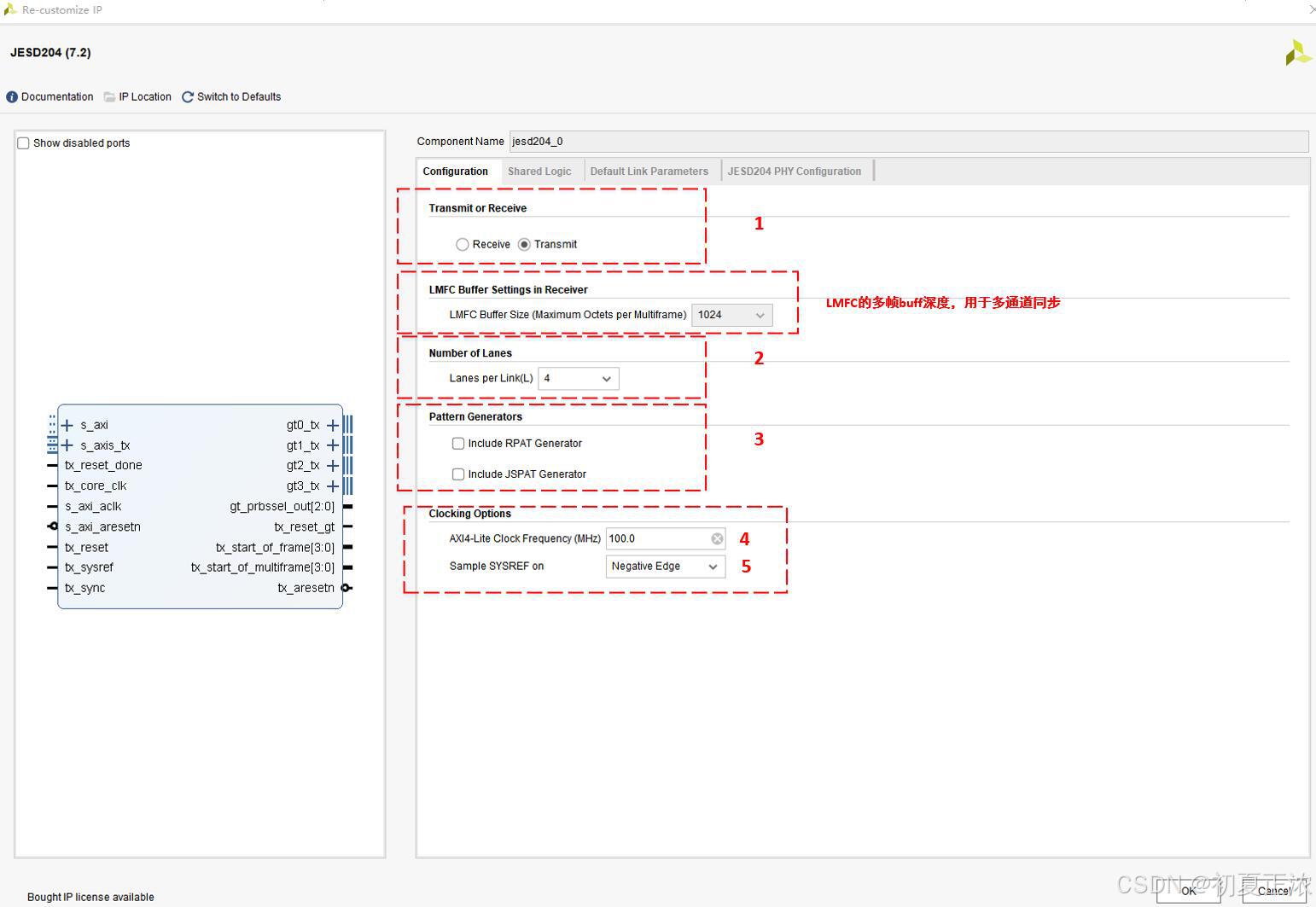

我们使用的XILINX IP是JESD204,这是包含了链路层的IP,一般搭配使用还需要带一个JESD204_PHY的IP 。

图 14 JESD204

图 15 JESD204_phy

我们这里主要介绍JESD204B这个ip的仿真,在UltraScale系列中没有这个IP,用JESD204C也是可以的。这个IP的设置比较简单:

1:发送端还是接收端设置

2:通道数

3: Pattern Generators:经修改的随机模式连续序列(RPAT);

连续的加扰抖动模式序列 (JSPAT)

在《JEDEC STANDARD-Serial Interface for Data Converters》中规定,所有 TX 设备均应能传输下列测试序列:

• 一个连续的/K28.7/字符序列(低频模式,有助于确定上升和下降时间);

• 连续的/K28.5/字符序列(混频模式或码组同步);

• 重复发送初始通道对齐序列。如果发送器启用此测试模式,只要接收器发出同步请求,发送器就应启动码组同步。完成码组同步后,发送器应重复 发送 ILAS。如果发送器进入测试模式时没有有效的码组同步请求,则发送器的行为应 与接收到的同步请求相同。进入测试模式时,发送器应连续发送至少四个/K28.5/符号,作为码组同步序列的一部分。单通道子类 0 ADC 设备不需要此测试序列。

4:AXI-LITE时钟(配置通道)

5:采样SYSREF的边沿类型

共享逻辑就没什么太多需要说的,直接跳过了。

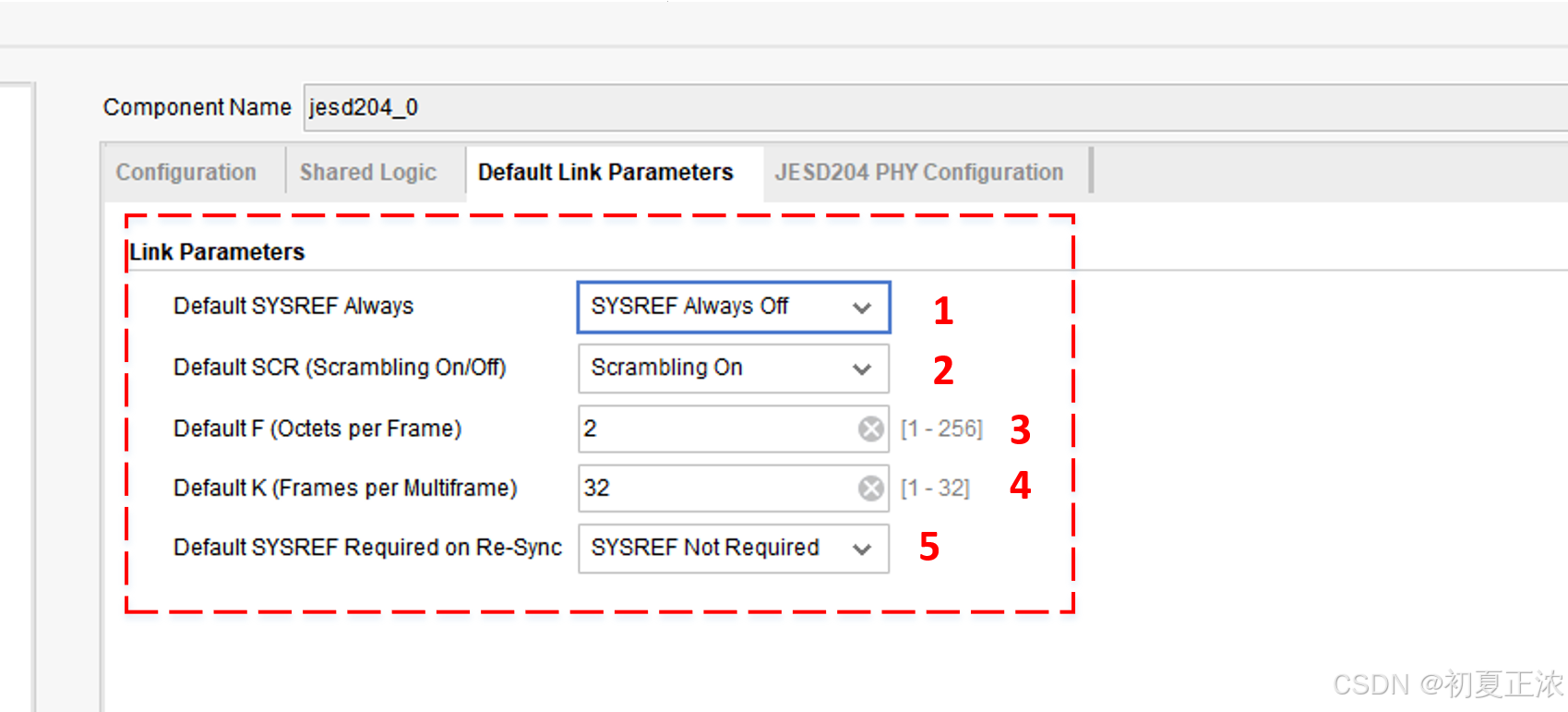

1:SYSREF的模式,是否是连续还是单次的

2:数据是否加扰

3: 每个帧里面有几个字节,也就是一个有效数据,用几个字节表示,该参数也是根据芯片手册来确定。

4:每个多帧里包含多少帧数,这个参数一般根据AD芯片来设置

5:重新同步时是否再次需要SYSREF

上面所有参数均设置等效配置寄存器中存储的默认(重置)值。如果通过 AXI4-Lite 配置总线写入寄存器,则会覆盖在IP生成期间设置的值。如果使用软件配置转换器帧参数,则无需在此处配置值。这些配置设置可用于在没有连接 AXI4-Lite 主机的情况下使用 IP。只有寄存器的一小部分可以通过这种方式配置。要访问所有配置设置并监控链路状态,应连接 AXI4-Lite 接口。

物理层的配置在另外一个IP上进行配置,在该IP上不参与配置。

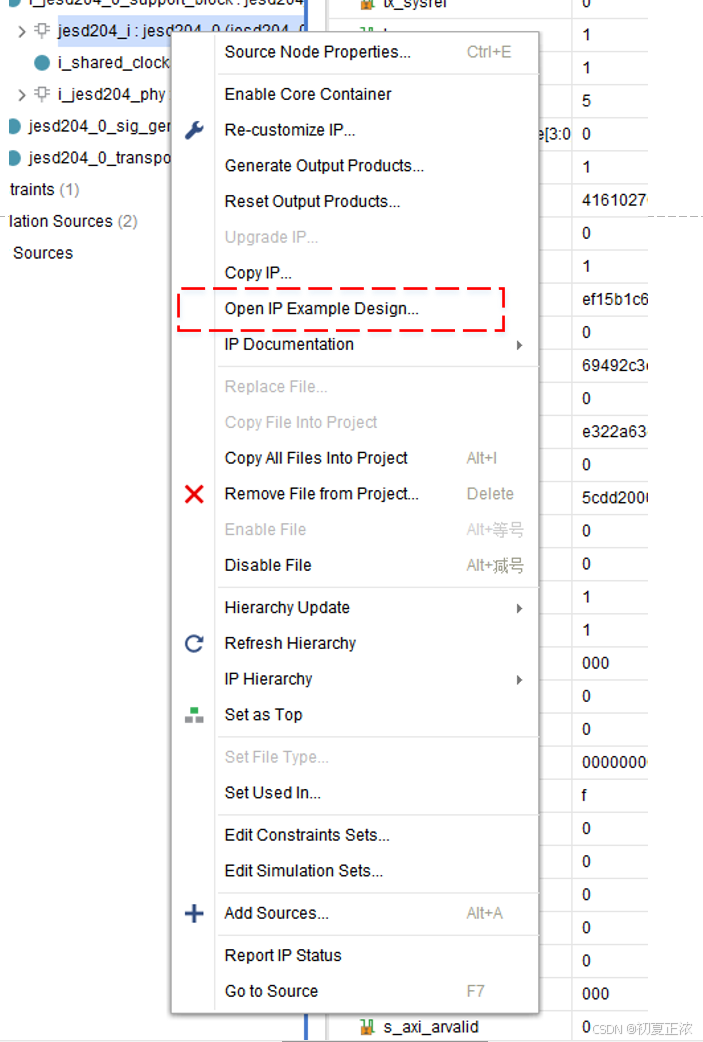

4.2 IP仿真

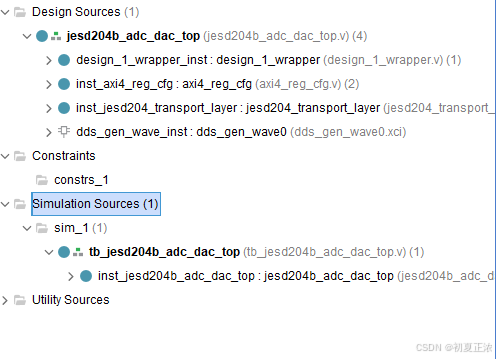

生成IP后,右键IP,点击打开Example design:即可进入示例工程,如下图:(多说一句~:其实如果小伙伴们看懂它的仿真思路了,可以自己尝试去写仿真,自己写的会更好懂一写,官方仿真是有丢丢的繁琐,没那么好懂,我们自己写的话,可以自己把收端发端都放进去,一起仿真,效果会更好,如果有小伙伴需要的话,后面我也会考虑跟大家分享分享,确实是不错的学习资料)

示例工程如下:

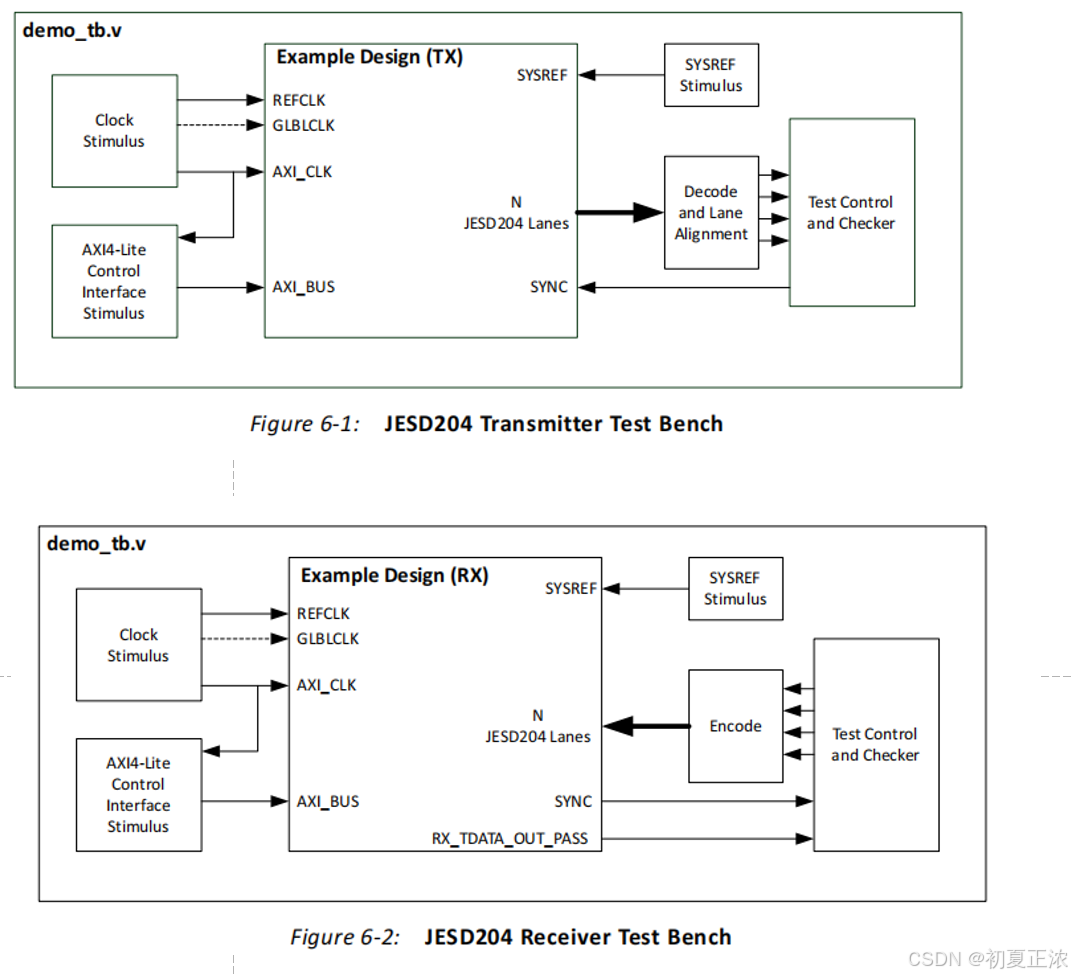

对于该IP来说,发端和收端的仿真工程不是一样的,整体框架一直,但是具体的数据流是有区别的:

接下来,重点说明发端的tb:

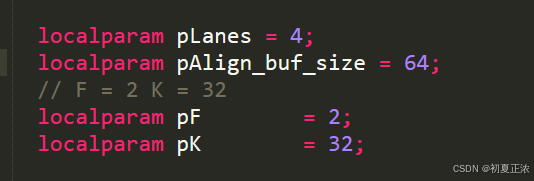

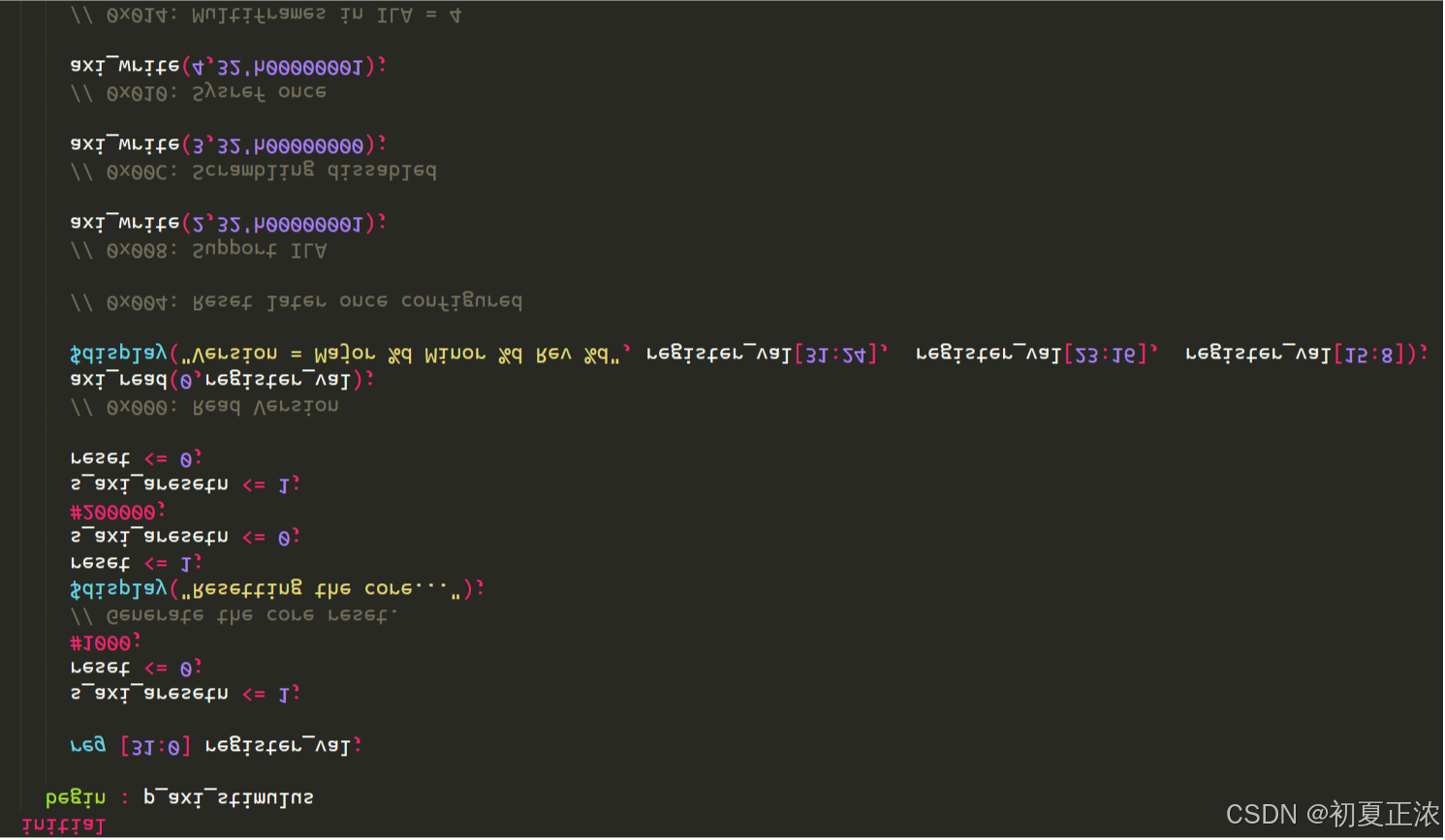

在demo_tb中:刚开始是对相关参数的初始化:

LANE数量和对齐buff参数的初始化:

ILAS阶段第二个多帧配置参数的初始化:(各字段含义见手册描述)

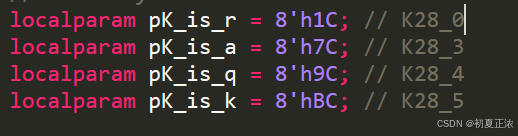

不同K码的定义:

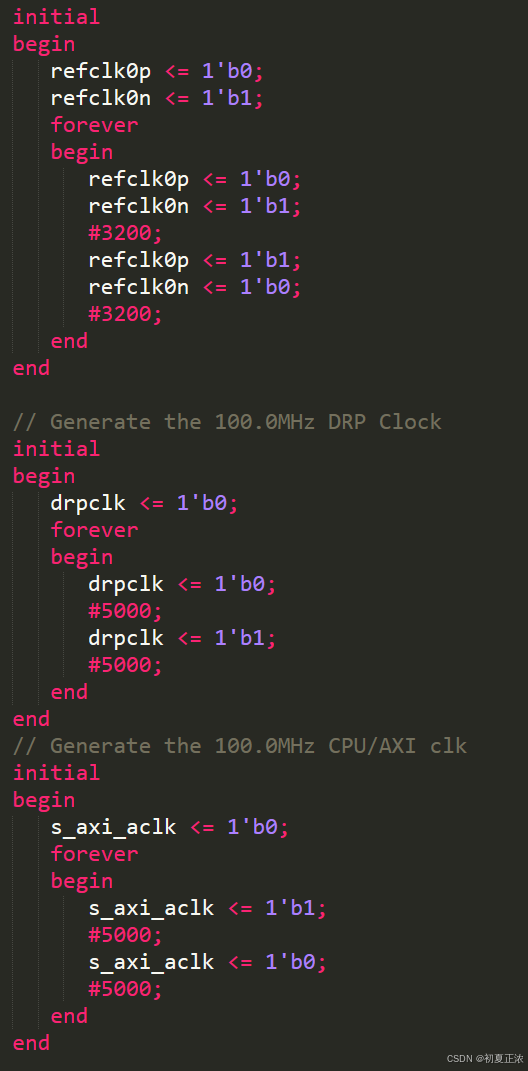

三种时钟的定义:GTXE2 BUF时钟,DRP时钟,AXI-LITE配置时钟

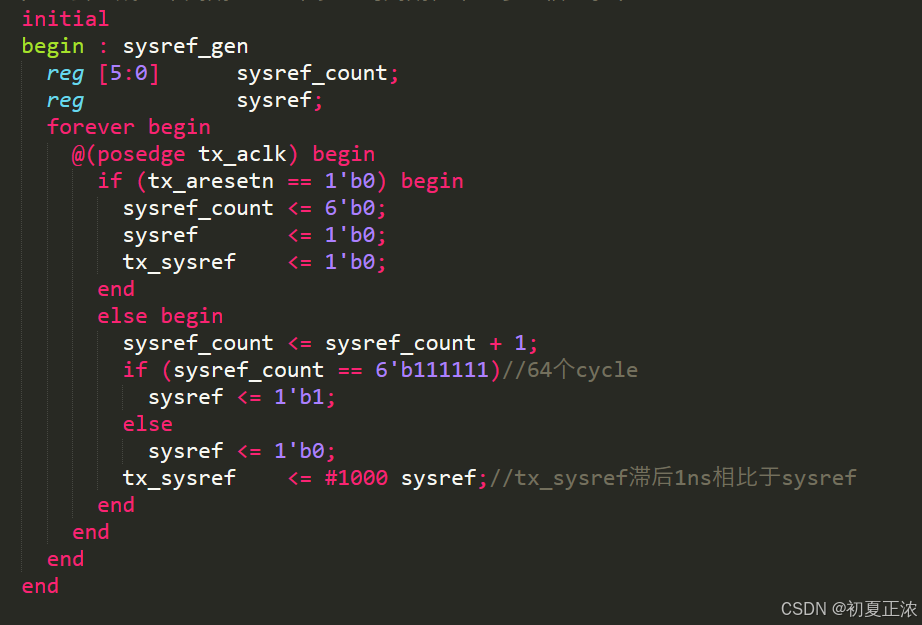

这是sysref的产生,比较简单不做太多阐述。

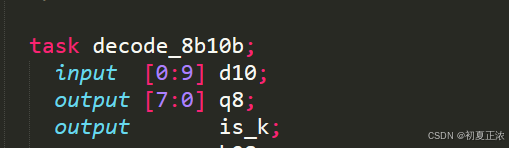

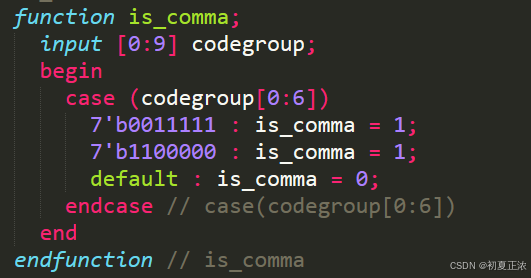

这个模块是对K码的8B/10B解码模块,对产生的数据进行解析,当为K码时,就会有is_k拉高,这在组码同步,通道对齐阶段都有使用

这是逗号对齐模块,在xilinx 高速串行收发器中,在数据之间会插入逗号也就是K码,监测到逗号就说明该帧为一个完整数据。

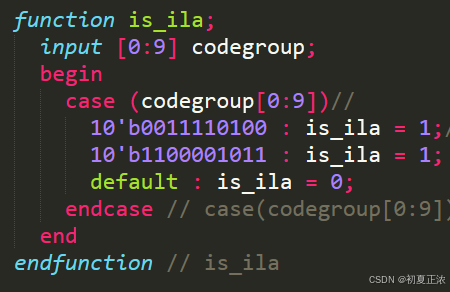

该模块为K28.0的检测模块,也就是在ILAS阶段需要检测四个多帧的开始即K28.0 /R/。

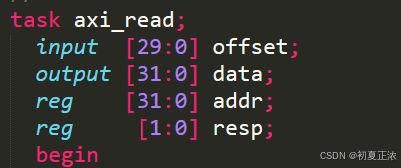

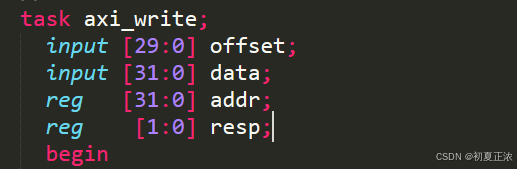

这是配置IP的模块,通过AXI-LITE总线去读写寄存器,即可以通过寄存器去配置IP的相关参数。

接下来对主要仿真代码进行解析:

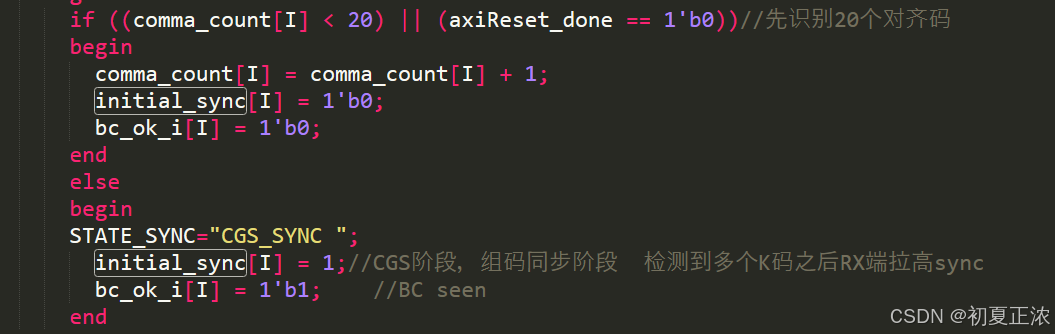

在组码同步阶段,仿真模块中写的是识别到20个COMMA之后,则开始进入ILAS,并且认为已经识别到K28.5。

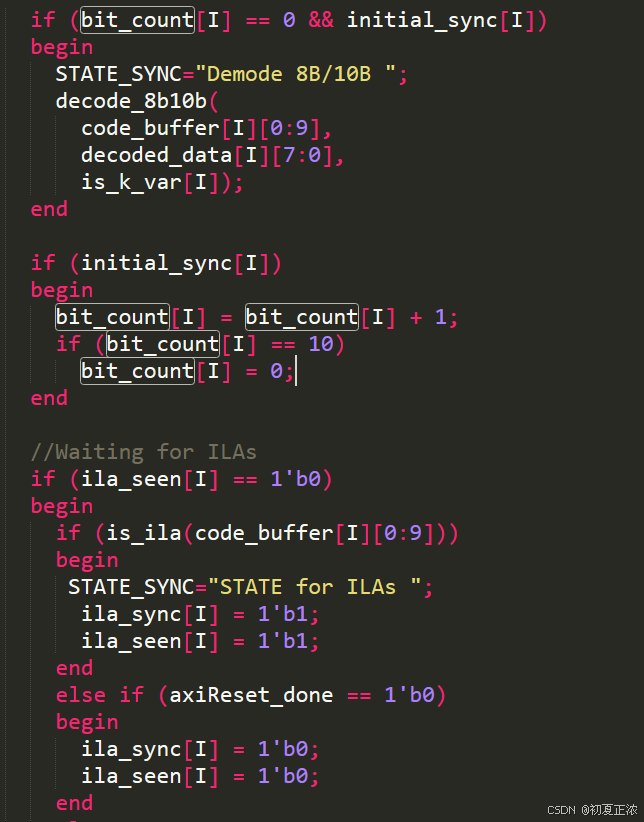

当CGS阶段结束后,开始进行ILAS阶段,这个时候首先bit_count作为滑动窗口,对每10个bit进行8B/10B解码,找出K28.0,也就是多帧阶段的帧起始字段/R/.后面就是对每个通道都做数据

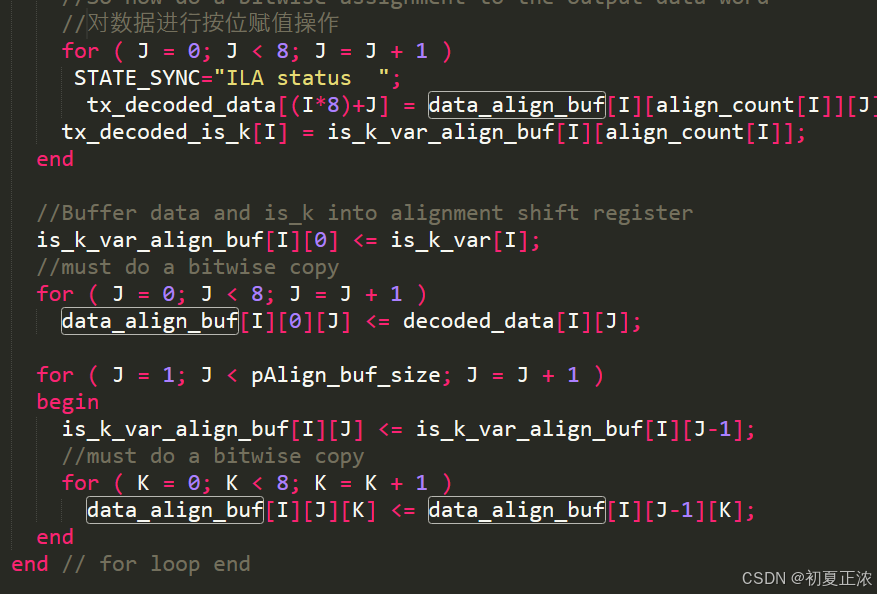

接下来就是多通道对齐,对齐的buf深度为64,每个通道按bit输入进BUF,其中I表示通道编号。

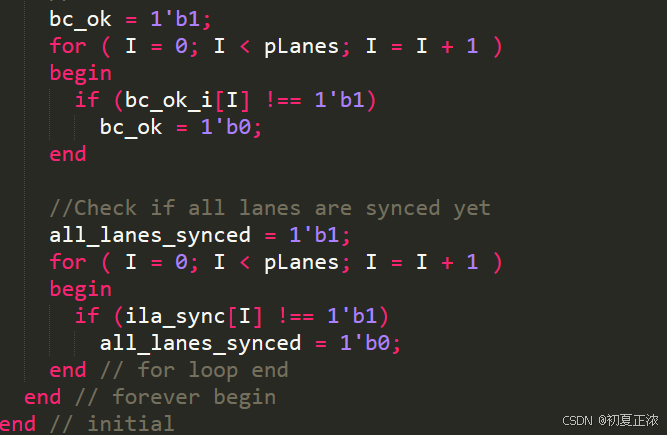

当所有通道对齐之后,链路正式建立。

其他的就是仿真状态监测,通过不同的状态进行打印,熟悉了上面流程状态监测就是比较简单的模块了。

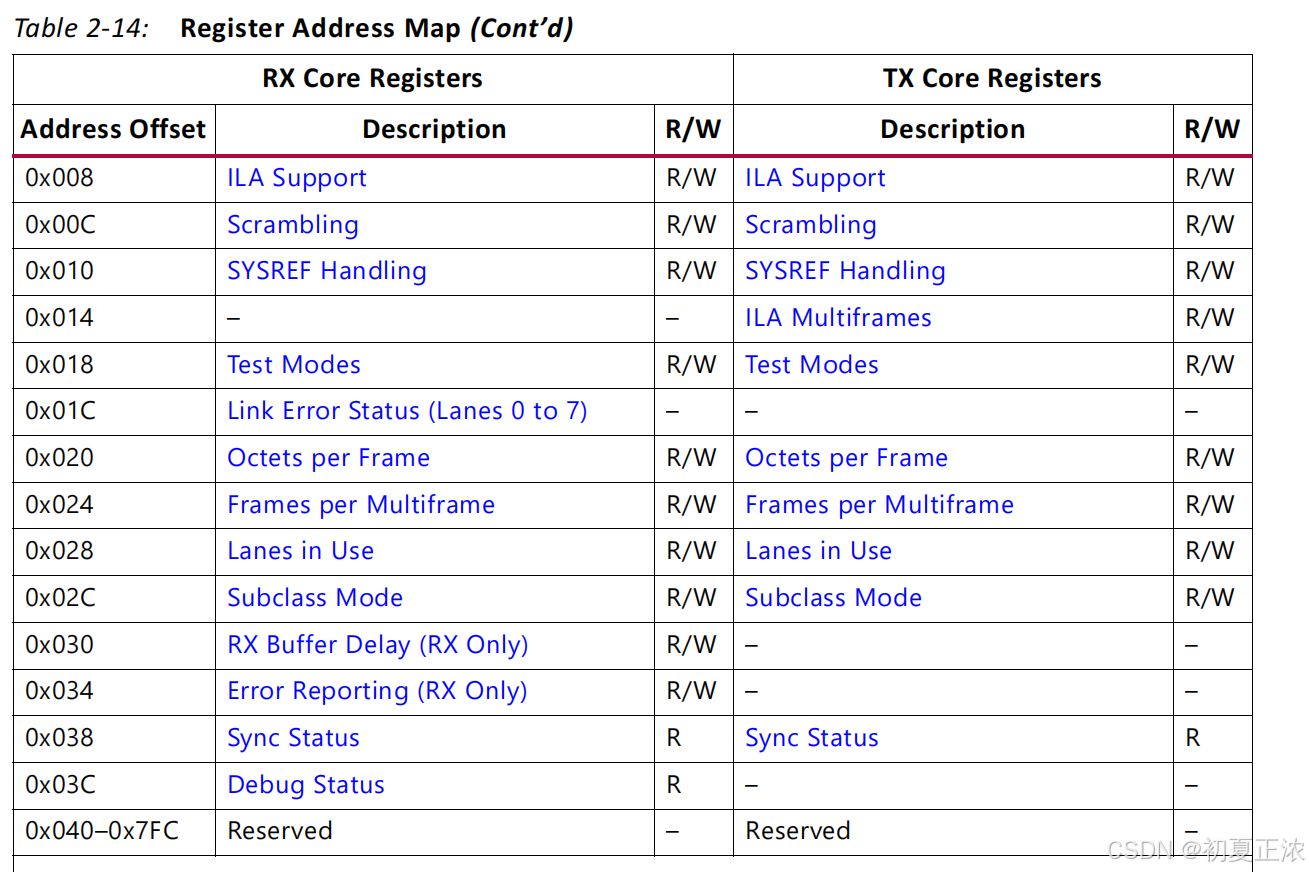

还有一点比较重要,就是寄存器配置模块,这里都是比较重要的寄存器,在我们实际项目中是使用的比较多的寄存器具体参数可以看PG066的寄存器空间,如果有不熟悉的,大家可以评论留言,后面看有没有必要对寄存器进行单独说明

图 16 寄存器空间

(好久没更新文章了,该露个面了,正好分享一下最近做JESD204B的一些小知识科普,文章比较长又写的比较匆忙,错误在所难免,望各位小伙伴不吝赐教)