如何expanded time来观察信号到来的先后顺序?(仿真工具使用技巧)【Modesim/Questasim】

如何使用delta cycle来观察信号到来的先后顺序?

-

- 一、写在前面

- 二、如何使用delta cycle来观察信号到来的先后顺序?

-

-

- 2.1 案例来源

- 2.2 正常对于前仿,组合逻辑无延时,信号统一在上升沿发生改变

- 2.3 点击以下的图标以将time expanded

- 2.4 我们可以发现信号实际的先后变化关系

-

- 三、 其他Modesim/Questasim使用技巧

一、写在前面

Modesim/Questasim是Mentor公司用来仿真VHDL/Verilog/Systemverilog的EDA工具,因其可以运行在Windows系统下,同时与各类FPGA的开发平台有较好的适配,所以是很多数字IC或FPGA初学者第一次接触到的仿真工具,但是简体中文互联网上对Modesim/Questasim的使用技巧的归类与整理不够详细,也不够准确,因此创作本前缀为【Modesim/Questasim】的系列文章,对此工具的使用技巧进行整理与归纳总结。

当然modesim/Questasim更多的是提供给FPGA/数字IC领域初学者的仿真工具,对于IC设计来说,真正工作环境使用到的更多的是VCS,也希望有志于从事数字IC领域工作的人员尽早地将环境转移到linux下的VCS上去进行熟悉

二、如何使用delta cycle来观察信号到来的先后顺序?

2.1 案例来源

源码和仿真文件来自【数字IC手撕代码】Verilog自动售卖饮料机|题目|原理|设计|仿真

这是一个有关状态机的设计文件,假如在输入端投币,那么输出端根据状态机的变化会吐出找零或硬币。

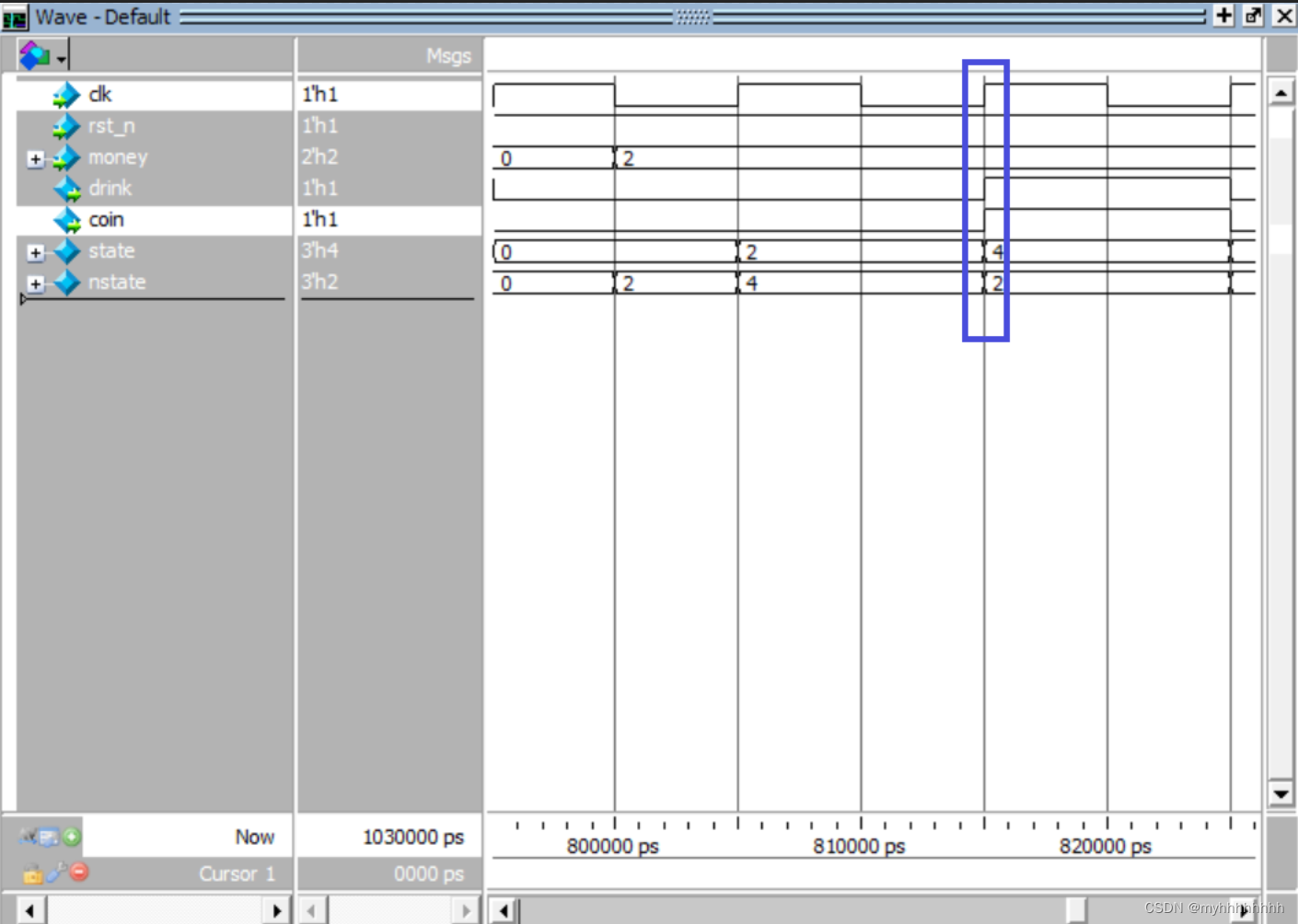

2.2 正常对于前仿,组合逻辑无延时,信号统一在上升沿发生改变

我们可以发现,不管信号的尺度多小,饮料信号、找零信号和状态机变化的信号都是在同一个上升沿发生改变,这与实际电路不符,也不利于我们debug和trace信号变化的信后顺序。

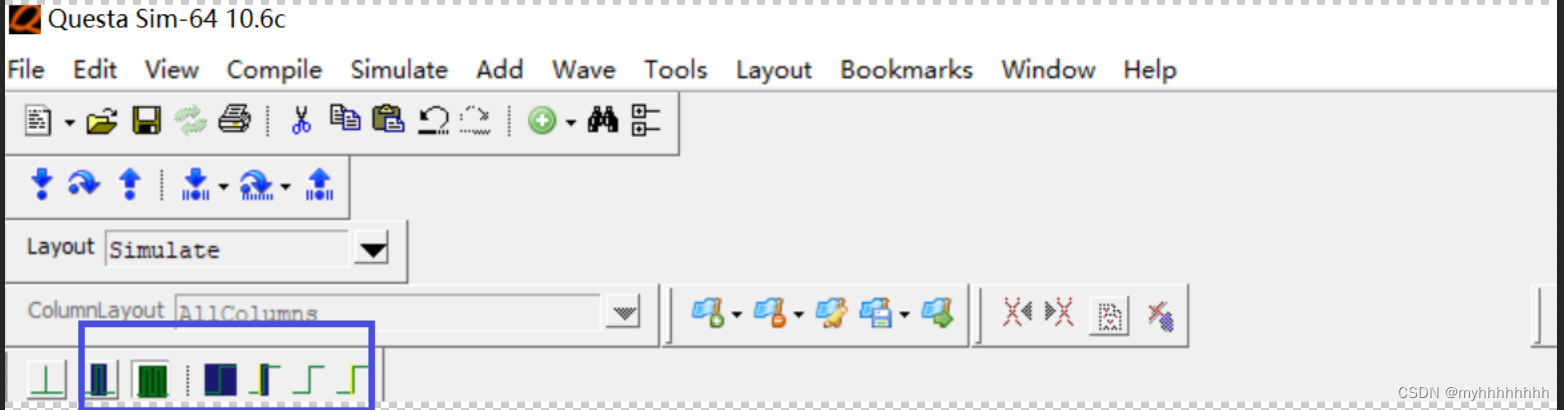

2.3 点击以下的图标以将time expanded

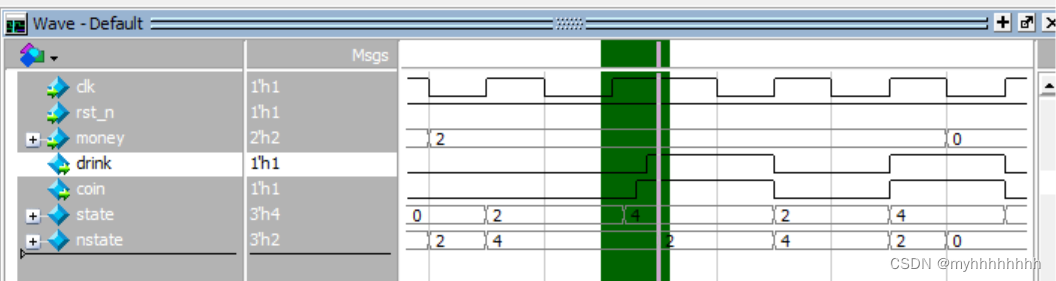

2.4 我们可以发现信号实际的先后变化关系

即clk是最先变化的,引起了state的变化,最终使money信号和drink信号发生改变的先后关系。

三、 其他Modesim/Questasim使用技巧

如何在仿真窗口查看信号频率

如何设置“tab”键缩进数量

如何去除仿真时的信号前缀

如何设置一个清爽的仿真窗口

如何使用delta cycle来观察相同边沿的先后顺序

如何使用Modesim查看状态机状态跳转

如何用命令行的形式进行仿真及do脚本的使用