rk3288 mipi 调试步骤

https://blog.csdn.net/dearsq/article/details/52354593(参考:CSDN博客)

https://www.2cto.com/kf/201708/670726.html(参考:CSDN博客)

https://www.cnblogs.com/lialong1st/p/9952077.html(参考:CSDN博客)

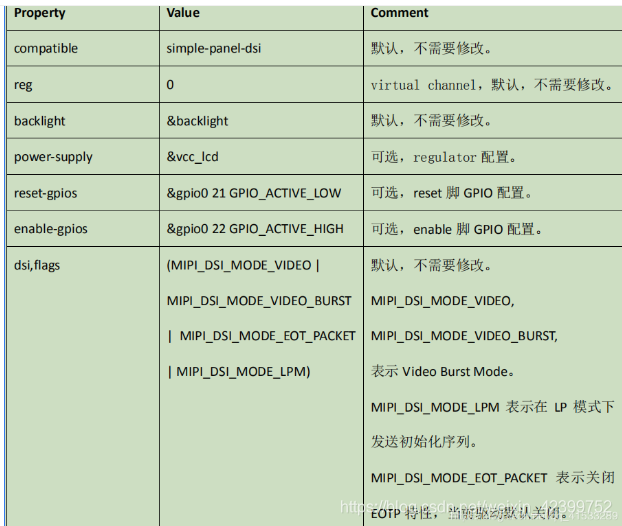

// lcd-xxx-mipi.dtsi 中的 屏参

disp_timings: display-timings { native-mode = ; compatible = "rockchip,display-timings"; timing0: timing0 { screen-type = ; //单mipi SCREEN_MIPI 双mipi SCREEN_DUAL_MIPI lvds-format = ; //不用配置 out-face = ;//屏的接线格式 //配置颜色,可为OUT_P888(24位)、OUT_P666(18位)或者OUT_P565(16位) clock-frequency = ; //dclk频率,看规格书,或者 H×V×fps hactive = ; //水平有效像素 vactive = ; //垂直有效像素 hback-porch = ; //水平同步信号 hfront-porch = ; //水平同步信号 vback-porch = ; vfront-porch = ; hsync-len = ; //水平同步信号 vsync-len = ; hsync-active = ; //hync 极性控制 置 1 反转极性 vsync-active = ; de-active = ; //DEN 极性控制 pixelclk-active = ; //dclk 极性控制 swap-rb = ;//设 1 反转颜色 swap-rg = ; swap-gb = ;clock-frequency:

即DCLK(dotc clock), PCLK(pixel clock).

clock-frequency = (h_active + hfp + hbp + h_sync) * (v_active + vfp + vbp + v_sync) * fps

厂商给的参考值是58.2MHz, 那么fps就是:

fps = 58200000 / (480 + 160 + 160 +24) * (1280 + 12 + 10 + 2) = 54Hz

这里需要说明的一点是,Android 的最高刷新频率为 60fps,所以我们最好保证

LCDC 的刷新频率也为 60fps,根据文档第一部分介绍的 LCDC 的刷新频率计算公式可以知道,LCDC 的刷新频率和 DCLK 成正比,和水平方向与垂直方向参数之和的乘积成反比。根据屏幕的 datasheet 我们可以看出,对于一款屏幕 H_VD/V_VD 对应屏幕的分辨率,值是固定的不能修改,BP、FP、PW 的值都有一个最大值和最小值的取值范围,所以当我们的 DCLK 分配不到想要的频率的时候,可以适当的调整 BP、FP、PW是的 LCDC的刷新率尽可能的接近 60FPS。

LCD之mipi DSI接口驱动调试流程

https://blog.csdn.net/liwei16611/article/details/68146912

一、屏的基本参数说明

水平分辨率:hactive 垂直分辨率:vactive

水平前尖:hfront-porch(HFP) 垂直前尖:vfront-porch(VFP)

水平后尖:hback-porch(HBP) 垂直后尖:vback-porch(VBP)

水平消隐信号:hsync-len(HS) 垂直消隐信号:vsync-len(VS)

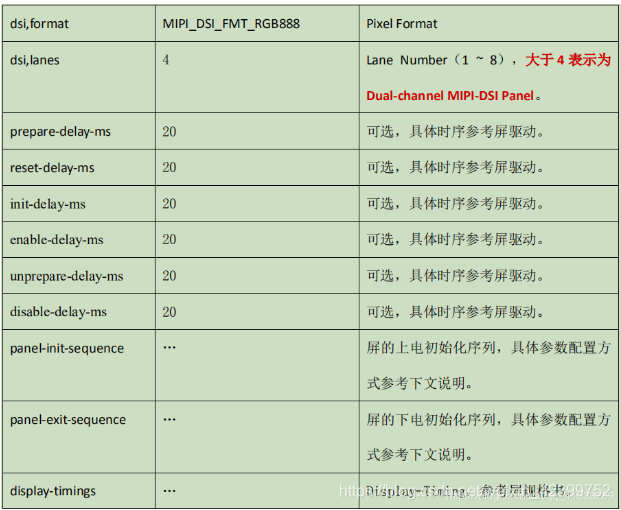

1.lane-rate= clk(时钟频率) * RGB(3) * BIT(6或8) / lane_num ,lane_num表示差分时钟通道数,具体数值要根据实际情况修改。注:以上公式的值计算出来后,rk3288里面需要*1.25,因为配置会比实际输出会低一点

2…clock-frequency=(水平分辨率+HS+HBP+HFP)(垂直分辨率+VS+VBP=VFP)*fps(帧频率);

3.dsi,format表示RGB三原色用多少位表示,如六位:dsi.format=;八位:dsi.format=,lane-rate计算公式中的RGB与BIT值根据format参数得出;

二、通过时序图分析水平和垂直各个参数:

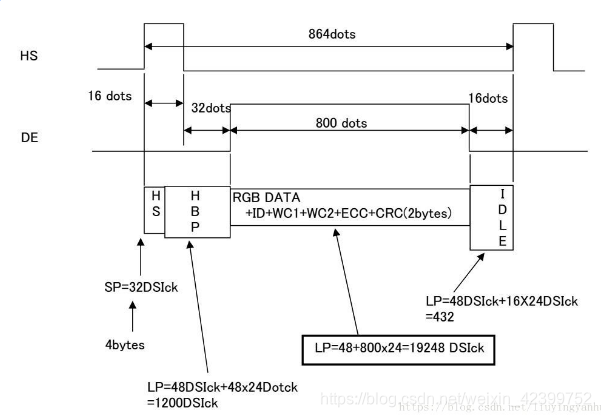

下图是行同步信号:HS 里面的864=16+32+800+16,我们可以看到在DE 为高电平时,HS 为低电平的时候就是有效的数据,即屏的水平像素为800。在HS 为高电平时,DE 是低电平,意思就是这个时候不需要显示数据,需要去消隐,就是hsync。在往后的32 个像素,就是屏真正的信号出来前的无效信号长度,因为如果我们直接出来,很可能会丢数据和出现杂波,多这32 个像素是为了防止这种情况,就是上面提到的HBP 参数,最后的16 像素,也是同理。所以一个完整的行信号是=hsync+hbp+hactive+hfp。

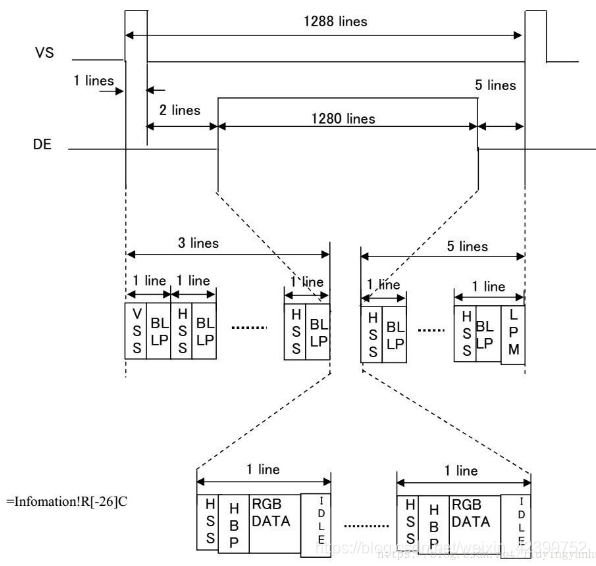

下图是场同步信号,其他的和行同步信号是一致,只不过这个里面在DE 为高电平时里面就是1280 个行同步信号。可能有点绕口,但是我们一定要理解,以这个800x1280 的屏为例,就是说屏幕上有800x1280 的dot,如果一个点一个点的在屏幕上显示,当水平显示800 个dot 后,就会有一个行同步信号,也就是800x1,然后转到第二行继续显示800 个然后出一个行同步信号,就是800x2,以此类推一直到800x1280,这个时候就会出一个场信号,告诉屏我一帧的画面已经画完了,现在要开始下一帧了。

三、基本步骤

1.先查看屏的规格说明书,确认屏的类型以及屏的具体型号,这很重要,确定之后,才能确定需要修改那个dts文件;

2.把全部代码编译一遍,使用AndroidTools工具将所有img文件下载到板子上,看能否发现ADB设备,能发现ADB设备表示代码可以跑起来;

4.修改dts文件,在autobuild.sh文件中修改编译规则,根据修改的dts文件编译相应的镜像文件

屏参先按规格说明书给出的标准参数填,如下图所示:

如果标准参数的点不亮,再尝试最大和最小,如果都点不亮,则需要慢慢修改参数调试;

CLK如果不准确 可以按照20MHZ增大或减小的逻辑调,如原来是150MHZ,可减小或增大20MHXZ,相应的,lane-rate值也要根据公式做出相应的改变,注意,如果一直都点不亮,可查看屏幕排线有没有接好,或者可能是硬件部分有问题。

初始化代码解析(MIPI必须有初始化代码才能点亮,这个有原厂提供):

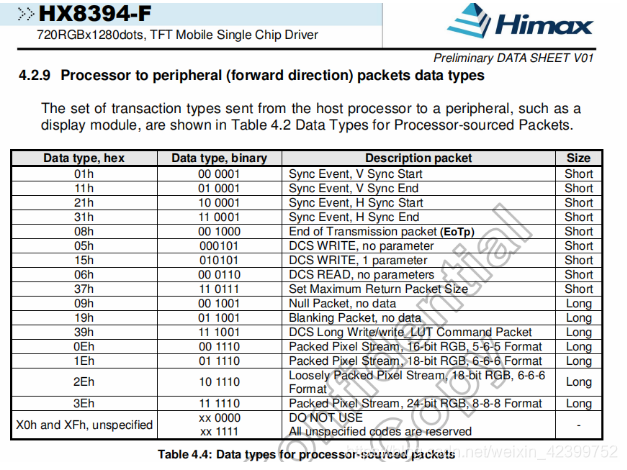

panel-init-sequence = [ 39 00 06 f0 55 aa 52 08 00 .................................................. 05 96 01 29 ];说明:前 3 个字节(16 进制),分别代表 Data Type,Delay,Payload Length。

从第四个字节开始的数据代表长度为 Length 的实际有效 Payload。

第一条命令的解析如下:39 00 06 f0 55 aa 52 08 00

Data Type:0x39 (DCS Long Write)

Delay:0x00 (0 ms)

Payload Length:0x06 (4 Bytes)

Payload:f0 55 aa 52 08 00

最后一条命令的解析如下:

05 96 01 29

Data Type:0x05 (DCS Short Write, no parameters)

Delay:0x96 (150 ms)

Payload Length:0x01 (1 Bytes)

Payload:0x29

命令的前面三个字节分别表示命令类型、延时和命令净荷长度。从第四个字节开始表示命令的有效 payload。这个字节数需要与第三个字节一致。

命令的类型有三种 : 0x05/0x15/0x39.

其中0x05命令类型是带1个参数,如:

05 96 01 11

0x15命令类型是带2个参数,如:

15 00 02 36 0A

0x39命令类型是带多个参数,即大于两个参数,如:

39 00 0A D4 00 37 52 17 01 04 70 45 05

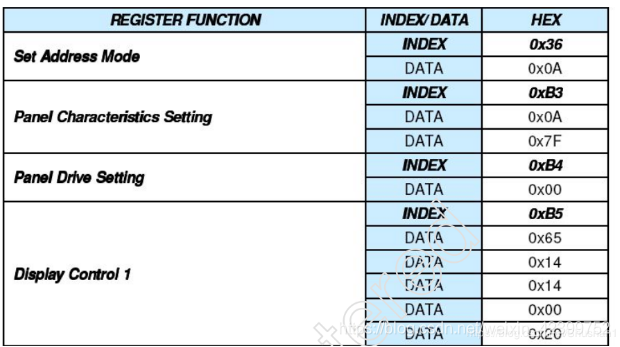

其中,这些命令就需要根据屏的数据手册去寻找,比如我的屏的数据手册中的命令如图:

与我这几个命令相符

15 00 02 36 0A

39 00 03 B3 0A 7F

15 00 02 B4 00

39 00 06 B5 4C 14 14 00 20

这些参数配置完了之后编译烧录屏就能显示了.

遇到问题:

1.背光不能亮

检查硬件电路,或者enable脚是否配置正确.

2.可以显示,但是屏幕花屏

调节rockchip,lane-rate以及timings参数.

3.水平左边有黑边

调节前肩后肩就可以

4.字体,图片有抖屏的现象

解决办法有两种办法

1>屏蔽rockchip,lane-rate

&dsi0 {

status = “okay”;

//rockchip,lane-rate = ;

pinctrl-names = “default”;

pinctrl-0 = , ;

因为rk doc文档有说:

Optional properties

- clocks, clock-names:

phandle to the SNPS-PHY config clock, name should be “phy_cfg”.

phandle to the SNPS-PHY PLL reference clock, name should be “ref”.

phandle to the Non-SNPS PHY high speed clock, name should be “hs_clk”.

phandle to the h2p bridge clock, name should be “h2p”. - phys: phandle to Non-SNPS PHY node

- phy-names: the string “mipi_dphy” when is found in a node, along with “phys”

attribute, provides phandle to MIPI PHY node - rockchip,dual-channel: for dual-channel panel, if not, don’t configure

- rockchip,lane-rate: manually configure lane-rate, not necessary.

文档路径:

kernel\Documentation\devicetree\bindings\display\rockchip\dw_mipi_dsi_rockchip.txt

2>根据公式计算大概值:

lane_rate = clock-frequency* RGB(3) * BIT(6或8) / 4;

一般来说在3288里面需要*1.25,因为配置会比实际输出会低一点

RK3326\kernel\Documentation\devicetree\bindings\display\rockchip路径下有帮助文档,介绍dts

原文链接:https://blog.csdn.net/Shushan1/article/details/87858434