Vivado 原语STARTUPE3的使用

1、STARTUPE3 引脚描述

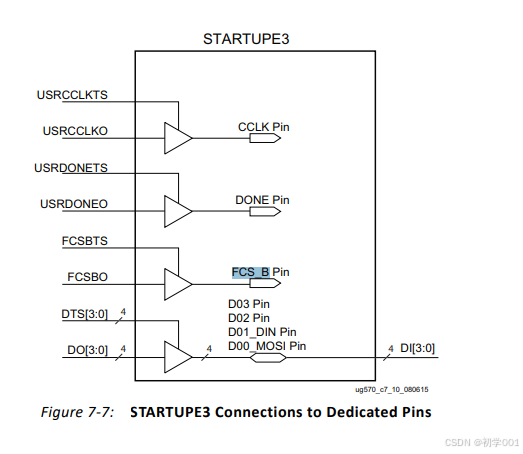

描述 STARTUPE3 相关管脚。三态控件默认1 为禁用输出,0为是能输出,KEYCLEARB 默认为 1,其他输入默认为 0。

原文参考xilinx官方手册UG570第116页

2、FPGA逻辑端控制

STARTUPE3 组件的一个关键特性是将用户设计连接到一些专用的 configuration pins。这些 pins 可用于作为用户设计的一部分访问 configuration flash。STARTUPE3 表示与外部引脚的连接,因此 STARTUPE3 的输入是与输出引脚或双向引脚的连接,而 STARTUPE3 的输出是返回用户设计的双向引脚输入。

特别需要注意DO、DI管脚在输入输出方向DTS信号控制使能,逻辑端sck、cs、mosi信号为输出类型,相应使能控制信号应该置‘0’;对于miso为输入信号,控制信号DTS相应为应该置为‘1’。下面是我使用xcku035系列fpga芯片验证spi_x1使用原语端口例化部分可以参考:

wire [1 :0] w_operation_type ; wire [31:0] w_operation_addr ; wire [8 :0] w_operation_num; wire w_operation_valid ; wire w_operation_ready ; wire [7 :0] w_write_data ; wire w_write_sop ; wire w_write_eop ; wire w_write_valid ; wire [7 :0] w_read_data ; wire w_read_sop ; wire w_read_eop ; wire w_read_valid ; wire o_spi_clk ; wire o_spi_cs ; wire o_spi_mosi ; wire i_spi_miso ; flash_drive flash_drive_u0( .i_clk (i_clk ), .i_rst (i_rst ), .i_operation_type (w_operation_type ), //操作类型 .i_operation_addr (w_operation_addr ), //操作地址 .i_operation_num (w_operation_num ), //限制用户每次最多写256字节 .i_operation_valid (w_operation_valid ), //操作握手有效 .o_operation_ready (w_operation_ready ), //操作握手准备 .i_write_data (w_write_data ), //写数据 .i_write_sop(w_write_sop ), //写数据-开始信号 .i_write_eop(w_write_eop ), //写数据-结束信号 .i_write_valid (w_write_valid ), //写数据-有效信号 .o_read_data(w_read_data ), //读数据 .o_read_sop (w_read_sop ), //读数据-开始信号 .o_read_eop (w_read_eop ), //读数据-结束信号 .o_read_valid (w_read_valid ), //读数据-有效信号 .o_spi_clk (o_spi_clk ), //spi的clk .o_spi_cs (o_spi_cs ), //spi的片选 .o_spi_mosi (o_spi_mosi ), //spi的主机输出 .i_spi_miso (i_spi_miso ) //spi的从机输出); STARTUPE3 #( .PROG_USR (\"FALSE\" ), .SIM_CCLK_FREQ (0.0 ) // Set the Configuration Clock Frequency (ns) for simulation ) STARTUPE3_inst ( .CFGCLK ( ), // 1-bit output: Configuration main clock output .CFGMCLK ( ), // 1-bit output: Configuration internal oscillator clock output .DI ({1\'b0,1\'b0,i_spi_miso,1\'b0} ), // 4-bit output: Allow receiving on the D input pin .EOS ( ), // 1-bit output: Active-High output signal indicating the End Of Startup .PREQ ( ), // 1-bit output: PROGRAM request to fabric output .DO ({1\'b1,1\'b1,1\'b0,o_spi_mosi} ), // 4-bit input: Allows control of the D pin output .DTS (4\'b0010 ), // 4-bit input: Allows tristate of the D pin .FCSBO (o_spi_cs ), // 1-bit input: Controls the FCS_B pin for flash access .FCSBTS (0 ), // 1-bit input: Tristate the FCS_B pin .GSR (0 ), // 1-bit input: Global Set/Reset input (GSR cannot be used for the port) .GTS (0 ), // 1-bit input: Global 3-state input (GTS cannot be used for the port name) .KEYCLEARB (0 ), // 1-bit input: Clear AES Decrypter Key input from Battery-Backed RAM (BBRAM) .PACK (0 ), // 1-bit input: PROGRAM acknowledge input .USRCCLKO (o_spi_clk ), // 1-bit input: User CCLK input .USRCCLKTS (0 ), // 1-bit input: User CCLK 3-state enable input .USRDONEO (1 ), // 1-bit input: User DONE pin output control .USRDONETS (1 ) // 1-bit input: User DONE 3-state enable output );