STM32:FSMC和SRAM(XM8A51216V33A)时序分析

概述

时序图要区分哪些是要求,哪些是能力,即对外界信号的时序要求和自身输出能力FSMC中哪些是固定参数,即电路特性参数或者说输出误差参数(数据手册里的时序图参数);哪些是可调参数,即允许用户配置的参数(用户手册的ADDSET和DATASET)sram的控制信号cs、oe、we,写和读是一段时间而非一个时刻,oe低电平期间都是在读,we低电平期间都是在写

cs# 信号阶段锁存地址 → 激活芯片 → 启动读/写周期oe# 信号阶段we#时序阶段锁存地址 → 选中单元 → 激活写入驱动器t_wp)锁定数据线数据 → 释放总线- FSMC读sram时:

-

地址建立时间、地址保持时间、数据建立时间、数据保持时间实际上都有所体现,只不过是地址保持时间(FSMC提供)和数据保持时间(sram提供)是不可调整的或者要求较低的,但实际使用中还是要验算一下的。 因此,对FSMC的配置主要体现在地址建立时间和数据建立时间 -

sram对地址建立时间参数(输入给

sram的地址有效时刻要比输入的oe下降沿至少早多久)无要求。————>因此FSMC可以设置地址建立时间参数为ADDSET=0(FSMC控制输出的oe下降沿在输出地址有效后多久才输出) -

sram对数据建立时间参数(输入给

sram的oe上升沿之前要保证oe低电平至少持续一定的时间,保证sram有足够的时间取出内部数据)有要求:从ce有效后至少等到10ns,也就是oe低电平至少持续10ns。————>因此,FSMC可以设置数据建立时间参数为DATASET=2(表示2HCLK=12ns)(FSMC控制从oe下降沿让sram开始取出内部数据到oe上升沿FSMC读取数据线数据,这段oe低电平时间就是留给sram的数据建立时间) -

sram对地址保持时间参数有要求:这个要求实际上体现在

sram参数tace和taa(给到地址后sram内部电路能在10ns以内把数据送出来,其实也意味着这10ns时间内地址线要保持不能变化)。————>因此,FSMC在输出ce、oe低电平时地址线不会变化,因此只需设置足够久的oe低电平时间即可,也就是数据建立时间,所以说是通过设置数据建立时间间接满足了地址保持时间 -

FSMC对数据保持时间参数有要求(电路特性,无法调整):

th(Data_NOE):Data hold time after FSMC_NOE high 即在NOE上升沿(FSMC采集数据线)之后,数据线还至少要保持多久的时间即数据保持时间,才能保证FSMC能正确采集到数据线,至少保持0ns。————>因此,sram输出数据时的数据保持实现参数也是电路特性,不可调整,只能验算看两者是否匹配:thzoe:oe上升沿到数据线变成高阻(数据变失效、数据IO电路关闭)最多需要2.3ns,也就是数据保持时间:读结束后,数据线还会维持最多2.3ns。而FSMC需要的是至少0ns,验算下来,是能够满足FSMC的要求的 -

验算其他参数:

sram读时序中要求trc即读周期时间最小是10ns即ce低电平时间要大于10ns。————>因此,FSMC输出给sram的地址有效的持续时间、ce低电平持续时间都要大于10ns,而FSMC输出的ce低电平持续时间=(ADDSET+DATASET)*HCLK = (0+2)*6ns = 12ns,满足了trc>10ns的要求

-

- FSMC写sram时:

- 地址建立时间是

tsa(地址有效到we上升沿的时间)还是taw(地址有效到we下降沿的时间) ?- 猜测:

(1)应该是tsa。写操作时,应该是在we下降沿时sram就锁存地址并定位到sram内部存储地址了吧,并且也是在we下降沿,FSMC开始着手往数据线上放数据了吧;we低电平期间则是sram在获取数据线并将其解析和搬运到sram内部(和读操作时sram将内部数据往外搬运到数据线上,刚好是相反操作,是需要一定的时间的即数据建立时间);we上升沿则是让sram执行往目标地址里写入数据的操作。 - 另一种猜测

(2)应该是taw。sram只在we上升沿才同时锁存地址和数据线,在we下降沿并没有什么操作。因此地址建立时间指的是地址有效到we上升沿这段时间 —— 但这样的话,和FSMC写时序里的ADDSET表示的时间段对不上。 - 以第一种说法为准

- 猜测:

- sram的能力/要求,地址建立时间:

sram对外部输入的地址有效到外部输入的we下降沿要求的时间间隔(地址建立时间)是tsa>=0ns,对外部输入的地址到外部输入的we上升沿要求的时间间隔是taw>6.4ns,对外部输入的we低电平持续的时间长度要求是tpwe>=0.7ns - 对

FSMC的要求:FSMC输出有效地址和cs下降沿给sram后,可以立即输出we下降沿,但输出的we低电平持续时间至少是6.4ns,即至少6.4ns之后才能对外输出we上升沿。 - FSMC的能力,地址建立时间:

设置ADDSET=0可使得cs下降沿和we下降沿同时输出; - FSMC的能力,数据建立时间:

设置DATASET=2,可以使得we低电平持续时间为2个HCLK=12ns - sram的能力/要求,数据建立时间:在收到外部输入的

we上升沿之前,需要提前收到外部输入的数据线数据,需要提前tsd>0ns时间收到。字节使能信号则提前tbw>0.8ns收到下降沿。 - 对

FSMC的要求:根据这个tsd>0ns条件,FSMC输出数据到数据线后可以立即输出we上升沿给sram,让sram进行数据写入 - FSMC的能力,数据建立时间:

设置DATASET=0,会使得输出的we低电平时间为0,不符合tpwe>=0.7ns的要求,因此DATASET的值需要大于0才行,保持为DATASET=2 - sram的能力/要求,数据保持时间:在收到外部输入的

we上升沿之后,外部输入的数据线还需要保持thd>=2ns的时间,以保证sram能正确写入数据 - 对

FSMC的要求:FSMC需要在输出we上升沿之后,还要维持输出数据线至少2ns - FSMC的能力,数据保持时间:没有相关参数设置数据保持时间,而是硬件上固定设计为

1个HCLK=6ns的保持时间,能够满足sram对数据保持时间的要求 - sram的能力/要求,地址保持时间:在收到外部输入的

we上升沿之后,外部输入的地址线还需要保持thd>=3.1ns的时间,以保证sram能正确写入数据 - 对

FSMC的要求:FSMC需要在输出we上升沿之后,还要维持输出地址线至少3.1ns - FSMC的能力,地址保持时间:和数据保持时间相同,没有相关参数设置数据保持时间,而是硬件上固定设计为

1个HCLK=6ns的保持时间,能够满足sram对地址保持时间的要求 - 验算其他参数:

sram要求写周期twc>10ns——>FSMC设置的参数为ADDSET=0,DATASET=2,输出cs低电平时间=(ADDSET+DADASET+1)HCLK=3HCLK=18ns,满足twc>10ns的要求

- 地址建立时间是

一、地址译码和控制信号

1.1 信号含义

(1)地址译码的触发条件:一旦地址线输入的信号稳定,地址译码器会立即将其转换为对应的行和列选择信号,定位目标存储单元。这一过程是组合逻辑操作,与CS/OE/WE无关。并且地址译码电路本身是实时译码的,不包含锁存功能,其输出随输入地址动态变化。

(2)片选信号(CS)的作用:若CS未使能,地址译码结果将被忽略,防止无效访问;其他功能电路也都无法工作,处于无效状态。

(3)输出使能OE的作用:输出使能信号开启数据总线输出,Data电路根据控制信号(如OE和WE)切换数据总线的方向,实现数据的读/写隔离,防止总线冲突,OE为低表示读取,此时数据IO电路变成输出即向外部输出数据,OE为高则使得数据IO电路变成输入即接收外部的数据。

(4)写使能WE的作用:使能SRAM进入写操作工作,启动了写操作相关的电路。

(5)OE不会锁存地址(地址由CE#或WE#锁存)

1.1.1 CS信号

1.1.1.1 CS# 下降沿 (Falling Edge)

-

发生了什么?

当CS#从高电平跳变到低电平时:- 芯片激活:SRAM结束待机状态,整个芯片被唤醒(功耗从静态功耗切换到动态功耗)。

- 地址锁存:锁存当前地址总线(A0-An)的值,并送入地址译码器。

- 启动访问周期:

- 如果是读操作(WE#=高电平):启动存储单元数据读出流程。

- 如果是写操作(WE#=低电平):准备写入驱动器。

- 输出缓冲器预激活:若为读操作,输出缓冲器进入准备状态(但需OE#有效才会真正驱动总线)。

-

关键动作:

锁存地址 + 启动读/写周期

(地址建立时间t_su(addr)要求地址在此下降沿前必须稳定!)

✅ 地址是在CS#下降沿被锁存的,这是SRAM访问的起点。

1.1.1.2 CS# 低电平期间 (Active Low Period)

-

发生了什么?

当CS#保持低电平时:- 持续访问操作:

- 读模式(WE#=高电平):

- 持续输出选中地址的数据(需OE#=低电平)

- 数据总线由SRAM驱动

- 写模式(WE#=低电平):

- 持续将数据总线值写入锁存的地址单元

- 数据总线由外部控制器驱动

- 读模式(WE#=高电平):

- 功耗状态:芯片维持高功耗模式(电流消耗可达待机模式的1000倍)。

- 总线控制:

- 禁止其他存储设备访问同一总线(避免冲突)

- 地址线必须保持稳定(除非流水线访问)

- 持续访问操作:

-

关键动作:

维持访问状态 + 持续执行读写操作

1.1.1.3 CS# 上升沿 (Rising Edge)

-

发生了什么?

当CS#从低电平跳变到高电平时:- 终止访问周期:立即结束当前读/写操作。

- 释放总线:强制禁用输出缓冲器,数据总线进入高阻态(Hi-Z)(不受OE#控制!)。

- 返回待机模式:关闭地址译码器、读写电路,功耗降至静态水平。

- 数据锁定:写操作中,确保存储单元完成状态翻转。

-

关键动作:

结束访问 + 释放总线 + 进入低功耗模式

1.1.1.4 时序逻辑总结

1.1.1.5 与其他信号的交互

-

地址锁存

- 唯一由CS#下降沿触发(WE#写操作时可能二次锁存,但首次锁存由CS#完成)

- 地址必须在CS#下降沿前满足

t_su(addr)(典型值3-10ns)

-

与OE#的优先级

#mermaid-svg-A1EBLzchnjZMej6G {font-family:\"trebuchet ms\",verdana,arial,sans-serif;font-size:16px;fill:#333;}#mermaid-svg-A1EBLzchnjZMej6G .error-icon{fill:#552222;}#mermaid-svg-A1EBLzchnjZMej6G .error-text{fill:#552222;stroke:#552222;}#mermaid-svg-A1EBLzchnjZMej6G .edge-thickness-normal{stroke-width:2px;}#mermaid-svg-A1EBLzchnjZMej6G .edge-thickness-thick{stroke-width:3.5px;}#mermaid-svg-A1EBLzchnjZMej6G .edge-pattern-solid{stroke-dasharray:0;}#mermaid-svg-A1EBLzchnjZMej6G .edge-pattern-dashed{stroke-dasharray:3;}#mermaid-svg-A1EBLzchnjZMej6G .edge-pattern-dotted{stroke-dasharray:2;}#mermaid-svg-A1EBLzchnjZMej6G .marker{fill:#333333;stroke:#333333;}#mermaid-svg-A1EBLzchnjZMej6G .marker.cross{stroke:#333333;}#mermaid-svg-A1EBLzchnjZMej6G svg{font-family:\"trebuchet ms\",verdana,arial,sans-serif;font-size:16px;}#mermaid-svg-A1EBLzchnjZMej6G .label{font-family:\"trebuchet ms\",verdana,arial,sans-serif;color:#333;}#mermaid-svg-A1EBLzchnjZMej6G .cluster-label text{fill:#333;}#mermaid-svg-A1EBLzchnjZMej6G .cluster-label span{color:#333;}#mermaid-svg-A1EBLzchnjZMej6G .label text,#mermaid-svg-A1EBLzchnjZMej6G span{fill:#333;color:#333;}#mermaid-svg-A1EBLzchnjZMej6G .node rect,#mermaid-svg-A1EBLzchnjZMej6G .node circle,#mermaid-svg-A1EBLzchnjZMej6G .node ellipse,#mermaid-svg-A1EBLzchnjZMej6G .node polygon,#mermaid-svg-A1EBLzchnjZMej6G .node path{fill:#ECECFF;stroke:#9370DB;stroke-width:1px;}#mermaid-svg-A1EBLzchnjZMej6G .node .label{text-align:center;}#mermaid-svg-A1EBLzchnjZMej6G .node.clickable{cursor:pointer;}#mermaid-svg-A1EBLzchnjZMej6G .arrowheadPath{fill:#333333;}#mermaid-svg-A1EBLzchnjZMej6G .edgePath .path{stroke:#333333;stroke-width:2.0px;}#mermaid-svg-A1EBLzchnjZMej6G .flowchart-link{stroke:#333333;fill:none;}#mermaid-svg-A1EBLzchnjZMej6G .edgeLabel{background-color:#e8e8e8;text-align:center;}#mermaid-svg-A1EBLzchnjZMej6G .edgeLabel rect{opacity:0.5;background-color:#e8e8e8;fill:#e8e8e8;}#mermaid-svg-A1EBLzchnjZMej6G .cluster rect{fill:#ffffde;stroke:#aaaa33;stroke-width:1px;}#mermaid-svg-A1EBLzchnjZMej6G .cluster text{fill:#333;}#mermaid-svg-A1EBLzchnjZMej6G .cluster span{color:#333;}#mermaid-svg-A1EBLzchnjZMej6G div.mermaidTooltip{position:absolute;text-align:center;max-width:200px;padding:2px;font-family:\"trebuchet ms\",verdana,arial,sans-serif;font-size:12px;background:hsl(80, 100%, 96.2745098039%);border:1px solid #aaaa33;border-radius:2px;pointer-events:none;z-index:100;}#mermaid-svg-A1EBLzchnjZMej6G :root{--mermaid-font-family:\"trebuchet ms\",verdana,arial,sans-serif;}CS#上升沿强制关闭输出缓冲器覆盖OE#状态

- 即使OE#=低电平,CS#上升沿仍会强制总线高阻态

-

与WE#的协同

- 写操作:CS#下降沿锁存地址 → WE#下降沿启动写入驱动器

- 读操作:CS#下降沿锁存地址 → OE#下降沿开启输出

1.1.1.6 设计关键准则

- 最短片选脉宽

t_CS:CS#低电平最小持续时间(确保完成读/写) - 总线切换规则:

- CS#上升沿后需等待

t_OHz才能允许其他设备驱动总线 - 新设备需在CS#上升沿

t_su(addr)后才能发送地址

- CS#上升沿后需等待

- 功耗优化:

快速拉高CS#可显著降低功耗(尤其电池供电设备)

掌握CS#的行为是SRAM接口设计的核心——它是芯片的\"总开关\",控制着整个访问生命周期的开始和结束。

1.1.2 WE信号

1.1.2.1 WE# 下降沿 (Falling Edge)

- 发生了什么?

当WE#从高电平跳变到低电平时,SRAM 启动写周期。此时:- 地址锁存与译码:SRAM会在下降沿锁存当前地址总线上的地址(

A0-An),并将其送入地址译码器,选中目标存储单元(即一个存储单元中的一对交叉耦合反相器)。 - 写入路径激活:SRAM内部连接到目标单元的位线(Bit Lines)和写入驱动器(Write Drivers)被激活,准备写入数据。

- 地址锁存与译码:SRAM会在下降沿锁存当前地址总线上的地址(

- 关键动作:

锁存地址,并开始准备写入流程。

(地址建立时间t_su(addr)要求地址在此下降沿前必须稳定!)

1.1.2.2 WE# 低电平期间 (Active Low Period)

- 发生了什么?

在WE#保持低电平期间:- 数据写入单元:

SRAM 持续驱动数据总线(I/O0-I/O7)的值到目标存储单元的位线上。

写入驱动器会强制覆盖目标单元原有的状态(即打破原有的双稳态),使其转变为新的数据状态。 - 写入稳定性要求:

WE#低电平的最小持续时间称为写使能脉宽t_wp。

这段时间必须足够长,以确保:- 数据总线上的值稳定有效(满足数据建立时间

t_su(data)和保持时间t_h(data))。 - 存储单元有足够时间被成功改写(克服单元内部晶体管的驱动能力,建立新的稳定状态)。

- 数据总线上的值稳定有效(满足数据建立时间

- 数据写入单元:

- 关键动作:

将数据线上的值强制写入锁存地址对应的存储单元。

1.1.2.3 WE# 上升沿 (Rising Edge)

- 发生了什么?

当WE#从低电平跳变回高电平时,SRAM 结束写周期:- 写入通道关闭:

SRAM 断开写入驱动器与位线的连接,停止驱动数据到存储单元。 - 存储单元隔离:

目标单元脱离写入状态,其内部交叉耦合反相器重新形成双稳态,锁定刚写入的值。 - 数据总线释放(如果是共享总线):

若数据总线是双向的(I/O引脚),SRAM会释放总线控制权,允许其他设备使用总线。

- 写入通道关闭:

- 关键动作:

结束写入操作,锁定新数据并恢复存储单元稳定性。

(数据保持时间t_h(data)要求数据在此上升沿后仍需保持短暂稳定!)

1.1.2.4 总结时序关键点

WE# 下降沿WE# = LOWt_wp)WE# 上升沿1.1.2.5 核心结论

- 地址锁存发生在

WE#下降沿。 - 数据写入发生在

WE#低电平期间(写入驱动器持续工作)。 - 数据锁定发生在

WE#上升沿(写入结束,单元恢复稳定状态)。

1.1.3 OE信号

1.1.3.1 OE# 下降沿 (Falling Edge)

-

发生了什么?

OE#从高电平跳变到低电平时:- 开启输出缓冲器:SRAM内部的三态输出缓冲器被激活,允许数据从存储单元输出到数据总线(

I/O引脚)。 - 输出延迟开始计时:从

OE#下降沿到数据真正出现在总线上的时间称为t_OE(输出使能时间)。

(注意:此时地址必须已稳定并完成译码,否则输出可能是无效数据)

- 开启输出缓冲器:SRAM内部的三态输出缓冲器被激活,允许数据从存储单元输出到数据总线(

-

关键动作:

开启数据输出通道,准备将已选中的存储单元数据驱动到总线上。

(地址在OE#下降沿前需满足建立时间t_su(addr)!)

1.1.3.2 OE# 低电平期间 (Active Low Period)

-

发生了什么?

在OE#保持低电平时:- 持续输出数据:SRAM会持续将选中地址的数据驱动到数据总线上。

- 数据稳定性:只要地址和

CE#保持稳定,输出的数据就保持有效。 - 总线占用:此时数据总线被SRAM占用,其他设备应避免驱动总线(避免冲突)。

-

关键动作:

维持数据输出状态,允许外部电路(如CPU)读取数据。

1.1.3.3 OE# 上升沿 (Rising Edge)

-

发生了什么?

OE#从低电平跳变到高电平时:- 关闭输出缓冲器:SRAM的三态输出缓冲器被禁用。

- 总线释放:数据总线进入高阻态(Hi-Z),SRAM不再驱动总线(允许其他设备使用总线)。

- 输出延迟结束:从

OE#上升沿到总线完全变为高阻态的时间称为t_OHz(输出禁用时间)。

-

关键动作:

关闭数据输出通道,释放总线控制权。

1.1.3.4 时序关键点总结

OE# 信号阶段t_OE (输出使能时间)t_OHz (输出禁用时间)1.1.3.5 核心结论

OE#仅控制数据输出:

不锁存地址!地址锁存由CE#(片选下降沿)或WE#(写使能下降沿)触发。- 读操作流程:

- 地址锁定:

CE#下降沿锁存地址 → 译码选中存储单元。 - 数据输出:

OE#下降沿开启输出缓冲器 → 数据出现在总线。 - 总线释放:

OE#上升沿关闭输出缓冲器 → 总线高阻态。

- 地址锁定:

- 关键时序约束:

t_AA(地址访问时间):地址有效到数据输出的延迟(与CE#相关)。t_OE:OE#下降沿到数据输出的延迟(需满足t_OE < t_AA)。t_OHz:OE#上升沿到总线高阻态的延迟(避免总线冲突)。

1.2 信号时序要求

在SRAM的读写时序中,地址信号的建立时间(tAA)和保持时间(tAH)要求地址在控制信号(OE/WE)有效前后保持稳定,但译码器本身并不存储地址,仅依赖当前输入的地址值进行实时译码。典型的地址译码器由逻辑门(如与非门、或非门)构成,属于纯组合逻辑,输出随输入地址的变化而动态调整。

1.2.1 地址建立时间和保持时间的含义

- 地址建立时间(tAA):

从地址信号稳定到OE/WE有效的时间窗口。确保地址译码完成后,控制信号(如OE/WE)才生效,避免误操作。 - 地址保持时间(tAH):在

OE/WE信号有效后,地址信号需保持稳定的时间。防止控制信号切换时地址变化导致数据错误。

1.2.2 地址建立时间和保持时间的作用

(1)防止信号冲突:若地址信号在OE/WE有效时仍在变化,可能导致译码后的存储单元与实际目标单元不一致,引发数据错误。

(2)数据总线的同步:OE/WE控制数据总线的方向(读/写)。地址建立时间和保持时间确保数据总线切换时,地址已稳定,避免总线竞争或数据错位。

(3)工艺与电路延迟:实际电路中,地址译码和驱动电路存在延迟。建立时间和保持时间补偿了这些延迟,确保译码结果与数据操作同步

1.2.3 设计时序要求

-

建立时间约束:要求

地址信号路径延迟 ≤ 控制信号路径延迟 + 时序裕量。 -

保持时间约束:要求

地址信号的最小保持时间 ≥ 控制信号切换后的译码电路响应时间。 -

这里说的

路径延迟是电路特性,延迟时间则对应到了存储器或者MCU手册里所写的各种时序参数,比如存储器的taa参数、STM32的数据建立时间等等

地址建立时间和保持时间并非直接参与译码逻辑,而是为确保地址译码结果与控制信号的有效性在时序上严格匹配。它们的作用是协调地址译码后的存储单元定位与数据总线操作(读/写)之间的同步性,避免因信号延迟或竞争导致的数据错误。因此,这两个参数是SRAM时序完整性设计的关键。

1.3 读写实例

1.3.1 以STM32对SRAM的读操作为例

(1)地址稳定:STM32向地址线输入目标地址,sram的译码器实时完成定位。

(2)CS下降沿:STM32输出片选信号低电平给sram的片选引脚,从而使能sram,让sram的电路能工作即就绪状态,需要等待其他控制信号比如oe有效后,才能执行具体的某一块电路。

(3)OE下降沿:STM32输出使能信号即oe下降沿到sram的oe引脚,从而开启sram的数据总线输出功能,并启动sram内部的读操作电路,关闭写操作电路,读操作电路开始锁存地址线的地址数据并去sram内部存储矩阵里取出对应的数据放到数据线上。

(4)OE上升沿:oe持续一段时间的低电平后(这段时间是留给sram去取出内部数据,要留的满足sram的性能速度要求),STM32输出oe上升沿到sram的oe引脚,这样就相当于关断了sram的数据IO输出功能,但实际上sram的数据IO输出可能不会立即关闭,而是还会持续一段时间,这是由sram的电路设计特性决定了,这个特性就是为了保证STM32能正确采样的数据线上的数据,因为STM32一般会在oe的上升沿去锁存数据线的数据即读取数据,如果sram立即关断数据输出,可能会导致STM32采样到错误数据。

(5)CS上升沿:STM32输出片选信号高电平给sram的片选引脚,使得sram的控制电路失效,因此一般而言cs上升沿代表着一次读写的结束。

(6)若地址在OE有效前(下降沿)未稳定(违反tAA即地址建立时间),可能导致错误的存储单元被选中,地址建立时间一般可以设置即STM32可以设置自身输出cs和oe信号时,控制这俩信号输出的时间间隔,比如cs先输出下降沿,过了2个CLK后oe在输出下降样。

(7)若地址在OE有效后(下降沿)过早变化(违反tAH即地址保持时间),可能导致数据总线输出错误值,地址保持时间一般就不用直接设置了,因为后面的数据建立时间会间接控制地址保持时间:因为oe下降沿之后,oe低电平需要持续一段时间才能变高,这段低电平时间就是留给sram电路取出数据的,也就是数据建立时间——在oe上升沿之前,数据需要提前建立多久STM32才能正确采样到数据——换个说法就是:要留多久时间给sram才能保证oe上升沿之前数据线上出来正确数据并维持一小段时间了。STM32可以设置数据建立时间也就是设置oe低电平持续时间,这段时间由恰好对应到了地址保持时间,因为地址保持时间的意思是指oe下降沿之后地址还要保持多久,而STM32在oe低电平器件地址线是不变的、保持住的。

1.3.2 以STM32对SRAM的写操作为例

(1)地址线稳定,给到sram的地址译码器,实时译码。

(2)STM32输出cs下降沿给sram,sram的控制电路就绪。

(3)STM32输出we下降沿给sram,启动写操作电路:电路在做什么?锁存地址译码数据

(4)STM32输出we上升沿沿给sram,sram会锁存数据线数据,因此

- 需要地址建立时间 —— STM32可以控制cs和we输出的先后顺序,满足sram的地址建立时间要求;

- 需要数据建立时间 ——在we上升沿之前留足够多的时间即STM32控制we低电平持续时间,满足sram在收到we下降沿后至少过多久才能把数据送出来的时间要求,we低电平时间要大于这个时间;

- 数据保持时间则是在STM32输出we上升沿之后,sram输出电路不立即失效,而是还能维持数据线数据一段时间;

- 地址保持时间同样含在了we低电平期间,因为这个期间,地址线数据是不变化的、保持的。

(5)STM32输出cs上升沿给sram,使得sram的控制电路失效,因此一般而言cs上升沿代表着一次读写的结束。

二、分析和理解时序参数

2.1 时序的本质

时序图要区分哪些是要求,哪些是能力,即对外界信号的时序要求和自身输出能力。因为电路传播时间不同,所以要保证控制信号按照实际需要的传播速度在合适的时刻和顺序传播到目标位置,保证读写到正确数据和正确地址。这也难怪参数都是ns级别的,因为cmos管开关时间就是ns级别的,商用CPU晶体管开关频率:量产芯片中通常≤7 GHz(极端散热下可达9 GHz)。存储器手册里给出的各种参数,实际上都是在描述电路里电流的传播路径、传播时间即存储器电路的属性、特性,因此结合实际的电路或者功能框图理解这些参数会更容易一些,更容易区分出哪些参数属于器件设计的特性,哪些是可以调节的或者允许的、有余量的。

2.2 建立时间和保持时间

-

地址译码电路的工作不受

oe 、we 、cs等控制信号的影响,但这些信号会决定后续是否使用译码出的地址值;一旦数据线稳定了,地址译码电路就一直在工作,持续进行译码操作,sram会在oe或者we有效的时刻使用译码后的地址,因此在这个时刻附近,地址线务必保持稳定一段时间即地址建立和保持时间。 -

地址建立、保持时间,数据建立、保持时间的定义在不同的sram或者mcu里有差异,因此配置的时候更应该关注具体含义是什么,让mcu输出能满足sram的时序信号即可。

-

一般会定义成:

地址持续的总时间=地址建立时间+地址保持时间 + WE/OE低电平时间

数据持续的总时间=数据建立时间+数据保持时间 + WE/OE低电平时间 -

使用地址的时刻一般是:

-

对于读操作,是在

oe下降沿,sram要使用地址去定位存储单元即锁存译码后的地址,开始根据地址把数据取出放到数据总线,因为oe为低后sram电路才能工作,去使用此时译码得到的地址。因此在oe下降沿,mcu要为sram提供足够的地址建立和保持时间;oe下降沿期间,sram根据地址取出数据放到总线上;在oe上升沿,mcu会读取和锁存数据总线,此时地址线也要稳定,也就是mcu要保持地址线稳定,防止误操作和总线冲突,因此也就需要地址保持时间; -

对于写操作,有两种说法

-

一种是:写操作时,应该是在we下降沿时sram就锁存地址并定位到sram内部存储地址了吧,并且也是在we下降沿,FSMC开始着手往数据线上放数据了吧;we低电平期间则是sram在获取数据线并将其解析和搬运到sram内部(和读操作时sram将内部数据往外搬运到数据线上,刚好是相反操作,是需要一定的时间的即数据建立时间);we上升沿则是让sram锁存数据线数据并往目标地址里写入数据的操作

-

另一种是:在

we上升沿锁存数据并将数据写入到目标地址,即在we上升沿使用地址,因此在we上升沿之后地址还要保持一段时间即地址保持时间,在上升沿之前地址也要保持一段时间即地址保持时间。we下降沿表示sram开始写操作过程,we和地址线可以同时有效或者we较晚;we低电平期间,sram进行地址译码和处理写操作,并在低电平期间等待到mcu发来的数据线,数据线持续一段时间后,mcu再拉高we开始写入即为sram提供足够的数据建立时间,we上升沿开始写入,地址还要保持一段时间。- tAW :Address setup to write end

- tHA :Address hold from write end

- tSA :Address setup to write start

- 和地址建立相关的参数有两个!一个是基于we下降沿,一个是基于we上升沿,很容易混淆,所以说可能不能太拘泥于定义,不同的器件里的定义可能有差别。根据deepseek回答,倾向于第一种的说法,后面的介绍页也以第一种为准。

-

-

使用数据的时刻一般是:

- 对于读操作,

sram给出数据而mcu去读取数据,mcu会在oe上升沿时锁存数据,因此oe上升沿附近,sram要提供满足mcu要求的数据建立和保持时间,而oe持续为低的这段时间就是sram在根据地址取出数据,这段时间设置的要大于sram的取数据所需时间; - 对于写操作,

sram会在we上升沿锁存数据线,因此mcu需要给sram提供满足要求的数据建立和保持时间。we下降沿表示让sram启动写操作电路。

- 对于读操作,

-

至于地址建立时间是

tsa还是taw还是tsa+taw,说法不一,但mcu需要同时满足这两个时序参数,即地址输出后需要间隔tsa时间后才能输出we下降沿,需要间隔tsa+taw时间后才能输出we上升沿,姑且认为是在we上升沿的时候sram锁存数据线并执行数据写入,地址线也是在we上升沿时刻被用到即定位到SRAM存储单元的位置 -

一般通用规则是:

- 读过程:(1)在

oe下降沿,sram要使用地址去定位存储单元即锁存译码后的地址,开始根据地址把数据取出放到数据总线;(2)sram给出数据而mcu去读取数据,mcu会在oe上升沿时锁存数据; - 写过程:(1)

we下降沿表示sram开始写操作过程并锁存地址译码数据,we和地址线可以同时有效或者we较晚(2) 在we上升沿锁存数据并将数据写入到目标地址,即在we上升沿使用地址和数据;

- 读过程:(1)在

-

如果采样器件性能好,一些保持时间、建立时间可以为0。

三、SRAM时序参数和配置FSMC时序参数

3.1 功能框图

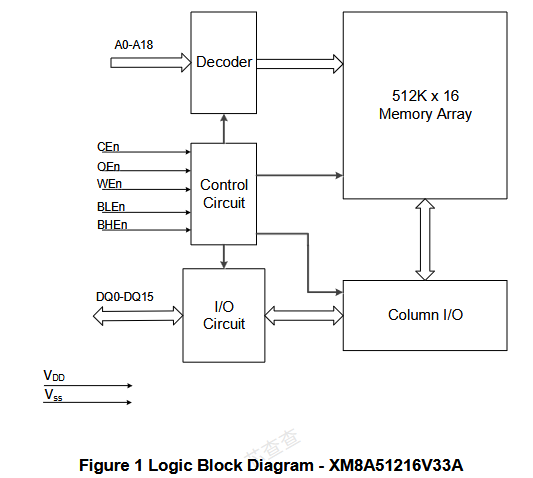

SRAM型号是XM8A51216V33A

地址译码电路:实时译码,译码过程不受控制信号影响,但译码值是否使用则由控制信号决定控制信号电路:控制读写操作,写操作需要WE有效,启动写电路;读操作则只需OE允许向外输出数据即可,因为读电路要比写电路简单数据IO电路:OE可以控制IO电路是输出(读取数据)还是输入(写入数据)

3.2 SRAM的读时序参数

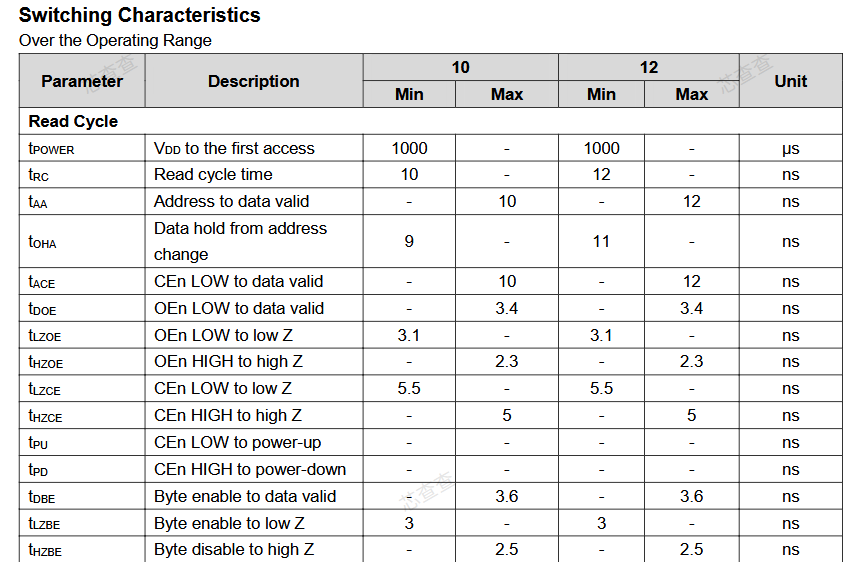

表格里的参数反映的是sram电路设计的特点,是每个信号在电路里的传播路径和传播时间,以及需要控制部分信号的到达顺序即时序,比如地址先于oe下降沿到达,数据先于oe上升沿出现等等,因此外部mcu访问此sram时,需要控制给出的数据、地址、cs、oe等信号的到达顺序。注意:这里的ce就是cs信号,只是在不同器件里名字有差别。

-

tpower:从sram的vdd上电开始到sram能开始工作进行第一个访问,至少等待1000us才能正常开始工作,因此不能一上电就立即访问 -

trc:读一次数据所需时间至少是10ns,算下来访问频率最高是100Mhz,因此MCU对sram的访问不能太快,一般就是控制ce的间隔 -

taa:从给到sram地址到sram把数据送出来,最多耗时10ns,数据线上的数据就准备好了,但是访问周期不能是10ns,因为被trc给限制了,说明数据出来后cs还要持续一段时间有效 -

toha:地址线变化后,上次的数据线还要保持一定时间,至少保持10ns,也就是说在读时序中,地址线可提前进行变化,因为地址在oe下降沿就锁存使用了 -

tace:从ce有效即ce下降沿到数据有效即数据送出来,最多需要10ns,这个和taa对应了;这也透露了个问题,地址在ce之前就已经译码完成准备好了,也就是说地址在ce下降沿之前就变化准备好了 -

tdoe:从oe有效即oe下降沿到数据有效即数据送到数据线上,最多需要3.4ns,如果MCU在ce有效后过了15ns才给出有效的oe信号,那么就是要在ce有效后的第15+3.4=18.4ns的时候数据才能给到数据线上,这个18.4和tace的10不冲突,10表示的是最大值即工作条件都很好的情况下,最慢也就10ns,如果工作条件不是很好,最慢肯定会超过10ns了。这个参数和tace是否间接要求了cs和oe之间需要一定的时间间隔?根据一些sram配置例子,这中时序图画法并没有间接要求cs和oe之间需要的时间间隔。 -

tlzoe:oe有效即下降沿到数据线变成低阻态即转变成有效数据态,至少要等3.1ns,也就是说数据线要反应个3.1ns才能进入工作状态,但是sram内部的数据已经准备好了,只是数据IO电路承载数据需要反应时间 -

thzoe:oe上升沿到数据线变成高阻(数据变失效、数据IO电路关闭)最多需要2.3ns,也就是数据保持时间:读结束后,数据线还会维持最多2.3ns -

tlzce:ce下降沿到数据线变为低阻,至少需要等5.5ns,这个和tlzoe一起来看:说明ce和oe会一起决定数据IO电路是否能进入低阻状态,并且oe的传输路径要短一些,因此最快只要3.1ns就打开数据IO了,ce的传输路径要长一些,因此最快5.5ns,但数据IO要想真正进入低阻状态,显然ce和oe要同时都把信号传递过来才可以!这意味着:如果是ce先有效比如第0ns有效,然后第5.5ns传递过去,在第3ns时oe才有效,第6.4ns传递过去,那么就要在第6.6ns时数据IO才变成低阻态;如果oe第0ns有效,ce第5ns有效,那么在第5+5.5=10.5ns时数据IO才有效 -

thzce:ce上升沿到数据变高阻(数据变失效)最多等待5ns。同理:如果oe上升沿出现在第10ns,ce上升沿出现在第15ns,那么就在第15+5=20ns的时候数据IO才恢复高阻;如果oe在第15ns,ce在第13ns,那么就在第13+5=18ns时数据IO恢复高阻,因为oe和ce要同时为高才行 -

这里面重点的就是

taa:这是留给sram电路根据地址拿到数据所需要的时间

3.3 SRAM的读时序图示

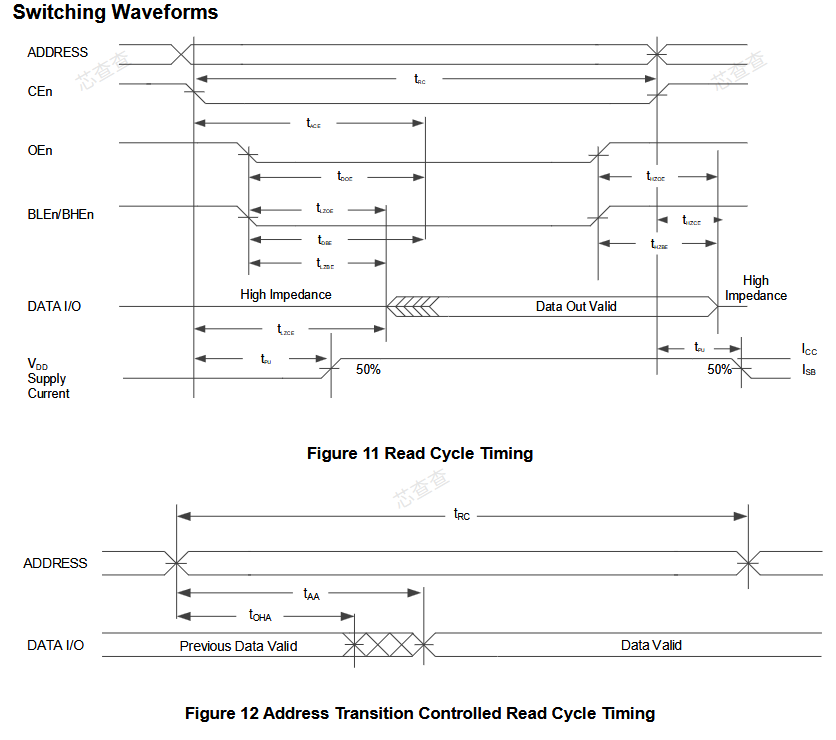

需要将参数和具体的时序图对应上。这里可以看出,读此sram可以有两种方式,一种是常规的用oe信号控制即在oe下降沿使用地址,在oe上升沿外部MCU读取数据;一种是只用地址线来访问数据而无需控制信号( During the address transition controlled read cycle, CEn is LOW, OEn is LOW, and WEn is in the state of don’t care也就是说在这种模式下ce和oe都是一直为低电平),估计也要看MCU的外部总线模块是否支持这种访问方式吧。

上述是读sram时,mcu需要为sram提供的时序图以及sram对外输出数据的能力。对时序图中的参数进行详细分析。

3.4 配置FSMC模块的读参数

3.4.1 参数分析

-

【1】

sram的能力/要求,地址建立时间:同时接收到地址和cs下降沿、oe下降沿是能正常访问sram的,即sram对地址建立时间参数无要求。因为读时序图上地址和oe下降沿之间没有参数,说明对此是没有要求的。 -

【2】

MCU的能力,地址建立时间:输出的地址变化、cs下降沿和oe下降沿是否允许同时出现?- 如果某个

mcu的地址线和cs同时变化的,并且如果cs和oe固定是同时出现下降沿,也就意味着这个mcu提供的地址建立时间只能为0(地址建立时间:读时序中指的是从地址稳定到oe下降沿的时间),那么可能不适合很多sram,因此大多数mcu可以调整地址变化时刻(也是cs下降沿)和oe下降沿之间的时间间隔即地址建立时间参数。不过这个sram读时序图对cs和oe下降沿之间的时间间隔并没有要求,也对地址建立时间无要求,这也就意味着mcu即使同时给出地址、cs下降沿、oe下降沿也是符合这个sram的读访问时序要求的。如果设置地址建立时间为1ns,那么就是地址和cs下降沿同时变化,但是oe相较于地址变化后1ns后才能出现下降沿。 - 如果某个

mcu由于硬件设计特点导致输出的地址线和cs不是同时变化的,比如,给出地址线后过了5ns才能给出cs信号,并且oe一般要晚于cs出现下降沿,那么这时就要设置MCU的地址建立时间参数至少是5ns

- 如果某个

-

【3】

sram的能力/要求,数据建立时间tace、tdoe:接收到地址后或cs有效后(这里两者是同时刻有效)最慢多久就会把数据放到总线上,即最慢tace或者taa后数据就出来了(给到地址后sram内部电路能在10ns以内把数据送出来)。给到oe有效后,sram内部电路则最慢3.4ns就能把数据送到数据线上,即tdoe。 -

【4】因此对

mcu的要求:mcu要在地址或cs有效后,至少再等tace的时间再读数据总线上的数据,也就是等待数据建立完成。并且,mcu要在地址或oe有效后,至少再等tdoe的时间再读数据总线上的数据,也就是等待数据建立完成。 -

【5】

MCU的能力,数据建立时间:调整oe低电平的持续时间即数据建立时间,给足够多的时间来满足sram的tace、taa参数,这样MCU才能在oe上升沿正确采集到数据- 假如某个

mcu的特点是:给出地址数据后必须至少要再过5ns才能给处cs下降沿,那么上述读时序中,地址和cs要错开5ns了,而tace还是10ns,那就是地址给出15ns后才能给出数据,cs给出10ns后才能给出数据,MCU需要在地址给出的至少15ns后再去读数据总线,也就是在地址之后至少15ns后MCU才能给出oe上升沿。 - 数据建立时间:如果这个mcu的特点是地址和cs下降沿、oe下降沿同时有效,那么可以设置此mcu的地址建立时间为

0,此mcu输出的地址、cs、oe时序是符合sram读时序要求的(如果设置为1ns,则oe下降沿晚于cs下降沿1ns)。另外还需要满足数据建立时间要求也就是cs之后要至少过10ns后才能输出数据(oe之后至少3.4ns,需要以大的参数为准),那么mcu就要设置数据建立时间参数即决定oe低电平持续时间至少是10ns,从而保证了mcu在cs下降沿之后10ns之后才去读取数据线上的数据。

- 假如某个

-

【6】

MCU的能力/要求,数据保持时间th(Data_NOE):Data hold time after FSMC_NOE high 即在NOE上升沿(FSMC采集数据线)之后,数据线还至少要保持多久的时间即数据保持时间,才能保证FSMC能正确采集到数据线,至少保持0ns -

【7】

sram的能力,数据保持时间thzoe:oe上升沿到数据线变成高阻(数据变失效、数据IO电路关闭)最多需要2.3ns,也就是数据保持时间:读结束后,数据线还会维持最多2.3ns,能够满足MCU对数据保持时间th(Data_NOE)的要求 -

【8】

时序参数验算:将MCU的FSMC参数设置好后,还要根据sram的其他时序参数验算时序,比如典型的sram的读周期(trc:读一次数据所需时间至少是10ns)对时序的约束等等 -

【9】

MCU读取一次sram的总耗时/读取速度:即cs低电平持续时间:至少包括了地址建立时间和数据建立时间。

3.4.2 参数配置

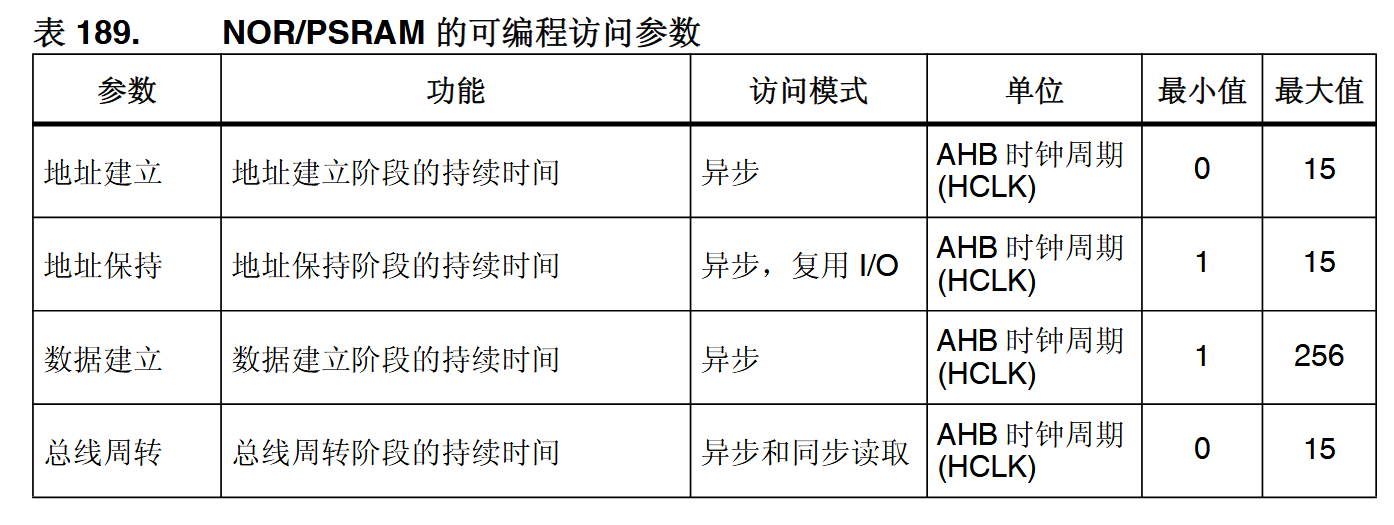

异步静态存储器(NOR Flash、PSRAM、SRAM)

● 信号通过内部时钟 HCLK 进行同步。不会将此时钟发送到存储器

●FSMC 总是会先对数据进行采样(OE或WE上升沿),而后再禁止片选信号 NE(即NE上升沿不早于OE或WE上升沿)。这样可以确保符合存储器数据保持时序的要求(数据转换的芯片使能高电平,通常最低为 0 ns。)

●如果使能扩展模式(FSMC_BCRx 寄存器中的 EXTMOD 位置 1),则最多可提供四种扩展模式(A、B、C 和 D)。可以混合使用 A、B、C 和 D 模式来进行读取和写入操作。例如,可以在模式 A 下执行读取操作,而在模式 B 下执行写入操作。

●如果禁用扩展模式(FSMC_BCRx 寄存器中的 EXTMOD 位复位),则 FSMC 可以在模式 1 或模式 2 下运行,如下所述:

当选择 SRAM/CRAM 存储器类型时,模式 1 为默认模式(FSMC_BCRx 寄存器中MTYP = 0x0 或 0x01)。

当选择 NOR 存储器类型时,模式 2 为默认模式(FSMC_BCRx 寄存器中 MTYP =0x10)。

- FSMC中访问模式有很多种,mode 1模式下读取,地址、cs、oe同时有效,信号的先后顺序不可调即地址建立时间失效。因此这里以mode A模式为例介绍如何配置时序参数。

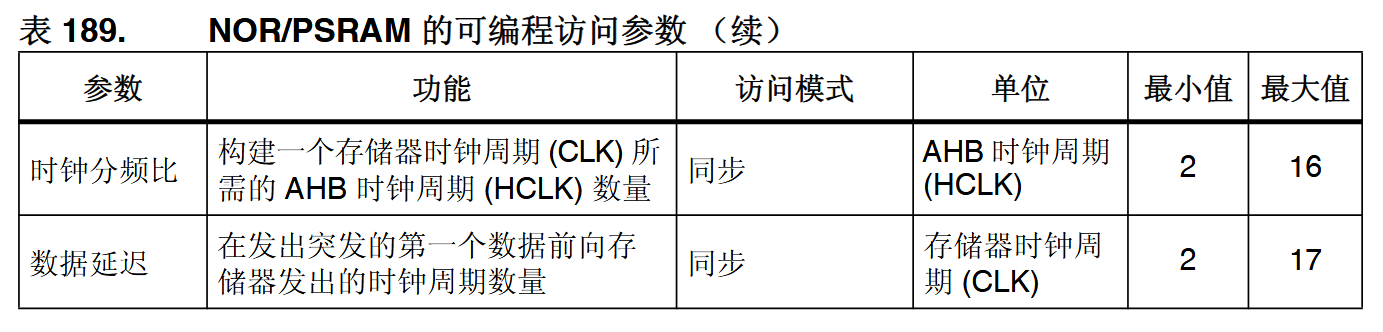

3.4.2.1 FSMC允许用户配置的参数有哪些?见用户参考手册

-

允许用户配置的参数

-

根据

sram特点配置FSMC参数,对于读时序,FSMC使用HCLK=168MHz,一个周期是6ns,根据模式A的读取访问时序分析,设置地址建立时间参数和数据建立时间参数如下:-

sram对地址建立时间无要求,允许地址和oe下降沿同时变化,因此FSMC中可将此参数设置为0 -

mcu就要设置数据建立时间参数即决定oe低电平持续时间至少是10ns,从而保证了mcu在cs下降沿之后10ns之后才去读取数据线上的数据,因此数据建立时间参数至少为 10ns / 6ns = 2个HCLK - 访问一次至少用时

2个HCLK即12ns,则最大访问速度是1/12ns=83MHz

-

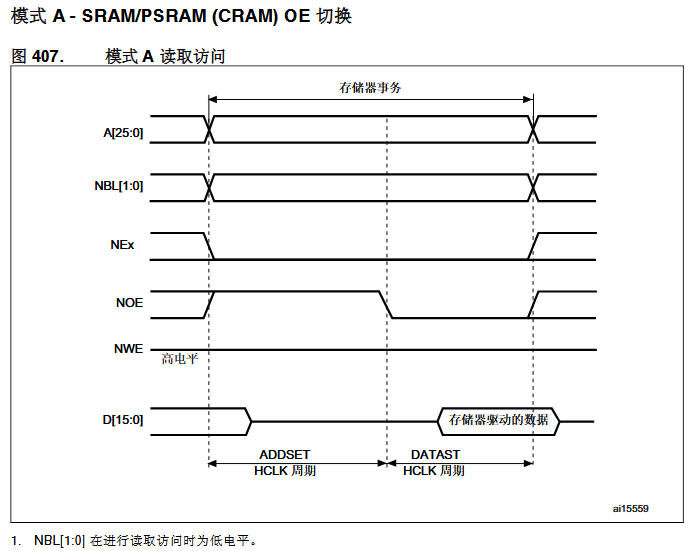

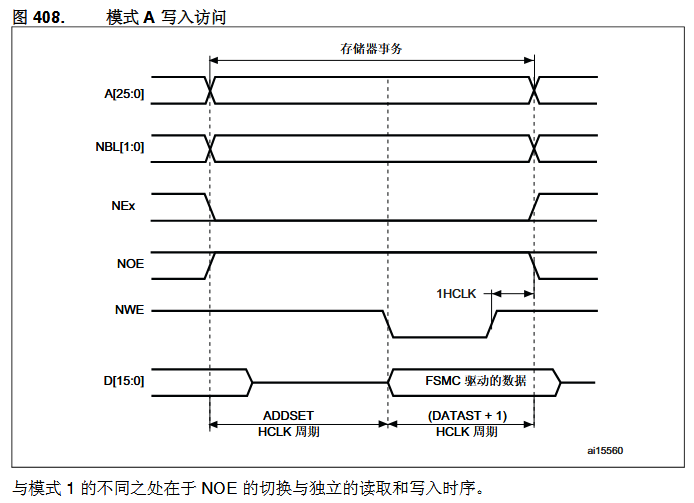

- 从用户手册里的模式A的读时序图来看,有以下特点

- 地址、NBL、NE都是在同一时刻进行变化的

- 地址(地址变有效也是NE下降沿)和NOE下降沿之间的时间间隔是可调的,即

地址建立时间参数 - 地址(地址变有效也是NE下降沿)和NOE上升沿是同时变化的

- NOE低电平持续时间称为

数据建立时间参数 - 数据线的数据是存储器比如sram驱动输出的数据,其持续时间存在

数据保持时间即NOE上升沿之后,数据还会保持一段时间 -

设置ADDSET参数可以控制FSMC给出地址有效后过了多久才给出NOE的下降沿即锁存地址线数据 -

设置DATAST参数可以控制FSMC给出NOE下降沿后过了多久才给出NOE的上升沿即留给sram用于取出内部数据的时间

3.4.2.2 FSMC固定参数有哪些,哪些是电路特性参数或者说输出误差,哪些是可调参数?见数据手册

数据手册里提供了参数配置例子,也补充了用户手册里没有的一些细节时序参数

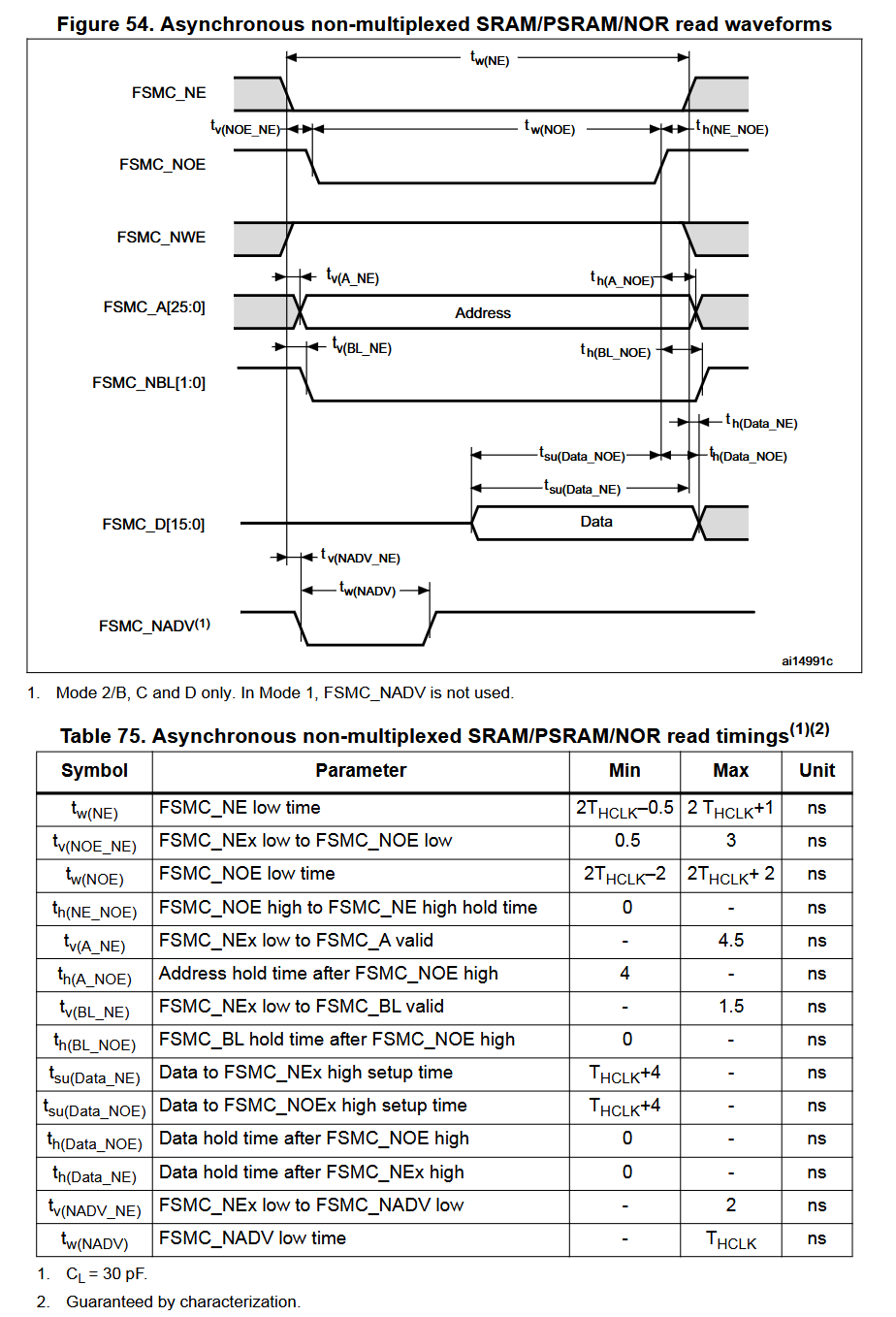

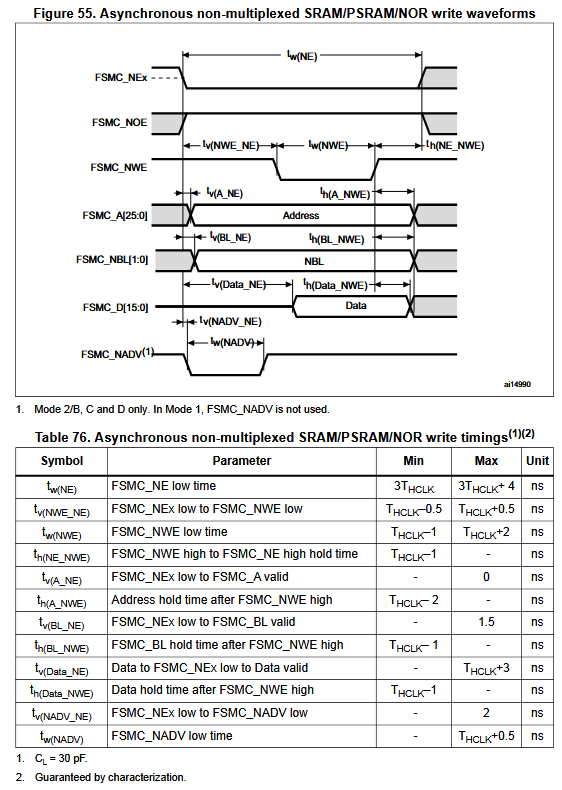

Asynchronous waveforms and timings

Figure 54 through Figure 57 represent asynchronous waveforms and Table 75 through Table 78 provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

• AddressSetupTime = 1

• AddressHoldTime = 0x1

• DataSetupTime = 0x1

• BusTurnAroundDuration = 0x0

In all timing tables, the THCLK is the HCLK clock period

翻译后的结果是

异步波形和时序

图54到图57表示了异步波形,表75到表78展示了对应的时序参数。这些表格里的参数是基于FSMC这些配置参数生成的

FSMC的地址建立时间参数设置为1

FSMC的地址保持时间参数设置为1

FSMC的数据建立时间设置为1

FSMC的总线切换周期设置为0

FSMC的时钟为HCLK=168MHz,一个周期是约6ns

模式A的读时序

基于上述参数配置,才得到了模式A读时序表格中的参数。注意,数据手册里还有模式B、C、D的读时序参数,是有区别的(与模式 1 的不同之处在于设置扩展模式(模式 B、C)时的 NWE 切换与独立的读取和写入时序)。

tw(NE):FSMC_NE low time 即NE低电平持续时间为2HCLK-0.5 —— 2HCLK + 1- 为什么会出现

2HCLK?因为片选NE的总时间一般就是地址建立时间+数据建立时间(tw(NE) = (ADDSET + DATASET) * HCLK)这个关系要参考用户手册里的FSMC时序图),而数据手册里里将这两个参数都配置成了1,因此NE的低电平持续时间就是2HCLK,至于-0.5和+1,应该属于电路特性,比如信号传播时间的误差。 - 这里的

ADDSET和DATASET是用户可以设置的参数。

- 为什么会出现

信号同步

● 所有的控制器输出信号在内部时钟 (HCLK) 的上升沿变化

● 在同步模式(读取或写入)下,输出的数据在 HCLK 的上升沿变化。无论 CLKDIV 值为

何,所有输出均会按以下方式变化:

— 当出现 FSMC_CLK 时钟的下降沿时,NOEL / NWEL / NEL / NADVL / NADVH / NBLL / 地

址有效输出可发生变化。

— 当出现 FSMC_CLK 时钟的上升沿时,NOEH / NWEH / NEH / NOEH / NBLH / 地址有效

输出可发生变化。

tv(NOE_NE):FSMC_NEx low to FSMC_NOE low 即NE下降沿和OE下降沿之间的时间差,这里是给出了个0.5 —— 3ns的范围,这个参数应该属于FSMC的电路特性(信号传播路径长度不同导致传播时间不同,出现了先后顺序;或者也有可能是FSMC需要先产生NE信号,然后隔几个ns后才能产生OE信号;这些都是猜测)而不是用户可以设置的参数。在用户手册里的时序图,画的NE和OE是同时变化的,并没有体现这个时间差,说明在普通使用FSMC时把NE和OE当做同时出现下降沿即可,只有比较细致的优化参数和访问速度才考虑NE和OE不同步的情况吧tw(NOE):FSMC_NOE low time 即OE低电平的持续时间,范围是2HCLK - 2 —— 2HCLK + 2,为什么是2HCLK ? 这个参数是可以用户配置。tv(NE_NOE):FSMC_NOE high to FSMC_NE high hold time 即NOE上升沿到NE上升沿之间的时间差,最小值是0ns,这个参数应该也是FSMC的电路特性,和信号的传播路径长度有关,用户手册里的时序图则是NOE和NE的上升沿同时出现tv(A_NE):FSMC_NEx low to FSMC_A valid 即在地址线变化前(地址变有效),NE提前多久出现下降沿,即NE下降沿到地址线的时间间隔,NE比地址线最多提前4.5ns出现,这也属于FSMC电路特性,用户手册里的时序图则是NE下降沿和地址变化沿同时出现th(A_NOE):Address hold time after FSMC_NOE high 即NOE上升沿到地址变化(地址变无效)的时间,表示FSMC在输出NOE上升沿之后,还会让地址线维持一段时间,地址线最多多维持1.5ns,这也是FSMC的电路特性,用户手册里的时序图则是OE上升沿和地址变化沿(地址变无效)同时出现tv(BL_NE):FSMC_NEx low to FSMC_BL valid 即NE下降沿到NBL变有效即下降沿的时间,表示NE比NBL提前多久有效,最多提前1.5ns,这也属于FSMC电路特性,用户手册里的时序图则是NE下降沿和NBL下降沿同时出现th(BL_NOE):FSMC_BL hold time after FSMC_NOE high 即在NOE上升沿之后,NBL过多久才会变成上升沿,即NBL上升沿比NOE上升沿至少晚0ns,这也属于FSMC电路特性,因此上限值不确定,不是用户设置的,用户手册里的时序图则是NOE上升沿和NBL上升沿同时出现tsu(Data_NE):Data to FSMC_NEx high setup time 即在NE上升沿之前(FSMC结束本次读取过程),数据线需要提前多久出现即数据建立时间,才能保证FSMC正确采集到数据线内容。至少提前HCLK + 4ns的时间,其中HCLK为用户设置的数据建立时间参数,4ns应该是FSMC的电路特性,会有一定的信号传播延迟,用户手册里的时序图则对应到DATASET参数即DATASET=1。用户设定的参数。tsu(Data_NOE):Data to FSMC_NOEx high setup time 即在NOE上升沿之前(FSMC采集数据线),数据线需要提前多久出现即数据建立时间,才能保证FSMC正确采集到数据线内容。至少提前HCLK + 4ns的时间,其中HCLK为用户设置的数据建立时间参数,4ns应该是FSMC的电路特性。这一部分和tsu(Data_NE)相同了,因为用户手册里的时序图里NOE上升沿和NE上升沿是同时出现的,实际上如果考虑两者之间实际的传播延时即参数th(NE_NOE)即NE上升沿比NOE上升沿晚了th(NE_NOE)时间,那么实际上用户设置的数据建立时间参数(DATASET=1)对应的是tsu(Data_NOE),而tsu(Data_NE) = tsu(Data_NOE) + th(NE_NOE),不过一般的参数配置只看用户手册里的时序图即可,不用考虑的这么细致。用户可设置的参数。th(Data_NOE):Data hold time after FSMC_NOE high 即在NOE上升沿(FSMC采集数据线)之后,数据线还至少要保持多久的时间即数据保持时间,才能保证FSMC能正确采集到数据线,至少保持0ns。这个参数其实是对sram提出了要求,对应到sram的【thzoe:oe上升沿到数据线变成高阻(数据变失效)最多需要2.3ns】。假如这个参数最小是5ns,那就意味着sram必须能够提供5ns的数据保持时间也就是说sram的读时序中必须是NOE上升沿之后数据线还要至少能保持5ns,否则这个sram就不适合用FSMC来访问。FSMC用户手册里的读时序图则对数据保持时间无要求,图中未体现此参数。th(Data_NE):Data hold time after FSMC_NEx high 即在NOE上升沿(FSMC采集数据线)之后,数据线还至少要保持多久的时间,才能保证FSMC能正确采集到数据线,至少保持0ns。和th(Data_NOE)同理,这个参数其实是对sram提出了要求,对应到sram的【thzce:ce上升沿到数据变高阻(数据变失效)最多等待5ns】。FSMC用户手册里的读时序图则对数据保持时间无要求,图中未体现此参数。tv(NADV_NE):FSMC_NEx low to FSMC_NADV low 即NE下降沿会比NADV下降沿提前多久出现,最多提前2ns出现,这属于FSMC的电路特性,用户无法设置和调整。用户手册里的时序图则是NE下降沿和NADV下降沿同时出现。tw(NADV):FSMC_NADV low time 即NADV低电平持续时间,最大值是HCLK,说明是用户可以设置的。NADV信号只有在模式B、C、D等模式下才起作用,在模式A下不起作用。

3.4.3 综上分析

- FSMC读sram时:

-

地址建立时间、地址保持时间、数据建立时间、数据保持时间实际上都有所体现,只不过是地址保持时间(FSMC提供)和数据保持时间(sram提供)是不可调整的或者要求较低的,但实际使用中还是要验算一下的。 因此,对FSMC的配置主要体现在地址建立时间和数据建立时间 -

sram对地址建立时间参数(输入给

sram的地址有效时刻要比输入的oe下降沿至少早多久)无要求。————>因此FSMC可以设置地址建立时间参数为ADDSET=0(FSMC控制输出的oe下降沿在输出地址有效后多久才输出) -

sram对数据建立时间参数(输入给

sram的oe上升沿之前要保证oe低电平至少持续一定的时间,保证sram有足够的时间取出内部数据)有要求:从ce有效后至少等到10ns,也就是oe低电平至少持续10ns。————>因此,FSMC可以设置数据建立时间参数为DATASET=2(表示2HCLK=12ns)(FSMC控制从oe下降沿让sram开始取出内部数据到oe上升沿FSMC读取数据线数据,这段oe低电平时间就是留给sram的数据建立时间) -

sram对地址保持时间参数有要求:这个要求实际上体现在

sram参数tace和taa(给到地址后sram内部电路能在10ns以内把数据送出来,其实也意味着这10ns时间内地址线要保持不能变化)。————>因此,FSMC在输出ce、oe低电平时地址线不会变化,因此只需设置足够久的oe低电平时间即可,也就是数据建立时间,所以说是通过设置数据建立时间间接满足了地址保持时间 -

FSMC对数据保持时间参数有要求(电路特性,无法调整):

th(Data_NOE):Data hold time after FSMC_NOE high 即在NOE上升沿(FSMC采集数据线)之后,数据线还至少要保持多久的时间即数据保持时间,才能保证FSMC能正确采集到数据线,至少保持0ns。————>因此,sram输出数据时的数据保持实现参数也是电路特性,不可调整,只能验算看两者是否匹配:thzoe:oe上升沿到数据线变成高阻(数据变失效、数据IO电路关闭)最多需要2.3ns,也就是数据保持时间:读结束后,数据线还会维持最多2.3ns。而FSMC需要的是至少0ns,验算下来,是能够满足FSMC的要求的 -

验算其他参数:

sram读时序中要求trc即读周期时间最小是10ns即ce低电平时间要大于10ns。————>因此,FSMC输出给sram的地址有效的持续时间、ce低电平持续时间都要大于10ns,而FSMC输出的ce低电平持续时间=(ADDSET+DATASET)*HCLK = (0+2)*6ns = 12ns,满足了trc>10ns的要求

-

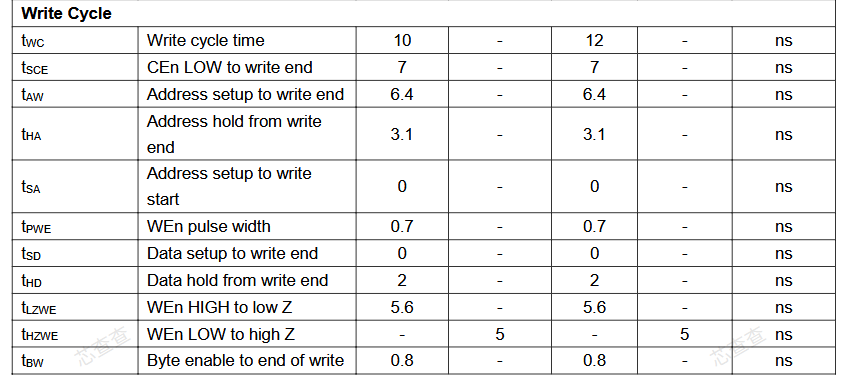

3.5 SRAM的写时序参数

这个sram的写操作时序有两种,也就是可以用两种方式(ce控制和we控制,猜测:ce控制的话就是在ce的上升沿执行写操作,we控制就是在we上升沿执行写操作,两种时序没法指定选择用那种,只要FSMC能给出任意一种符合写时序要求的信号时序图即可完成对sram的写操作)来写此sram。这里以 WEn Controlled Write Cycles 即we控制写时序图为例分析。

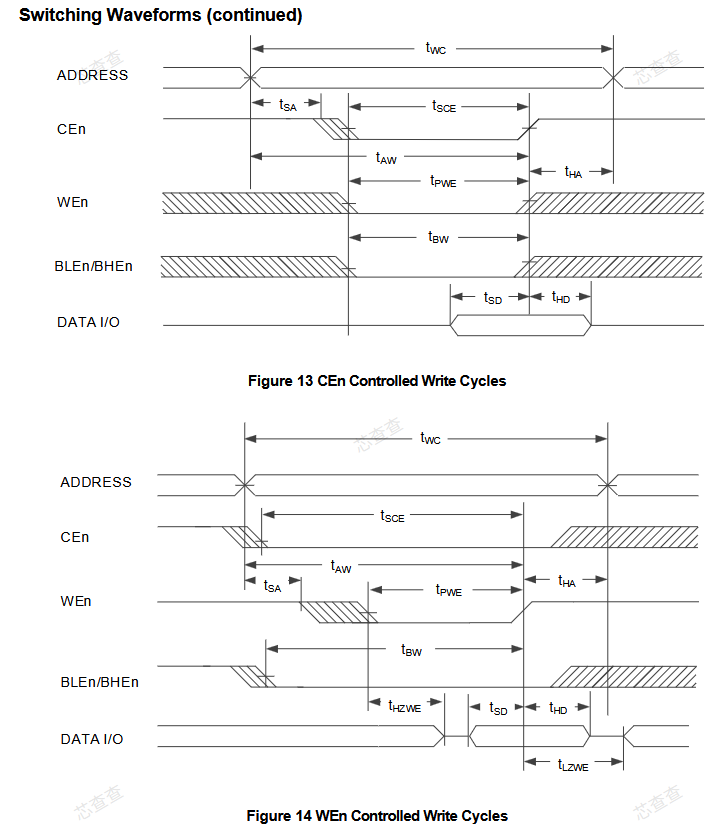

CE控制写操作的时序图

twc:写周期至少需要10ns,对应的是在一次写操作中,地址有效的持续时间,也就是说写操作频率不超过100Mhz,因此MCU的片选cs有效的频率不能超过10Mhz

tsce:ce下降沿到写结束即ce上升沿(即ce低电平持续时间),至少要有7ns,即MCU要给sram至少提供7ns的cs,这里的写结束是ce上升沿,也是we上升沿,因为两者在同一时刻,如果MCU给过来的是先we上升沿,隔一段时间再是ce上升沿,那么写结束就是ce上升沿,实际上一般是we上升沿开始锁存和写入数据

taw:从地址变化即有效到写结束即ce上升沿的时间,至少要6.4ns,地址要给足时间,在使用地址的时刻前,地址提前存在多久时间,或者说要求FSMC给出地址后,至少要过6.4ns后才能给出ce上升沿执行锁存数据并开始写入数据到sram中

tha:从写结束即ce上升沿到地址下一次变换的时间,也就是写结束后地址还需要保持的时间,在使用地址的时候后,地址还要持续保持多久时间,至少需要保持3.1ns,FSMC要提供足够的保持时间

tsa:从地址变有效到ce有效,至少需要0ns,也就是说ce可以和地址一起变化或者ce晚于地址变化,这说明了地址译码电路运行很快,性能很好

tpwe:we信号持续时间,至少要0.7ns,这样才能启动写电路

tsd:数据建立时间,数据输入即有效后,至少过了0ns才能结束写操作即给出ce上升沿,也就是说数据线上一旦给出数据后,ce就可以结束了,说明采样电路性能挺好,只要数据在ce有效段出现了就好

thd:写结束后即ce上升沿后,数据至少需要保持2ns,才能结束,是为了确保能正确采样数据

tlzwe:we上升沿到数据线下次变成低阻,至少需要5.6ns,也就是数据线至少需要休息5.6ns

thzwe:we下降沿到上次的数据线变成高阻,最多等待5ns,也就是说上次的数据线可能会持续到本次的写时序中

tbw:字节是能信号有效到写结束即ce上升沿,至少需要0.8ns,这样看的话对字使能信号没有太多要求了,那么很晚才给出也没问题写操作主要关注的就是地址建立时间、地址保持时间、数据保持时间

WE控制写操作的时序图

twc:Write cycle time 即写周期至少需要10ns,对应的是在一次写操作中,地址有效的持续时间,也就是说写操作频率不超过100Mhz,因此FSMC的片选cs有效的频率不能超过10Mhz

tsce:CEn LOW to write end 即ce下降沿到写结束即we上升沿,至少要有7ns,即要求FSMC在给sram提供有效地址和ce下降沿后,至少要等待7ns后才能执行写操作即提供we上升沿(一般是we上升沿开始锁存和写入数据),sram至少需要7ns的时间才能完成对数据线数据的采样和写入前的准备即数据建立时间。如果FSMC提供的ce下降沿、we下降沿、地址变有效是同时出现的,那么这个数据建立时间实际上就等于we低电平的持续时间。

taw:Address setup to write end 即从地址变有效到写结束即we上升沿的时间,至少要6.4ns,表示的是在使用地址的时刻前(we上升沿),地址需要提前存在多久时间,为地址建立时间。或者说要求FSMC给出地址后,至少要过6.4ns后才能给出we上升沿执行锁存数据并开始写入数据到sram中,这个参数也是对应到了we低电平持续时间

tha:Address hold from write end 即从写结束即we上升沿到地址下一次变换的时间,也就是写结束后地址还需要保持一段时间,至少需要保持3.1ns,因此,FSMC在输出we上升沿之后还要让地址线至少维持3.1ns的时间即地址保持时间

tsa:Address setup to write start 即从地址变有效到we有效即we下降沿,至少需要0ns,也就是说FSMC输出的地址变有效和we下降沿可以同时输出给sram,sram也是能够接受的,we可以和地址一起变化或者we晚于地址变化,这说明了地址译码电路运行很快,性能很好

tpwe:WEn pulse width 即we低电平持续时间,至少要0.7ns,FSMC至少输出0.7ns的低电平we信号才能启动sram的写功能电路

tsd:Data setup to write end 即数据建立时间,数据输入即数据线有效后,至少要过了0ns才能进行写操作即给出we上升沿,也就是说FSMC在给出we上升沿之前,we低电平至少持续0ns的时间,保证sram能有足够时间获取和解析数据线上的数据,为写操作(we上升沿)做准备。

thd:Data hold from write end 即写结束后即we上升沿后,数据线至少需要保持2ns,才能结束,是为了确保能正确采样数据,因此,FSMC给出we上升沿之后还要继续保持住数据线内容不变,至少持续2ns不变

tlzwe:WEn HIGH to low Z 即we上升沿到数据线下次变成低阻,至少需要5.6ns,这段时间包含了 thd数据保持时间和数据线空闲间隔时间,FSMC需要控制写操作的时间间隔

thzwe:WEn LOW to high Z 即we下降沿到上次的数据线变成高阻,最多等待5ns,也就是说上次的数据线可能会持续到本次的写时序中,在本次写时序中,we下降沿之后至少要等待5ns后再去使用数据线上的数据

tbw:Byte enable to end of write 即字节是能信号下降沿到写结束即we上升沿,至少需要0.8ns,这样看的话对字使能信号没有太多要求了,那么很晚才给出也没问题写操作主要关注的就是地址建立时间、地址保持时间、数据保持时间

3.6 SRAM的写时序图示

需要将参数和具体的时序图对应上。这里可以看出,写此sram可以有两种方式,一种是常规的用we信号控制即在we下降沿启动写操作,在we上升沿锁存数据和地址,进行写入;一种是用ce来控制写入数据

3.7 配置FSMC模块的写参数

3.7.1 参数分析

- sram的能力/要求,地址建立时间:

sram对外部输入的地址有效到外部输入的we下降沿要求的时间间隔(地址建立时间)是tsa>=0ns,对外部输入的地址到外部输入的we上升沿要求的时间间隔是taw>6.4ns,对外部输入的we低电平持续的时间长度要求是tpwe>=0.7ns - 对

FSMC的要求:FSMC输出有效地址和cs下降沿给sram后,可以立即输出we下降沿,但输出的we低电平持续时间至少是6.4ns,即至少6.4ns之后才能对外输出we上升沿。 - FSMC的能力,地址建立时间:

设置ADDSET=0可使得cs下降沿和we下降沿同时输出; - FSMC的能力,数据建立时间:

设置DATASET=2,可以使得we低电平持续时间为2个HCLK=12ns - sram的能力/要求,数据建立时间:在收到外部输入的

we上升沿之前,需要提前收到外部输入的数据线数据,需要提前tsd>0ns时间收到。字节使能信号则提前tbw>0.8ns收到下降沿。 - 对

FSMC的要求:根据这个tsd>0ns条件,FSMC输出数据到数据线后可以立即输出we上升沿给sram,让sram进行数据写入 - FSMC的能力,数据建立时间:

设置DATASET=0,会使得输出的we低电平时间为0,不符合tpwe>=0.7ns的要求,因此DATASET的值需要大于0才行,保持为DATASET=2 - sram的能力/要求,数据保持时间:在收到外部输入的

we上升沿之后,外部输入的数据线还需要保持thd>=2ns的时间,以保证sram能正确写入数据 - 对

FSMC的要求:FSMC需要在输出we上升沿之后,还要维持输出数据线至少2ns - FSMC的能力,数据保持时间:没有相关参数设置数据保持时间,而是硬件上固定设计为

1个HCLK=6ns的保持时间,能够满足sram对数据保持时间的要求 - sram的能力/要求,地址保持时间:在收到外部输入的

we上升沿之后,外部输入的地址线还需要保持thd>=3.1ns的时间,以保证sram能正确写入数据 - 对

FSMC的要求:FSMC需要在输出we上升沿之后,还要维持输出地址线至少3.1ns - FSMC的能力,地址保持时间:和数据保持时间相同,没有相关参数设置数据保持时间,而是硬件上固定设计为

1个HCLK=6ns的保持时间,能够满足sram对地址保持时间的要求 - 验算其他参数:

sram要求写周期twc>10ns——>FSMC设置的参数为ADDSET=0,DATASET=2,输出cs低电平时间=(ADDSET+DADASET+1)HCLK=3HCLK=18ns,满足twc>10ns的要求

3.7.2 参数配置

3.7.2.1 FSMC允许用户配置的参数有哪些?见用户参考手册

-

允许用户配置的参数

-

从用户手册里的模式A的写时序图来看,有以下特点

- 地址、NBL、NE都是在同一时刻进行变化的

- 地址(地址变有效也是NE下降沿)和NWE下降沿之间的时间间隔是可调的,即

地址建立时间参数 - 地址(地址变有效也是NE下降沿)和NWE上升沿是有固定时间间隔,即

NWE要比地址、数据、NE都早1个HCLK出现上升沿,这个时间就是FSMC提供的地址保持时间和数据保持时间 - NWE低电平持续时间称为

数据建立时间参数,用于将数据线数据放入sram内部 -

设置ADDSET参数可以控制FSMC给出地址有效后过了多久才给出NWE的下降沿即提前稳定地址线,为NWE上升沿锁存地址线数据做准备 -

设置DATAST参数可以控制FSMC给出NWE下降沿后过了多久才给出NWE的上升沿即用于将数据线数据放入sram内部,为NWE上升沿锁存数据线数据做准备

- 根据sram特点配置FSMC参数,对于写时序,

FSMC使用HCLK=168MHz,一个周期是6ns,根据模式A的写入访问时序分析,设置地址建立时间参数、地址保持时间参数和数据建立时间参数如下:- 地址建立时间:sram对地址建立时间要求为

tsa:Address setup to write start 即从地址变有效到we有效即we下降沿,至少需要0ns,也就是说FSMC输出的地址变有效和we下降沿可以同时输出给sram,sram也是能够接受的,因此FSMC中可将此参数设置为0ns / 6ns = 0,即ADDSET = 0 - 地址建立时间:sram对地址建立时间的额外要求为

taw:Address setup to write end 即从地址变有效到写结束即we上升沿的时间,至少要6.4ns,表示的是在使用地址的时刻前(we上升沿),地址需要提前存在多久时间,为地址建立时间,因此FSMC中可将此参数设置为6.4ns / 6ns = 2,即DATASET = 2(FSMC中表示的we低电平持续时间),地址建立时间到底是tsa还是taw?猜测:应该是tsa吧。写操作时,应该是在we下降沿时sram就锁存地址并定位到sram内部存储地址了吧,并且也是在we下降沿,FSMC开始着手往数据线上放数据了吧;we低电平期间则是sram在获取数据线并将其解析和搬运到sram内部(和读操作时sram将内部数据往外搬运到数据线上,刚好是相反操作,是需要一定的时间的即数据建立时间);we上升沿则是让sram执行往目标地址里写入数据的操作 - 数据建立时间,数据输入即数据线有效后,至少要过了0ns才能进行写操作即给出we上升沿,并且,即we低电平持续时间,至少要0.7ns,

FSMC至少输出0.7ns的低电平we信号才能启动sram的写功能电路,不过数据建立时间已经由参数taw:Address setup to write end约束了,已经设置了DATASET=2,使得we低电平满足了大于0.7ns的时间要求 - 访问一次至少用时3个HCLK即

18ns,则最大访问速度是1/18ns=55MHz

- 地址建立时间:sram对地址建立时间要求为

3.7.2.2 FSMC固定参数有哪些,哪些是电路特性参数,哪些是可调参数?见数据手册

数据手册里提供了参数配置例子,也补充了用户手册里没有的一些细节时序参数

模式A的写时序

-

tw(NE):FSMC_NE low time 即FSMC输出的NE低电平持续时间 = 3HCLK —— 3HCLK+ 4 ns,用户可设置此参数,比如此时设置的ADDSET=1,DATASET=1,而根据用户手册的时序图:NE低电平时间=(ADDSET+DATASET+1)*HCLK=3HCLK,4ns则是信号在电路里传播时间误差 -

t v(NWE_NE):FSMC_NEx low to FSMC_NWE low即FSMC输出NE下降沿后过多久才会输出NWE下降沿,即地址建立时间ADDSET,用户可配置此参数,比如此时ADDSET=1,对应tv(NWE_NE) =HCLK - 0.5—— HCLK+0.5 ns -

tw(NWE): FSMC_NWE low time 即FSMC输出的NWE低电平的持续时间,即数据建立时间DATASET,用户可配置此参数,比如此时DATASET=1,对应tw(NWE) = HCLK – HCLK +2 ns -

th(NE_NWE): FSMC_NWE high to FSMC_NE high hold time 即FSMC输出NWE上升沿之后过了多久才输出NE上升沿,也就是NWE早于NE结束,用户无法配置,而是设计固定为1个HCLK,th(NE_NWE) = HCLK –1 ns -

tv(A_NE):FSMC_NEx low to FSMC_A valid 即FSMC输出有效地址后过多久才会输出NE下降沿,属于电路特性,用户无法配置,tv(A_NE) <= 0 ns说明FSMC输出有效地址的时刻不会早于NE下降沿的输出 -

th(A_NWE):Address hold time after FSMC_NWE high 即FSMC输出NWE上升沿(sram在此时写锁存数据和地址并写入)后还会让地址线维持一段时间,即地址保持时间,用户无法配置,而是设计固定为1个HCLK,即th(A_NWE) = HCLK – 2 ns -

tv(BL_NE):FSMC_NEx low to FSMC_BL valid 即FSMC输出NE下降沿后过多久才会输出NBL边沿,属于电路特性,用户无法配置,tv(BL_NE) <= 1.5 ns -

th(BL_NWE): FSMC_BL hold time after FSMC_NWE high 即FSMC输出NWE上升后还会让NBL维持一段时间,和参数th(A_NWE)保持一致,设计固定为1个HCLK,tv(BL_NE) > HCLK – 1 ns -

tv(Data_NE):Data to FSMC_NEx low to Data valid 即FSMC输出NE下降沿之后过了多久才会输出数据到数据线上,此参数会间接受到ADDSET参数的影响,因为看FSMC的时序图:数据是在NWE下降沿之后才出现,此时设置ADDSET=1,那么tv(Data_NE)至少有1个HCLK的间隔,tv(Data_NE) < HCLK +3 ns -

th(Data_NWE):Data hold time after FSMC_NWE high 即FSMC输出NWE上升沿之后还会让输出的数据线维持一段时间以适应sram的数据保持时间,这个参数用户无法配置,而是设计固定为1个HCLK,th(Data_NWE) > HCLK –1 ns -

tv(NADV_NE):FSMC_NEx low to FSMC_NADV low 即FSMC输出NE下降沿之后过多久才输出NADV下降沿,属于电路特性,用户无法配置,tv(NADV_NE) < 2 ns -

tw(NADV):FSMC_NADV low time 即FSMC输出的NADV低电平的持续时间,此参数会间接受到ADDSET参数的影响,因为看FSMC的时序图:NADV是在NE下降沿和NWE下降沿之间出现,此时设置ADDSET=1,则tw(NADV) < HCLK + 0.5 ns -

位于写入事务末尾的一个 HCLK 周期有助于确保 NWE 上升沿之后的地址和数据保持时间。由于存在此 HCLK 周期,DATAST 值必须大于零 (DATAST > 0)。

3.8 程序配置FSMC模块参数

(1)综上分析,理论上最大访问速度时的参数为:

-

FSMC读参数

- 地址建立时间ADDSET = 0 (sram对地址建立时间无要求)

- 地址保持时间ADDHOLD = 0 (模式A下此参数不起作用)

- 数据建立时间DATASET = 2 (sram要求至少提供10ns用于取出数据)

- 读取一次总耗时即cs低电平时间=(ADDSET +DATASET )*HCLK = 2HCLK=12ns(符合sram的读周期trc>10ns要求),访问频率为1/12ns=83MHz

-

FSMC写参数

- 地址建立时间ADDSET = 0 (sram对地址建立时间无要求)

- 地址保持时间ADDHOLD = 0 (模式A下此参数不起作用)

- 数据建立时间DATASET = 2(sram要求至少提供7ns用于处理地址线和数据线)

- 写入一次总耗时即cs低电平时间=(ADDSET +DATASET +1)*HCLK =3HCLK=18ns(符合sram的写周期twc>10ns要求),访问频率为1/18ns=55MHz

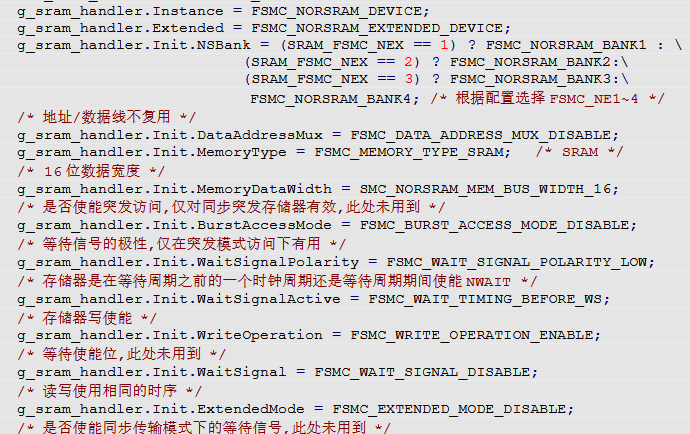

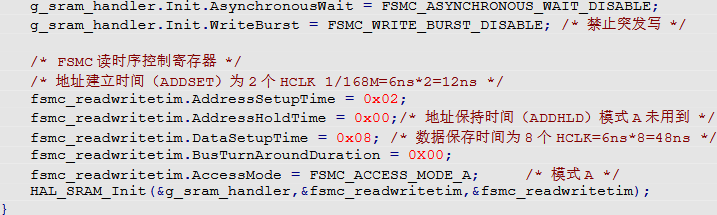

(2)这部分配置是正点原子提供的FSMC例程

这里配置的是有问题的

fsmc_readwritetim.AccessMode = FSMC_ACCESS_MODE_A;g_sram_handler.Init.ExtendeMode = FSMC_EXTENDED_MODE_DISABLE;因为在FSMC的参考手册里这样说:如果想使用模式A,那么应该把扩展模式使能

- 如果使能扩展模式(FSMC_BCRx 寄存器中的 EXTMOD 位置 1),则最多可提供四种扩展模式(A、B、C 和 D)。可以混合使用 A、B、C 和 D 模式来进行读取和写入操作。例如,可以在模式 A 下执行读取操作,而在模式 B 下执行写入操作。

- 如果禁用扩展模式(FSMC_BCRx 寄存器中的 EXTMOD 位复位),则 FSMC 可以在模式 1 或模式 2 下运行,如下所述: 当选择 SRAM/CRAM 存储器类型时,模式 1 为默认模式(FSMC_BCRx 寄存器中MTYP = 0x0 或 0x01)。

当选择 NOR 存储器类型时,模式 2 为默认模式(FSMC_BCRx 寄存器中 MTYP =0x10)。