使用华三模拟器HCL搭建双核心网络架构(M-LAG)实现

M-LAG(Multichassis Link Aggregation Group)即跨设备链路聚合组,是一种实现跨设备链路聚合的机制,将一台设备与另外两台设备进行跨设备链路聚合,从而把链路可靠性从单板级提高到了设备级,组成双清系统。

常见的双核心网络架构有三种:

1.传统STP/RSTP/MSTP架构

2.堆叠(Stacking)架构

3.M-LAG(跨设备链路聚合)架构

三种双核心架构对比总表

◼️ 预算有限项目

◼️ 低实时性业务

◼️ 追求极简管理

◼️ 同型号设备部署

◼️ 高可用+高性能需求

◼️ 零中断升级场景

◼️ 无特殊硬件

◼️专用堆叠模块/线缆

◼️ 堆叠授权许可

◼️高速Peer-Link(多链路聚合)

◼️独立Keepalive链路(带外管理)

✅ 通用性强(全网兼容)

✅ 配置简单(基础防环)

✅毫秒级切换(≤50ms)

✅跨设备链路聚合(带宽叠加)

✅独立升级(零丢包)

✅故障域隔离(单设备故障局部影响)

❌收敛慢(1-50秒)

❌ 需手动优化防次优路径

❌升级需整组重启

❌扩展受限(固定成员数)

❌Peer-Link故障易引发双主

❌ 硬件成本高(需高速互联端口)

802.1w (RSTP)

802.1s (MSTP)

Huawei CSS/iStack

H3C IRF

Huawei M-LAG

H3C DRNI

Arista MLAG

关键维度深度解析

1.链路利用率与收敛时间

2.运维复杂度对比

3.风险对比

总结建议

-

选STP:预算有限 + 非实时业务(如学校机房、小型办公室)。

-

选堆叠:统一管理优先 + 设备同源(如企业分支机构接入层)。

-

选M-LAG:金融/数据中心核心,追求零中断升级与最大化带宽利用。

本次实验的为M-LAG架构方式:

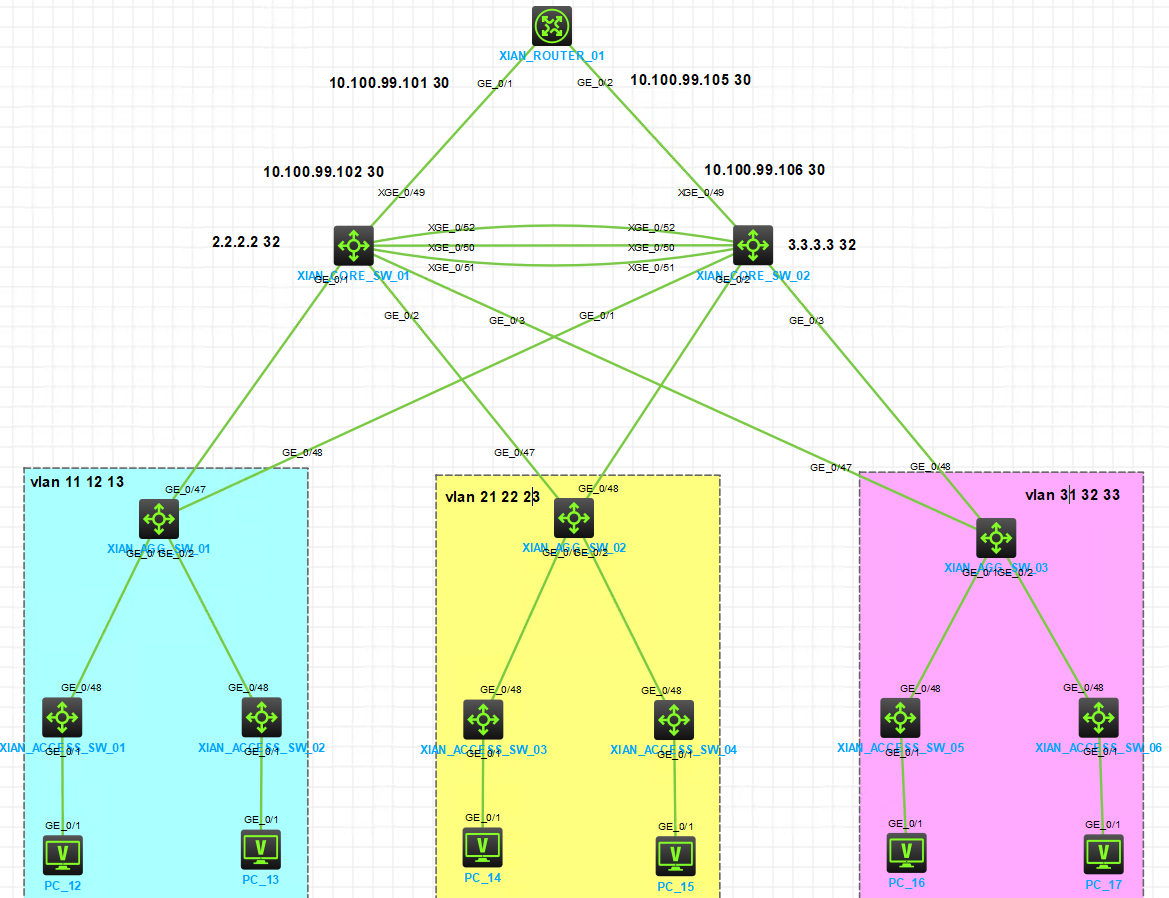

拓扑图如下,是一个基本的三层架构网络:核心层、汇聚层、接入层

①核心层通过两台核心交换机配置M-LAG实现负载均衡和冗余,达到毫秒级的切换。

②核心交换机为网关设备并提供DHCP服务

③核心交换机和汇聚交换机通过创建汇聚端口互联

(一)配置核心交换机

1、配置核心交换机1:XIAN_CORE_SW_01

①添加VLAN、配置m-lag

sys

[H3C]sys XIAN_CORE_SW_01

[XIAN_CORE_SW_01] dhcp enable

[XIAN_CORE_SW_01] vlan 11 to 13

[XIAN_CORE_SW_01] vlan 21 to 23

[XIAN_CORE_SW_01] vlan 31 to 33

关闭m-lag一致性检查(模拟器bug)

[XIAN_CORE_SW_01] m-lag consistency-check disable

[XIAN_CORE_SW_01] m-lag consistency-check mode loose

配置m-lag(修改系统MAC、编号、优先级)

[XIAN_CORE_SW_01] m-lag system-mac 1-1-1

[XIAN_CORE_SW_01] y

[XIAN_CORE_SW_01] m-lag system-number 1

[XIAN_CORE_SW_01] y

[XIAN_CORE_SW_01] m-lag system-priority 4096

[XIAN_CORE_SW_01] y

配置keepalive接口,本端地址为1.1.1.1/,对端地址为1.1.1.2

[XIAN_CORE_SW_01] m-lag keepalive ip destination 1.1.1.2 source 1.1.1.1

[XIAN_CORE_SW_01] interface Ten-GigabitEthernet1/0/50

[XIAN_CORE_SW_01] port link-mode route

[XIAN_CORE_SW_01] y

[XIAN_CORE_SW_01] ip add 1.1.1.1 24

在MAD中排除Keepalive接口

[XIAN_CORE_SW_01] m-lag mad exclude interface Ten-GigabitEthernet1/0/50

[XIAN_CORE_SW_01] quit

<