紫光FPGA与modelsim联合仿真报错问题解决_紫光modelsim联合仿真

PDS软件介绍

首先还是先介绍一下紫光同创FPG的开发环境吧,紫光同创FPGA 的开发软件叫做\"Pango Design Suite \"也可以叫PDS,是紫光同创为了客户端对紫光FPGA进行项目开发,从而研制的一款EDA工具;里面集成了从HDL描述到位流生成与下载调试的可编程工具套件以及可以兼容第三方仿真工具,仿真一般都是使用modelsim进行仿真。

问题以及背景

开头已经给各位简单的介绍了紫光同创的开发环境以及基本功能,本次遇见的问题就出在客户在使用PDS和modelsim 进行联合仿真时,modelsim出现了报错\"error loading design \"的报错;无法出现波形,客户这边使用的是VHDL;

原因分析

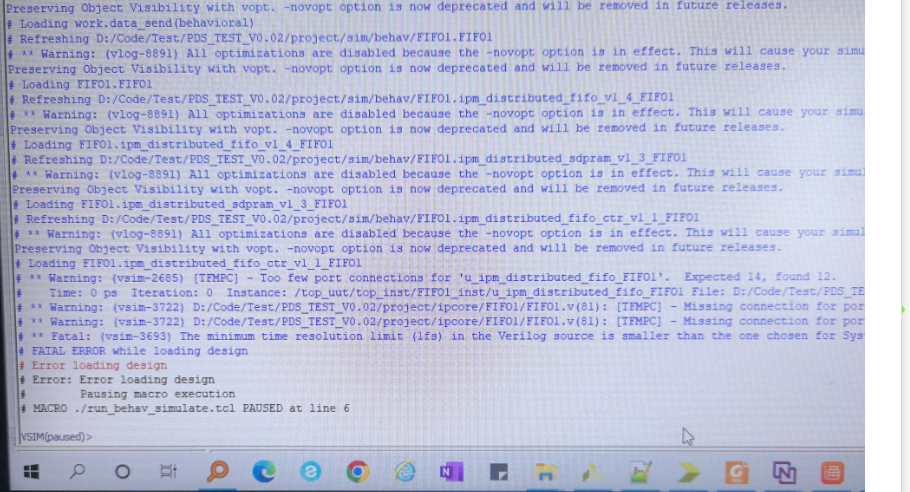

当modelsim出现这个报错的时候,其实第一个注意点应该不要放在“error loading design ”的这个报错本身,应该要找找是什么原因导致的这个报错,因为导致仿真失败的问题有很多种,需要查看日志或者transcript里面的警告信息来进行问题定位;不要盲目的直接拿着这个“error loading design ”本身去网上搜索找答案,这样会很浪费时间;好了说回正题,我们要解决问题,肯定是要复现出问题了,拿到客户的工程在我自己的电脑上跑了一下,成功的复现出了问题,既然成功的复现出了问题,那接下来就是做排查了啊;问题报错如下图:

看到这些信息呢,注意到这么多的警告信息,该怎么确认是那一个警告信息导致的仿真失败呢,那么这里就要注意到一个关键词“FATAL”,翻译过来就是“致命的”,那这里就基本可以确认是这里导致的仿真失败。这里就需要研究一下这个致命警告信息了, Fatal: (vsim-3693) The minimum time resolution tinit (hfgl ih the verilog souree is smaller than the one chosen for SyA FATAL FEPOR while loading design;这里大致的意思是时间精度不匹配;那么现在就可以带着这个问题去寻找答案了。

解决方案

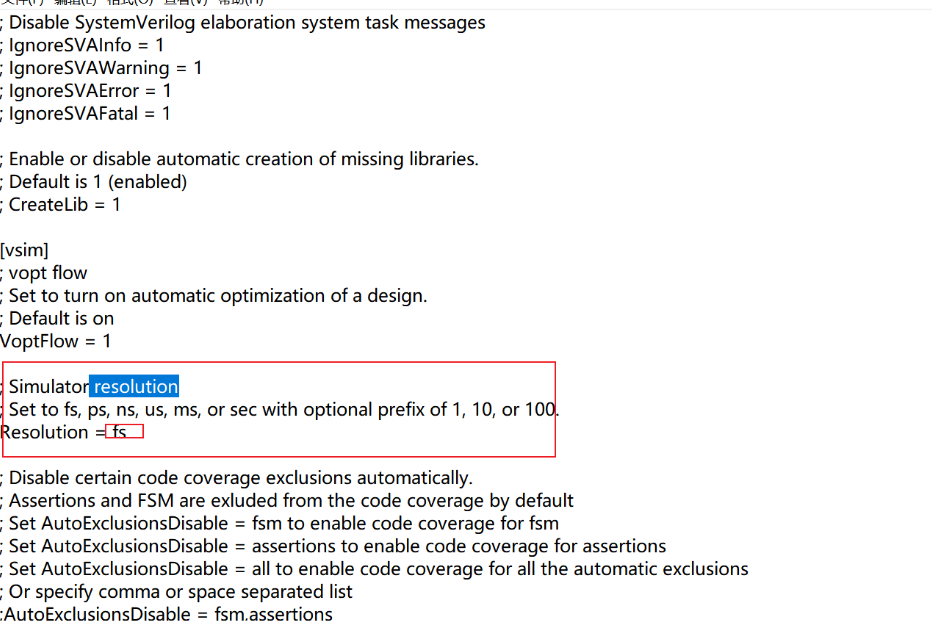

这里出现时间精度不匹配,你如果是使用的Verilog那么只需要将仿真文件里面的\'timescle 10ns/10ns这个时间精度函数的值进行修改就可以,根据警告信息;但是我这边客户使用的是VHDL,这种方法显然不行,VHDL没有这个时间函数,那么可以modelsim使用“vsim -t 1ps work.”这个指令来设置时间精度;当然可能UP的电脑性能和版本的问题啊,使用这个指令modelsim会一直强制退出,我也不知道为啥。然后后面就找了其他的方案,就是修改modelsim的initial文件里面的参数`Resolution`: 修改成 Resolution = fs;如下所示:

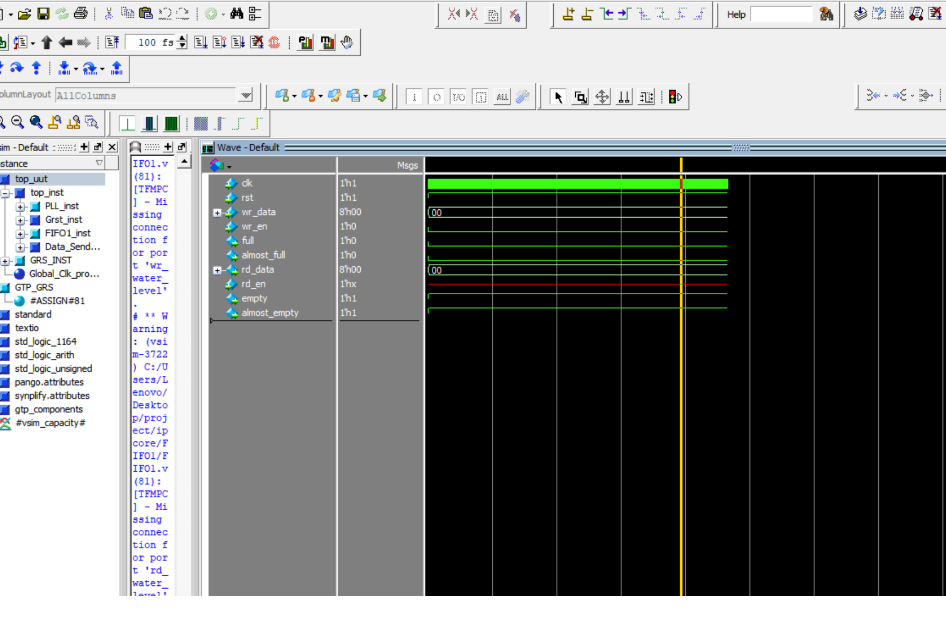

我这里修改的是编译完的那个库文件下面的ini文件,修改完毕后点击bat 文件就可以进行仿真了。当然修改文件这里大家可以试试修改一下modelsim安装目录下的initial文件,不过得记得备份。我这边修改后也是成功的出现了波形;问题得到了,如下所示:

好了,这次的问题就分享到这里了,希望对在使用紫光同创FPGA做开发遇到相关问题的小伙伴有有一定的帮助,另外这里UP还有一个方法还没进行验证(懒),后面找个时间试试哈哈哈。