蜂鸟E203 hbirdv2项目复现与FPGA开发【基于Linux】

目录

1 前言

1.1 设计目标与定位

1.2 架构特性

1.3 开发与调试支持

1.4 配套SoC与扩展性

2 开发环境

3 移植思路

4 准备工作

4.1 E203工程获取

4.2 具体安装步骤

4.3 E203项目的目录结构

5 vcs+verdi仿真

5.1 编译测试

5.2 运行仿真

5.3 显示波形

6 SDK测试

6.1 环境搭建

6.2 获取SDK工程

6.3 编译SDK工程

6.4 SDK联合仿真

6.5 修改ITCM和DTCM容量

7 FPGA工程与上板调试

7.1 vivado综合

7.2 上板调试

8 参考链接

1 前言

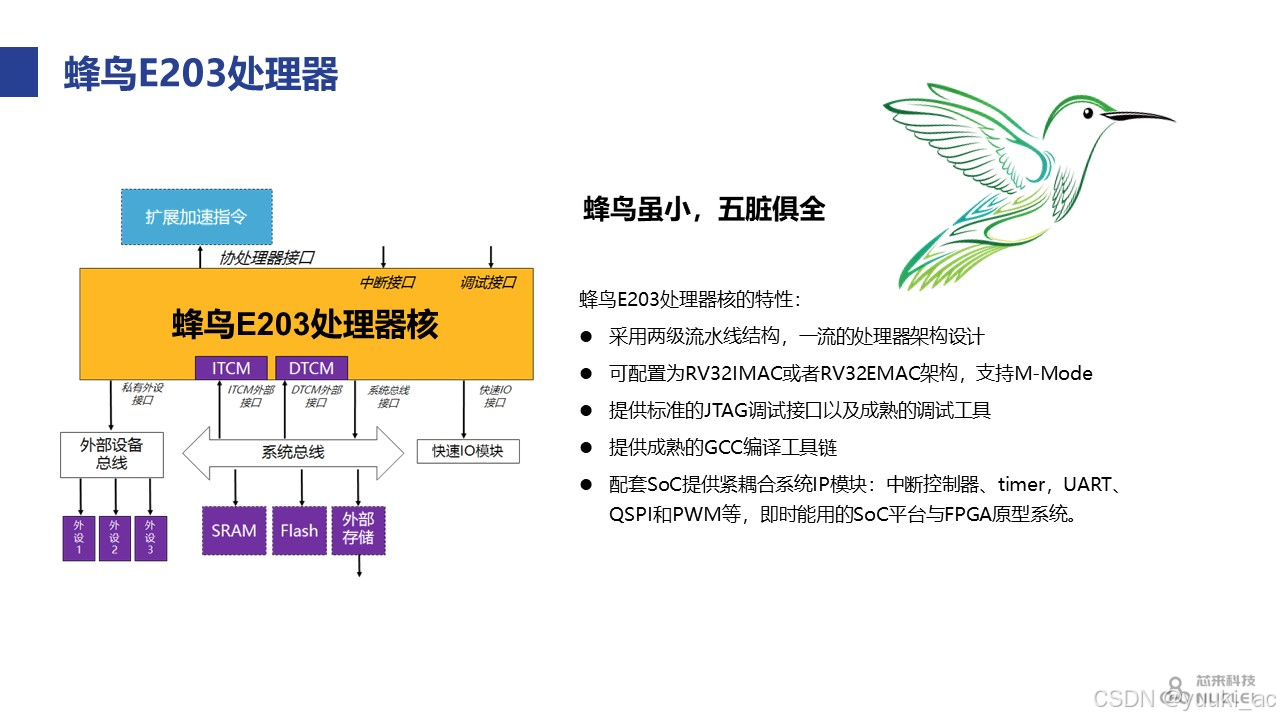

蜂鸟E203是一款由中国本土团队开发的开源RISC-V处理器内核,专为超低功耗与极小面积场景设计,适用于IoT设备、嵌入式系统及教育研究领域。

以下是其核心特点与架构的简要介绍:

1.1 设计目标与定位

- 能效比优化:通过两级流水线精简架构,实现了比同级ARM Cortex-M系列更优的功耗与面积表现。

- 开源属性:完整开放RTL代码(Verilog编写)及配套SoC,适合学术研究与爱好者学习,但未承诺商用质量。

1.2 架构特性

- 指令集支持:兼容RISC-V RV32I/E/A/M/C/F/D等子集,支持机器模式(Machine Mode Only)。

- 存储结构:

- 指令与数据分离的紧耦合存储(ITCM/DTCM),基于单周期SRAM实现,ITCM宽度64位以降低功耗。

- 支持系统总线、私有外设接口及快速IO接口,灵活配置地址空间。

1.3 开发与调试支持

- 工具链:提供成熟的GCC编译工具链和OpenOCD调试环境,支持Windows/Linux平台。

- 调试接口:集成标准JTAG接口,支持GDB交互调试(但暂不支持硬件断点与监视点)。

- 仿真验证:支持VCS+Verdi等工业级仿真工具,提供回归测试脚本与波形调试流程。

1.4 配套SoC与扩展性

- 系统集成:包含中断控制器、计时器、UART、QSPI、PWM等外设模块,形成“即用型”SoC平台。

- 扩展能力:支持协处理器接口(如NICE扩展),可连接AI加速器等自定义硬件模块。

2 开发环境

- 软件工具:Vmware Workstation 16pro、Vivado 2019.1、VCS、Verdi

- 操作系统:Centos(基于Linux)

- 工程源码:E203_ZYNQ_FPGA

3 移植思路

通过对比原Nuclei开发板(Artix-7)与ZYNQ7020的硬件差异,重点解决以下关键问题:

- 时钟架构重构:利用ZYNQ PS端PLL生成系统时钟

- 管脚约束设置:需要根据自己的开发板管脚定义重新设置约束文件

- JTAG调试:需要自行连接riscv调试器进行调试

- 脚本文件:重新设置脚本文件以支持新的开发板以及VCS+Verdi验证环境

4 准备工作

4.1 E203工程获取

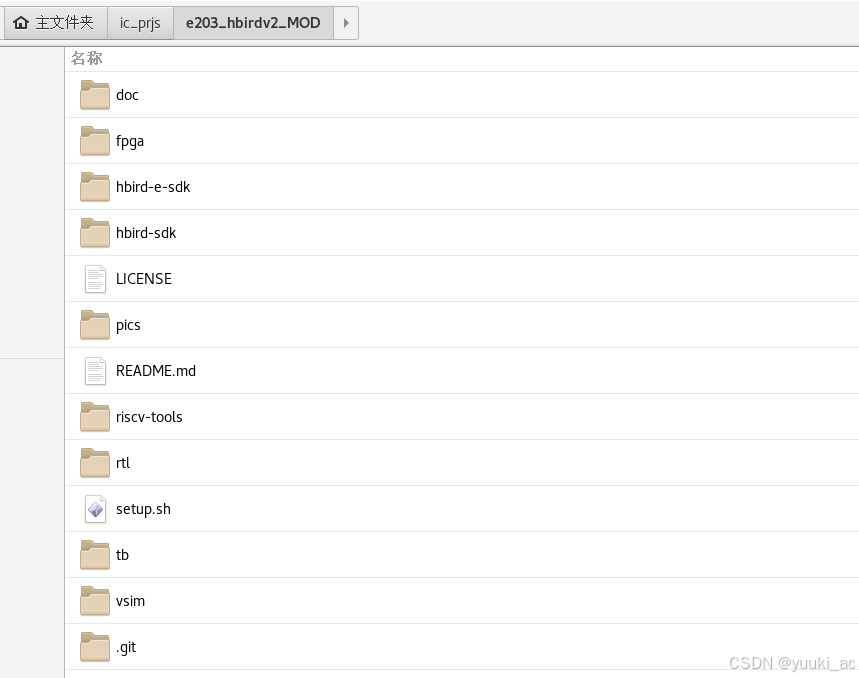

E203官方项目地址:e203_hbirdv2,在Github下载官方项目文件,其中,我们只需要用到的是rtl/e203下的RTL源码,FPGA工程中的相关脚本文件以及tb下的仿真文件。

git clone https://github.com/riscv-mcu/e203_hbirdv2.git当热,也可以直接进入E203_ZYNQ_FPGA ,其中已经上传了这个移植项目的所有RTL代码、约束文件、仿真文件以及vivado工程文件。

git clone https://github.com/ddd-yy/E203_ZYNQ_FPGA.git然后,配置好该项目需要用到的环境,即Centos系统、Vivado等。其中,关于Centos系统和相关编译工具链的环境具体教程如下:搭建IC_EDA虚拟机教程,其中已经安装好了我们需要的 Centos、Vivado 2019.1、VCS、Verdi以及E203工程所需的编译工具链环境。

关于E203工程的准备步骤也可以参考Nuclei官方的手册进行:Hummingbirdv2 E203

4.2 具体安装步骤

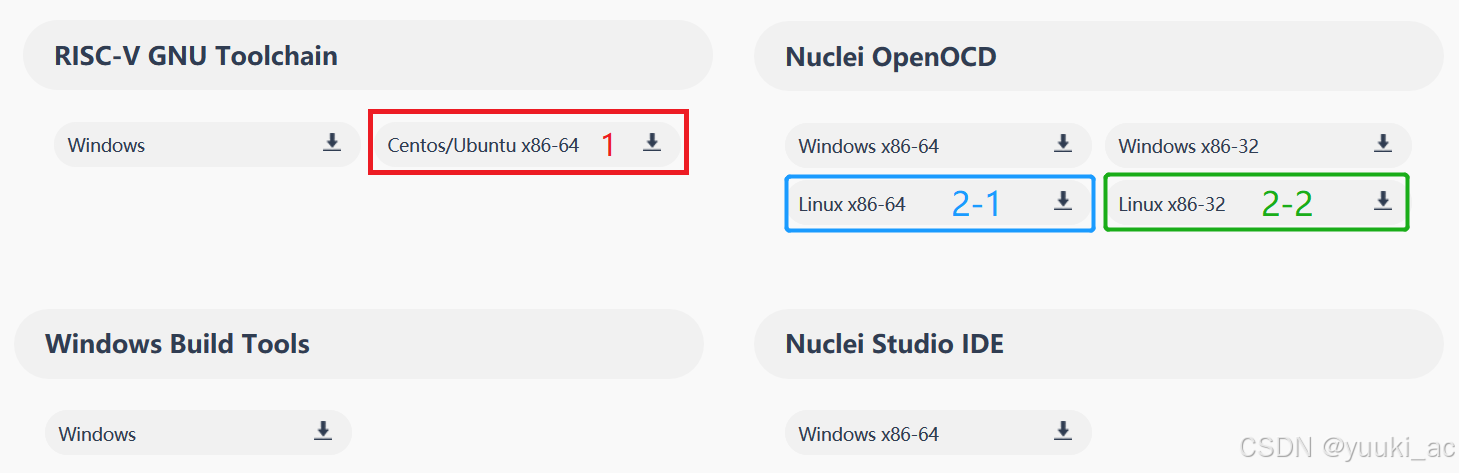

首先,在Linux系统中下载需要的工具:

sudo apt-get install autoconf automake autotools-dev curl device-tree-compiler libmpc-dev libmpfr-dev libgmp-devgawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev git然后在Nuclei官网:芯来工具链 下载riscv工具链:

然后解压文件,配置riscv-tools:

# 根据下载的文件名自行进行解压cp rv_linux_bare_9.21_centos64.tgz.bz2 ~/cd ~/tar -xjvf rv_linux_bare_9.21_centos64.tgz.bz2cd /mkdir -p ./riscv-tools/prebuilt_tools/prefix/bincd ./riscv-tools/prebuilt_tools/prefix/bin/ln -s ~/rv_linux_bare_19-12-11-07-12/bin/* .4.3 E203项目的目录结构

5 vcs+verdi仿真

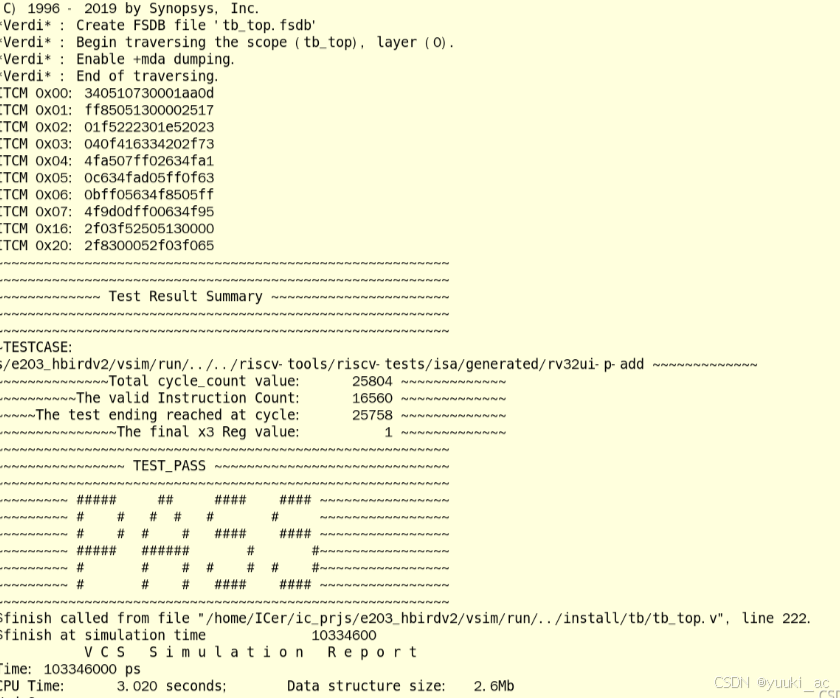

5.1 编译测试

在上一节中已经完成了工程的克隆以及工具链的配置,现在进行仿真,运行E203自带的测试用例。由于在实际工程上一般使用vcs+verdi仿真,而不是iverilog,因此,我们使用vcs+verdi,具体的EDA部署教程可以参考:Centos7安装EDA(vcs2018、verdi2018等

环境准备好之后,在对应目录下进行编译测试:

cd /riscv-tools/riscv-tests/isasource regen.sh在 /riscv-tools/riscv-tests/isa/generated 目录中,有预先生成的可执行文件。 如果测试代码有修改,需要使用上述命令可以重新生成可执行文件。

5.2 运行仿真

进入vsim目录下,通过仿真脚本进行仿真:

cd /vsimmake cleanmake install//-------------- For VCS:-------------//make compile SIM=vcsmake run_test SIM=vcs//-------------- For iVerilog:-------//make compile SIM=iverilogmake run_test SIM=iverilog

每次修改测试代码之后,都需要重新执行上述命令进行仿真。

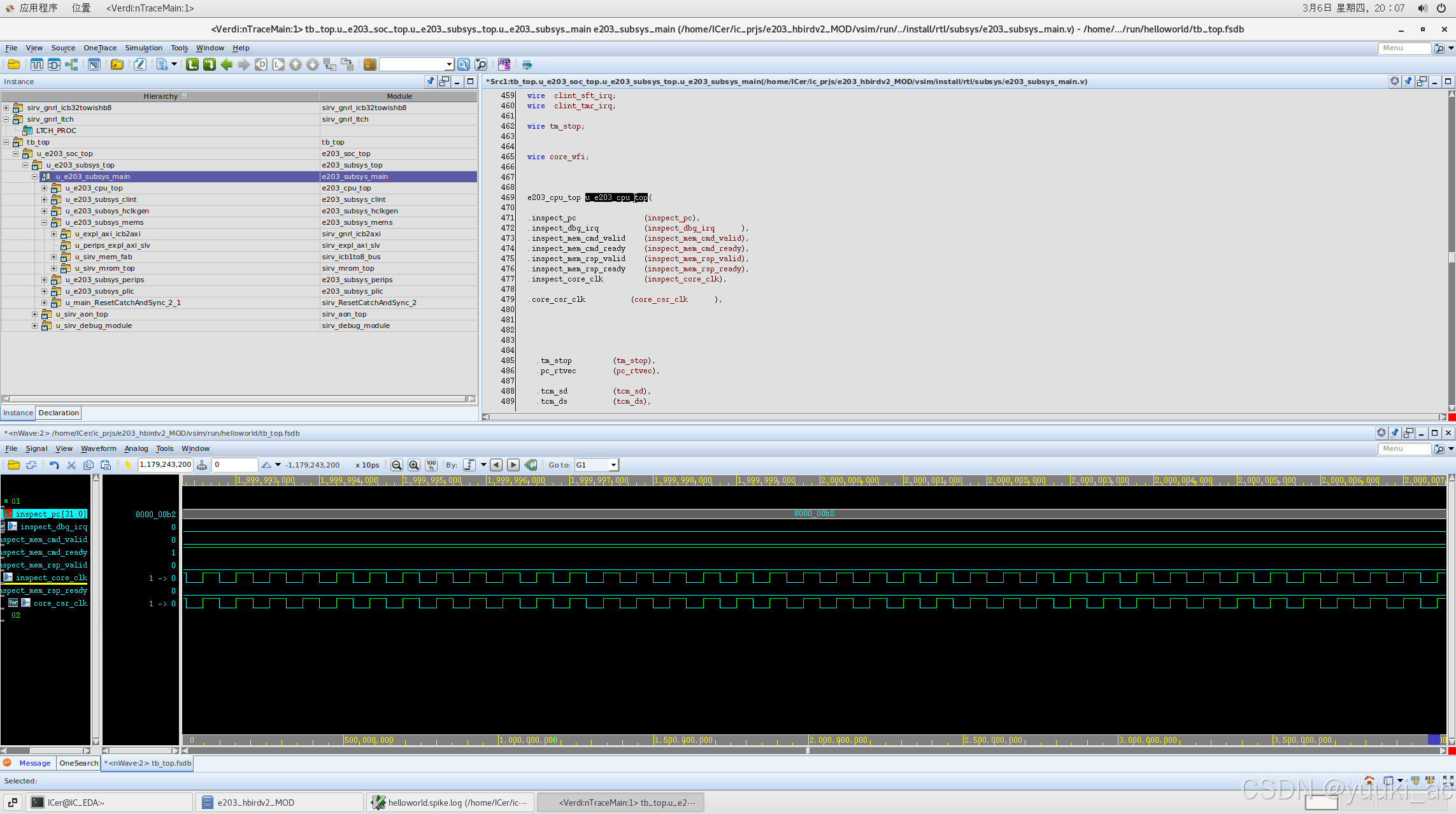

5.3 显示波形

运行以下命令展示仿真测试用例的波形图,我们选择Verdi:

//-------------- Using Verdi:-------------//make wave SIM=vcs//-------------- Using GTKWave:-----------//make wave SIM=iverilog波形图如下:

6 SDK测试

6.1 环境搭建

在 Nuclei工具下载官网 安装相应的openOCD工具,具体教程参考:使用 HBird SDK 进行开发

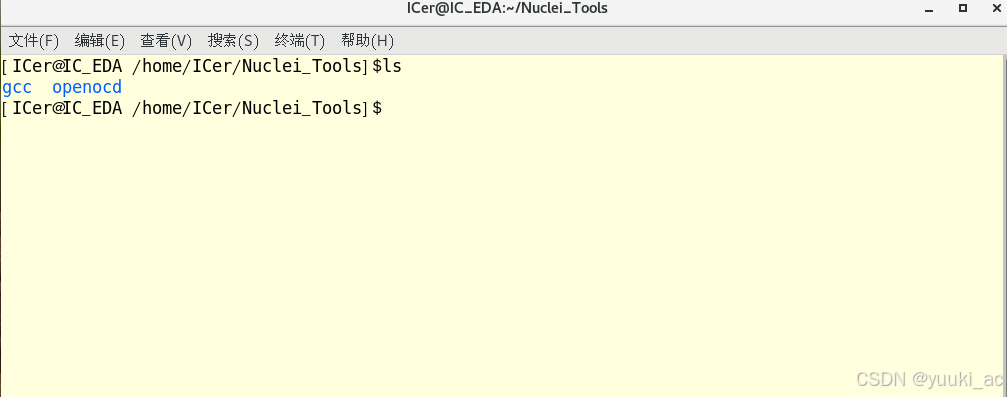

在 目录下创建 gcc、openocd 文件夹,解压相应的文件,根据官网教程放置到指定目录下。最后,nuclei-tools 目录结构如下:

6.2 获取SDK工程

在hbirdv2官方仓库中获取hbird-sdk源码:

git clone https://gitee.com/riscv-mcu/hbird-sdk.git设置SDK环境,进入到 /hbird-sdk目录下,新建setup_config.sh文件,并加入第三个命令(第三个是上面解压的两个文件,路径可以根据实际灵活修改)

touch setup_config.shg setup_config.shNUCLEI_TOOL_ROOT=/home/ICer/Nuclei_Tools6.3 编译SDK工程

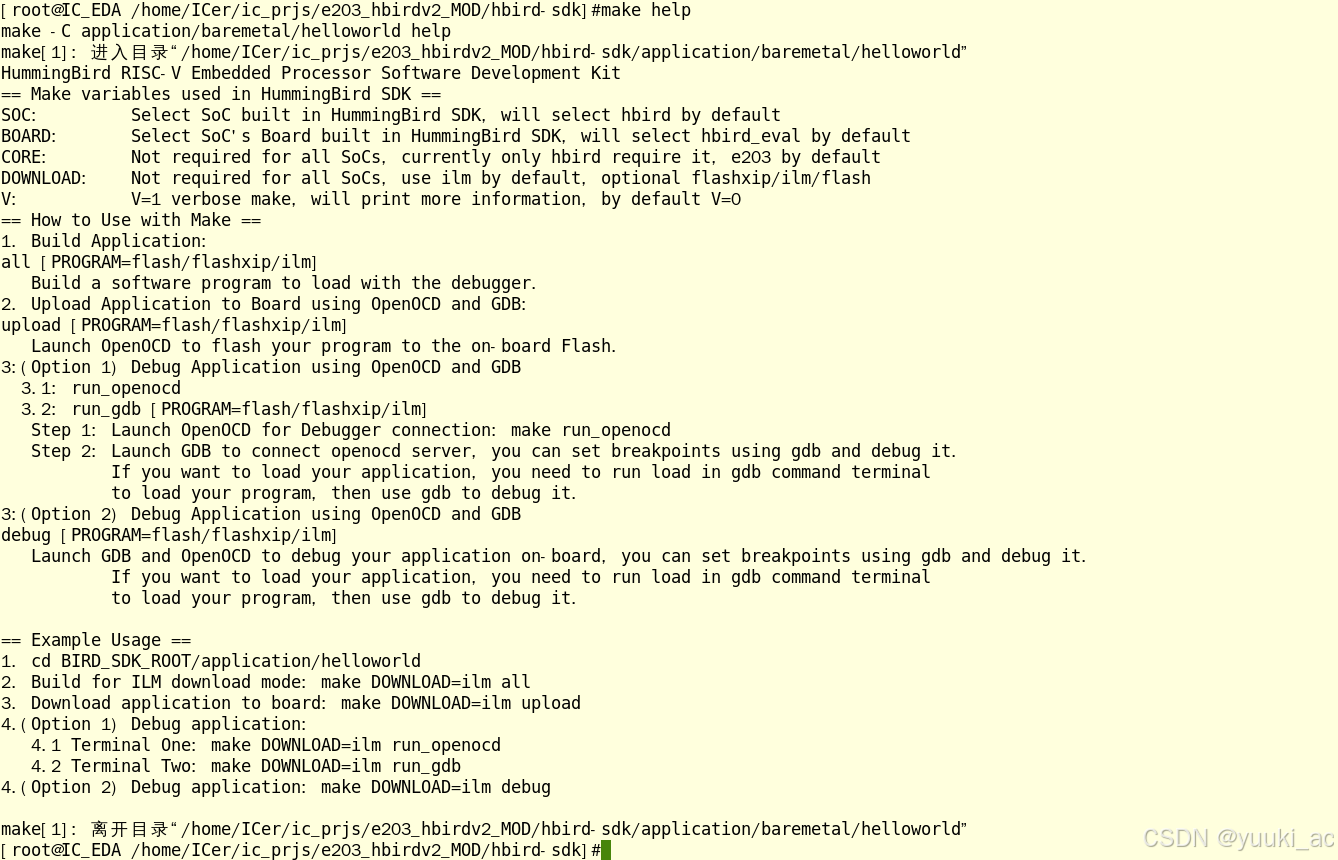

运行以下命令构建环境,每次执行SDK工程前都需要重新执行以下命令:

source setup.shecho $PATHwhich riscv-nuclei-elf-gcc openocd make rmmake help

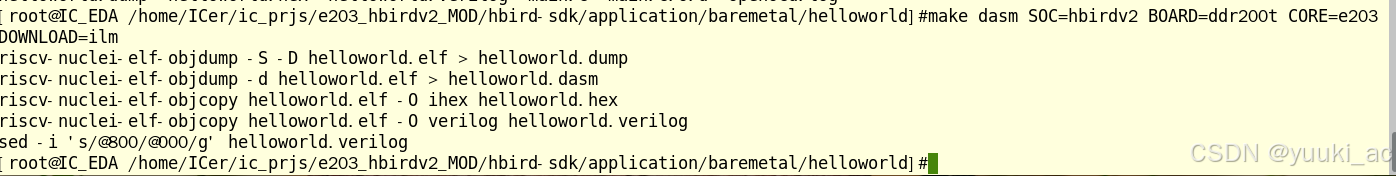

编译hello world demo,进入到 helloword目录,使用ilm模式编译:

cd application/baremetal/helloworld/make dasm SOC=hbirdv2 BOARD=ddr200t CORE=e203 DOWNLOAD=ilm6.4 SDK联合仿真

运行这两条命令后,可以上板测试,也可以让E203能够在软件仿真的环境下运行自己编写的C语言代码:

- 首先,hbird-sdk\\application\\baremetal目录下放置着一些测试程序,以helloworld为例。

- 复制helloworld目录为并取名为自定义的项目目录名hello_test,进入该目录下,修改makefile的内容,将 TARGET = helloworld 这一行内容的 “helloworld” 修改成自定义的项目名,如:mywork。

- 修改main.c函数的内容,将我们的应用程序文件放入该目录下。

- 运行 make dasm 这条命令,该命令将生成mywork.dasm、mywork.dump、mywork.verilog等新的文件,并将mywork.verilog文件复制到E203项目目录下的riscv-tools\\riscv-tests\\isa\\generated目录下。

- 进入E203项目目录下的vsim目录,运行 make run_test SIM=iverilog TESTNAME=mywork 命令即可。

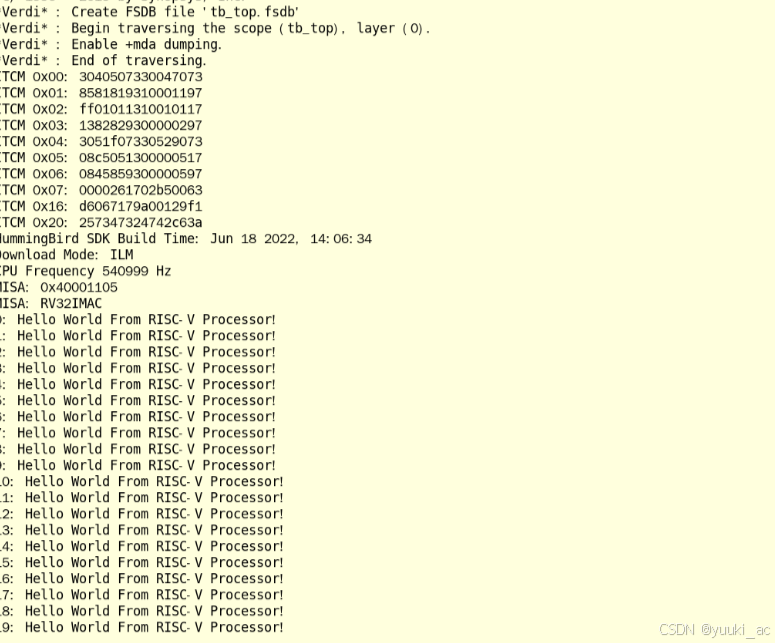

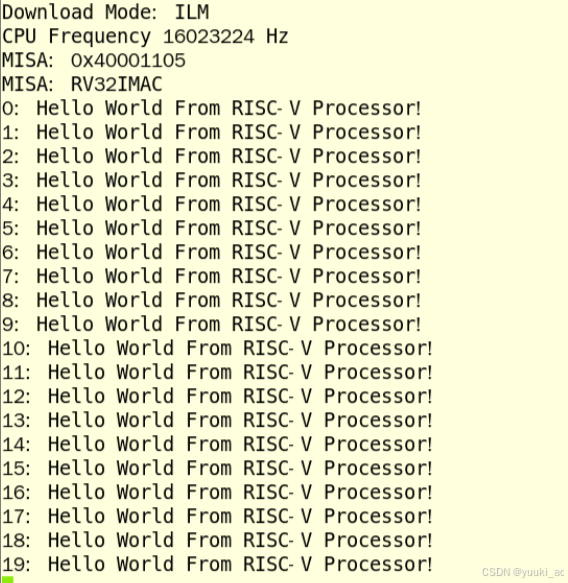

//-------------- For SDK:-------------//cd application/baremetal/mywork/make dasm SOC=hbirdv2 BOARD=ddr200t CORE=e203 DOWNLOAD=ilm//-------------- For VCS:-------------//cd /vsimmake cleanmake installmake compile SIM=vcsmake run_test SIM=vcsmake wave SIM=vcs示例输出:

6.5 修改ITCM和DTCM容量

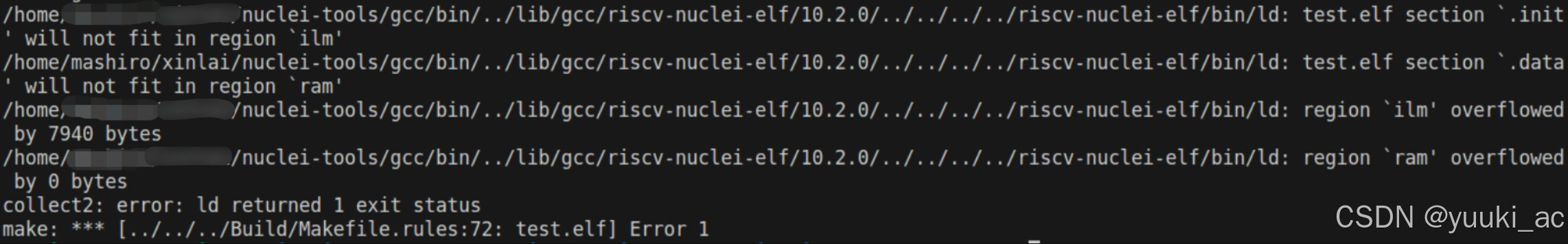

E203内核的DTCM和ICTM的默认配置为64KB的大小。但我们自己编写的应用程序可能因为代码量或者数据量过大,而导致指令或者数据无法完全放在ITCM或DTCM中,直接的表现是在用hbird-sdk生成.verilog文件时报错:

因此,我们需要根据需要对DTCM、ITCM的进行扩容,具体操作如下:

1) 修改vsim\\install\\rtl\\core下的config文件,将

`define E203_CFG_DTCM_ADDR_WIDTH 16`define E203_CFG_ITCM_ADDR_WIDTH 16修改成合适的大小。比如,如果想将DTCM扩展到256KB,则设置如下:

`define E203_CFG_DTCM_ADDR_WIDTH 18 // 2^18 = 2562) 由于扩容后的DTCM、ITCM的大小发生了变化,在运行仿真测试时,需要修改hbird-sdk生成测试代码的配置文件,即修改 hbird-sdk\\SoC\\hbirdv2\\Board\\ddr200t\\Source\\GCC 下的gcc_hbirdv2_ilm.ld文件,将:

ilm (rxai!w) : ORIGIN = 0x80000000, LENGTH = 64Kram (wxa!ri) : ORIGIN = 0x90000000, LENGTH = 64K修改成对应的大小。比如,如果想将DTCM扩展到256KB,则设置如下:

ilm (rxai!w) : ORIGIN = 0x80000000, LENGTH = 64Kram (wxa!ri) : ORIGIN = 0x90000000, LENGTH = 256K这样,就实现了仿真环境下E203的DTCM和ITCM的扩容。

3) 其他:在将E203综合到FPGA上时,由于FPGA的资源有限,如果设置的DTCM和ITCM的容量过大,可能会因为FPGA的资源不足而出现无法综合的问题。此外,如果综合成功,在使用NucleiStudio将应用程序下载到FPGA上时,同样要将NucleiStudio项目中的gcc_hbirdv2_ilm.ld文件修改成DTCM和ITCM内存大小的配置,才能让应用程序正常运行。

7 FPGA工程与上板调试

7.1 vivado综合

如果使用Nuclei官方的DDR200T开发板,那么就很容易执行FPGA,运行以下命令,然后连接开发板,上电测试即可:

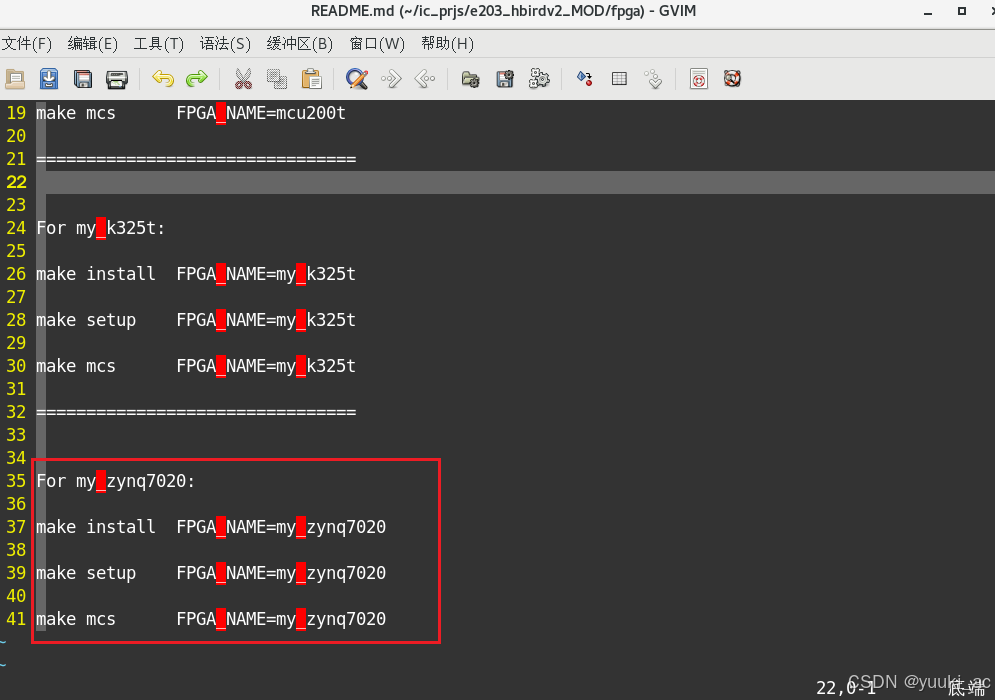

// 进入项目fpga目录cd /fpga// install 的文件夹,生成 FPGA bitstream 文件所需的所有 RTL 文件make install FPGA_NAME=ddr200t// 生成 bit 文件make bit FPGA_NAME=ddr200t// 生成 mcs 文件make mcs FPGA_NAME=ddr200t如果使用的其他型号的开发板,比如ZYNQ系列,那么需要新建工程,修改脚本文件以进行适配。进入到FPGA目录下,gvim打开 “README.md” 文件,文件里就是FPGA综合的命令,这里以ZYNQ7020为例:

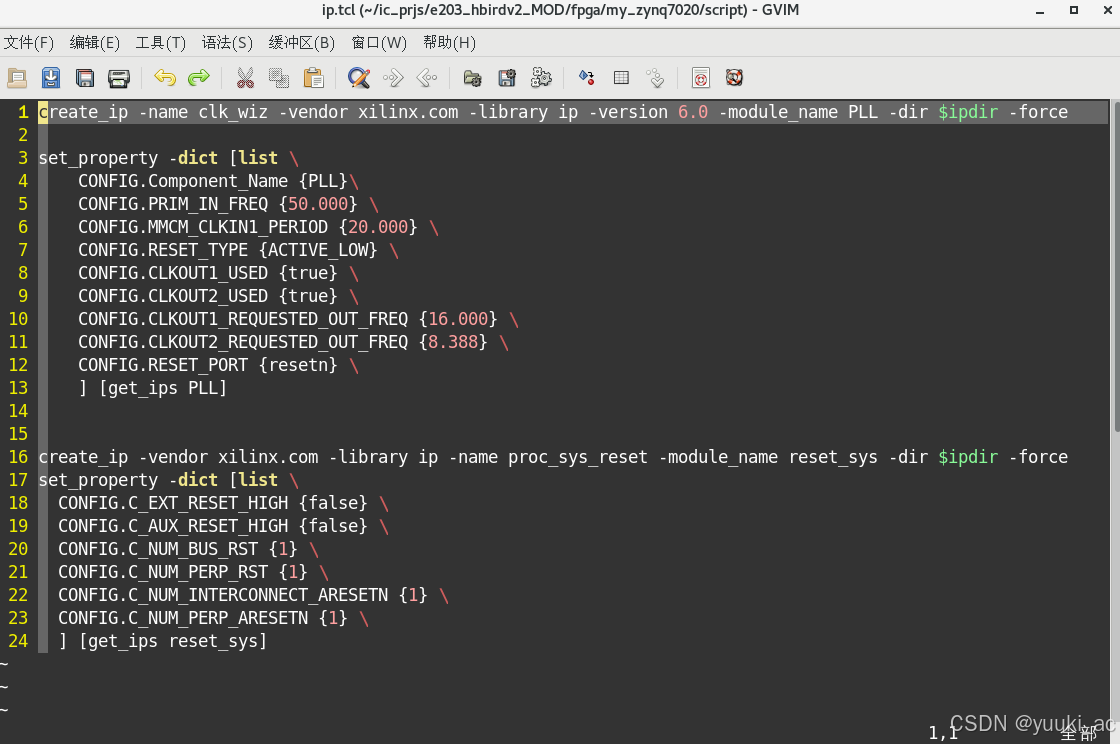

现在需要进行一些修改以适配ZYNQ。首先,我们需要进行相关脚本的修改,修改ip.tcl脚本,这个生成vivado的IP,我们需要配置clocking wizard IP输入时钟的属性:

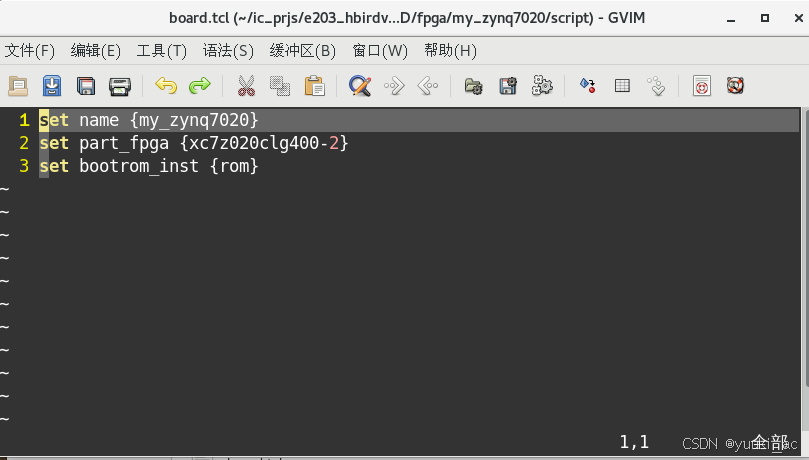

然后修改board.tcl脚本,如图,主要修改FPGA型号,其他脚本如果有board相关的全部注释掉:

依次执行以下命令,第二个直接使用 “setup” 可以打开Vivado的GUI,查看整个工程。

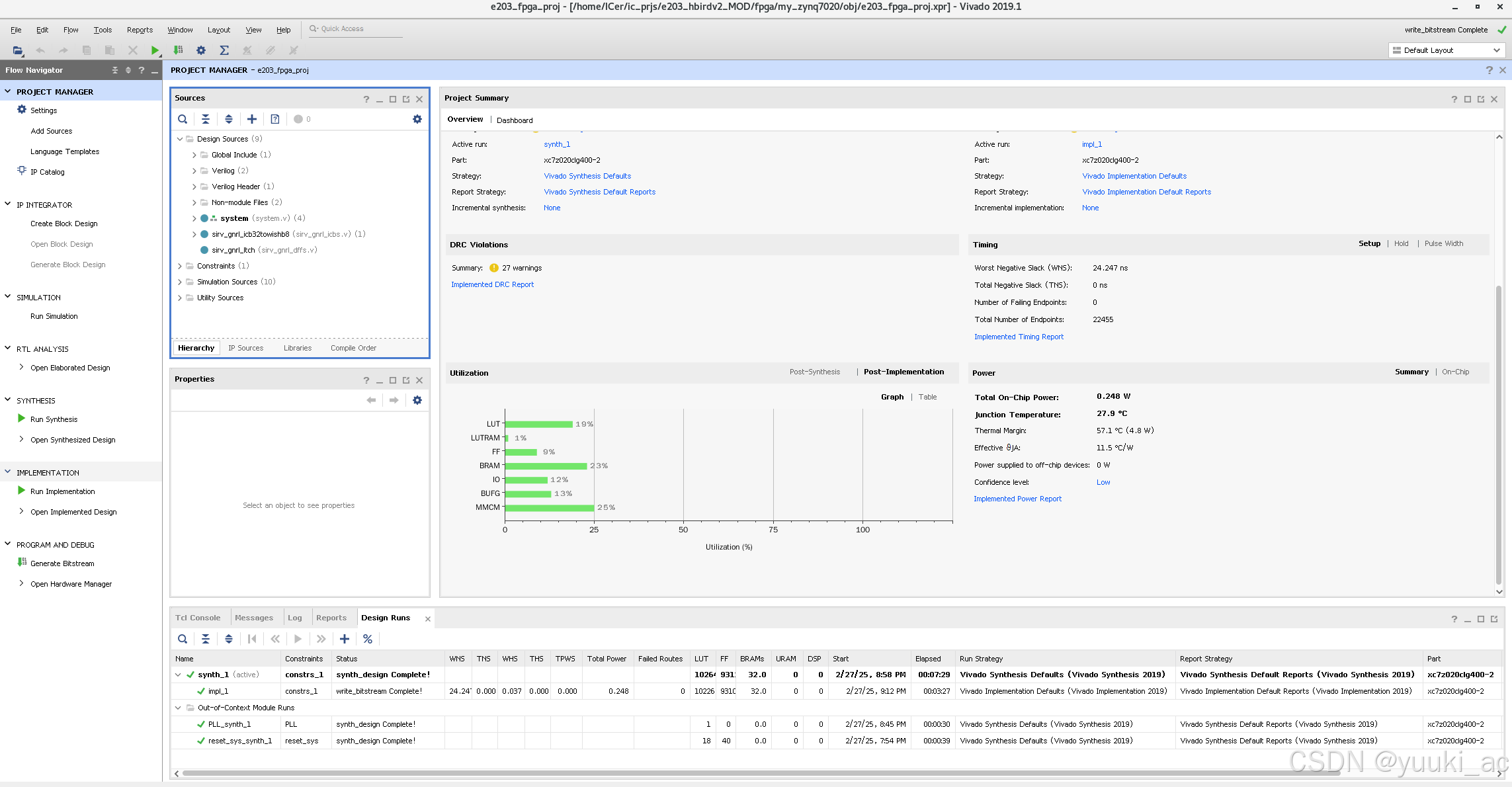

make install CORE=e203 FPGA_NAME=my_zynq7020 make setup CORE=e203 FPGA_NAME=my_zynq7020 关于E203的RTL代码中系统顶层文件的时钟、约束文件以及Vivado中相关IP的设置可以参考这个链接中的教程:E203 hbirdv2-ZYNQ7020-FPGA ,修改完成之后进行综合,综合结果如下:

7.2 上板调试

如果开发板是Nuclei官方的型号,上板调试的教程可以参考官方手册:使用 HBird SDK

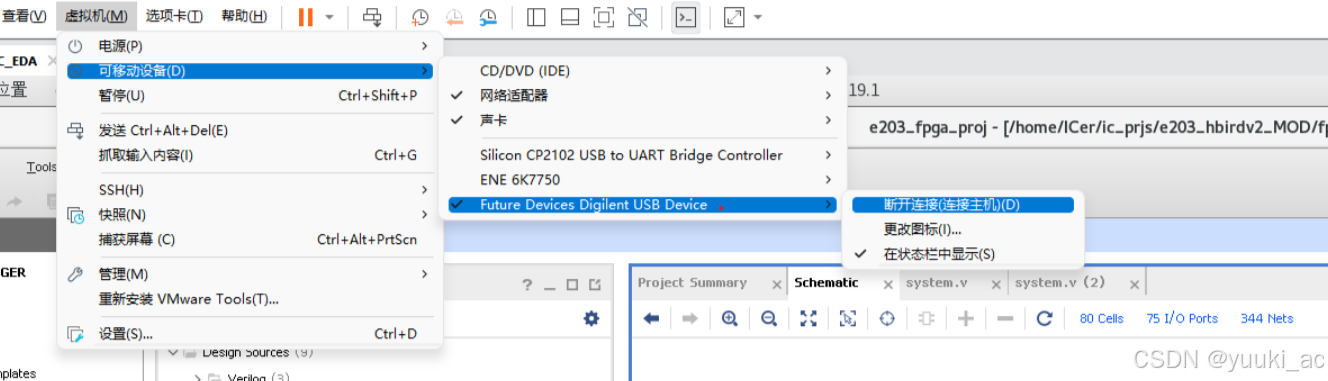

首先,要将jtag下载器设备连接到虚拟机,插入usb时会有窗口提示选择:

完成硬件连接后,使用以下命令检查 USB 状态:

lsusb // The example information displayed as below...Bus 001 Device 010: ID 0403:6010 Future Technology Devices International, Ltd FT2232xxxx使用以下命令设置 udev 规则,使这个 USB 可以被 plugdev 组访问:

sudo vi /etc/udev/rules.d/99-openocd.rules// Use vi command to edit the file, and add the following linesSUBSYSTEM==\"usb\", ATTR{idVendor}==\"0403\",ATTR{idProduct}==\"6010\", MODE=\"664\", GROUP=\"plugdev\"SUBSYSTEM==\"tty\", ATTRS{idVendor}==\"0403\",ATTRS{idProduct}==\"6010\", MODE=\"664\", GROUP=\"plugdev\"将当前用户加入plugdev:

whoami// Use above command to check your user name, assuming it is your_user_name// Use below command to add your_user_name into plugdev groupsudo usermod -a -G plugdev your_user_name//查询用户是否已经在 plugdev 组中groups若添加后提示该组不存在,则还需要继续设置。要新建plugdev,再次将所在用户添加到 plugdev 组中,重启一下,就可以查询用户是否已经在 plugdev 组中:

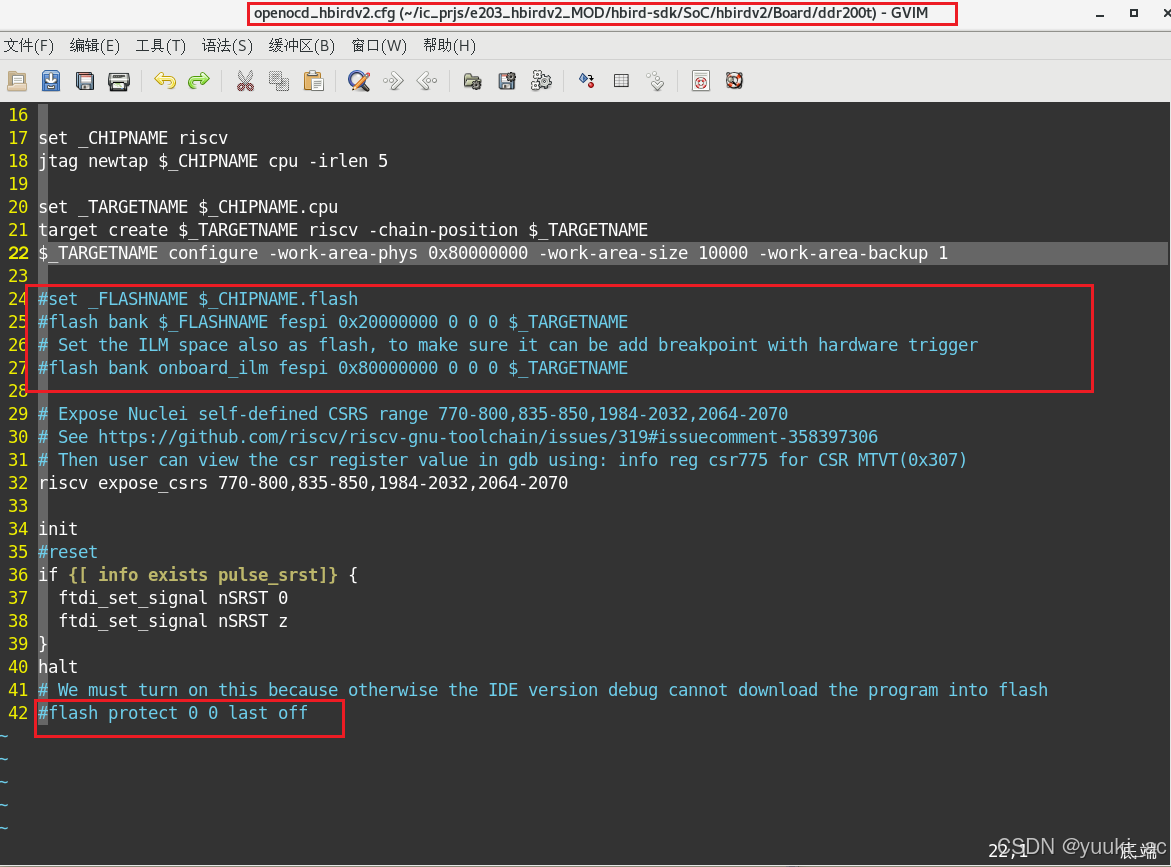

// 新建plugdevsudo groupadd plugdev// 将所在用户添加到 plugdev 组中sudo usermod -a -G plugdev your_user_name// 重启查询用户是否已经在 plugdev 组中groups // The example information showed as below after this command... plugdev ...// As long as you can see plugdev in groups, then means it is really belong to.ZYNQ开发板没有额外的Flash,因此只能将程序烧写到ROM中,所以使用 ilm模式,需要在相关目录下修改openocd_hbirdv2.cfg,将Flash相关全部注释掉:

使用以下命令编译和下载应用程序:

cd /application/baremetal/helloworldmake upload SOC=hbirdv2 BOARD=ddr200t CORE=e203 DOWNLOAD=flashHello World Demo 的功能是通过 UART 在 PC 的屏幕上打印一些信息,所以先准备好串口显示终端。使用第一个命令安装;使用第二个命令启动串口窗口。

sudo yum install screen // 安装串口sudo screen /dev/ttyUSB1 115200 // 打开UART终端重新烧写程序,查看打印的信息:

使用以下命令,可以编译应用程序并进入调试模式:

cd /application/baremetal/helloworldmake debug SOC=hbirdv2 BOARD=ddr200t CORE=e2038 参考链接

- OpenOCD调试官方文档教程:Introduction to OpenOCD

- Nuclei社区网站:RISC-V MCU中文社区

- Nuclei官方E203教程:Overview — Hummingbirdv2 E203

原创声明:本文为CSDN博主「yuuki_ac」原创文章,遵循CC 4.0 BY-SA版权协议

转载需附原文链接:蜂鸟E203 hbirdv2项目复现与FPGA开发【基于Linux】-CSDN博客