LP-MSPM0G3507学习--11ADC之二双通道高速DMA采样

关键函数:

DL_DMA_setSrcAddr():

DL_DMA_setDestAddr():

DL_DMA_setTransferSize():

DL_DMA_enableChannel():使能DMA传输

1.概述

DMA(Direct Memory Access)直接存储器存取,是一种实现高速存取数据的方法,配置好后,外设寄存器的数据可以不经CPU,自动搬运到指定存储器位置;指定存储器位置的数据,也可以不经过CPU,自动搬运到外设寄存器。

外设传输至存储器,多为Fixed address to Block address

存储器传输至外设,多为Block address to Fixed address

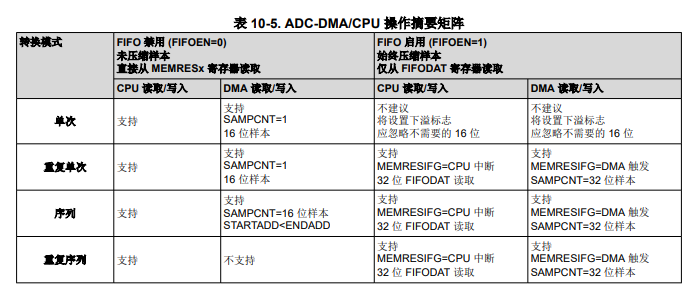

另外通常读取ADC转换数据是从Conversion Memory中读取的,而ADC包含一个可选的先入先出(FIFO)缓冲区,提供了另外一种方法来存储ADC结果的方式

从上表中可以看出,对于高速重复序列来说,必须启用FIFO

1.配置

ADC转换器选ADC1--PinMux peripheral and Pin Configuration

ADC 时钟源设为32MHz

Conversion Mode选sequence

两通道采用,因此Conversion Adderess设为1

使能repeat Mode--高速手动来不及

采样模式选自动

触发源选择software--通过精确计算采样时间,实现确定时间间隔采样,DMA会扮演触发的角色

Memory0配置为通道0/PA15,电压基准VDDA,采用时间源为 sampling Timer1

Memory1配置为通道0/PA156,电压基准VDDA,采用时间源为 sampling Timer1

高级配置中的分辨率设为12位,启动FIFO,掉电使能模式选择手动(Manual,选自动的话会自动掉电,导致无法实现高速度采样),期望采样时间分别为320ns、62.5ns,即采样率分别为1MHz,2MHz

采样率计算:

当时钟采用32MHz,选择12位模式时,转换阶段需要14个转换时钟周期,即转换时间为437.5ns,采样时间为62.5ns时,每一路总时长为500ns,即采样率为2MHz;当采样时间为320ns时,每一通道时长为757.5ns,约为1Mz;如采用1通道,想达到4MHz,必须提升频率,必然说时钟频率为80Mhz,则转换时间为175ns,采样时间可以为250-175=75ns

,