基于Verilog的SRIO在FPGA上的实现与测试

本文还有配套的精品资源,点击获取

简介:本文档集合了SRIO(Serial RapidIO)协议的测试案例,详细探讨了SRIO在FPGA上的实现。SRIO是一种高速串行总线技术,适用于高性能数据传输场景。文档中包含了使用Verilog硬件描述语言编写的SRIO实现代码,以及相关的测试平台和配置文件。这些资料将指导读者如何设计和验证SRIO协议在FPGA上的应用,包括协议的帧结构、仲裁机制、错误检测与恢复等关键细节。

1. SRIO总线技术概述

在现代信息技术和高速数据传输需求的推动下,SRIO(Serial RapidIO)总线技术凭借其高性能、低延迟、多带宽等优势成为众多设计者和开发者在通信、计算和存储系统集成中的首选。SRIO总线技术不仅仅是一种简单的总线标准,它是构建复杂系统内部或系统间通信的基石,能够实现模块之间的高速数据交换。

1.1 SRIO技术的起源与发展

SRIO起源于20世纪90年代末,最初由Motorola、IBM等公司共同开发,旨在提供一种能够在多处理器环境和高性能计算系统中广泛应用的互连技术。通过不断的发展和标准化,SRIO已成为一种开放的、非专有的、高性能的串行互连技术。

1.2 SRIO技术的关键特点

作为第三代总线技术的代表之一,SRIO具有以下特点: - 高性能 :支持高达10Gbps以上的数据传输速率,适合高速数据处理。 - 高可靠性 :提供多种错误检测和纠正机制,保障数据传输的准确性。 - 低延迟 :优化的协议设计使得系统内部通信的延迟非常低,提高了系统的响应速度。

在接下来的章节中,我们将详细探讨SRIO在FPGA中的实现方法,并通过Verilog语言实现SRIO协议的细节。此外,还会涉及SRIO的帧结构、仲裁机制和错误处理,以及测试平台的搭建和系统级集成等方面。通过逐步深入,让我们共同揭开SRIO技术的神秘面纱。

2. SRIO在FPGA中的实现方法

2.1 SRIO在FPGA实现的基础知识

2.1.1 SRIO接口的电气特性

串行RapidIO (SRIO) 接口作为一种高性能的互连协议,它的电气特性决定了其在FPGA中的实现方法。SRIO的电气特性包括了信号的电压等级、传输速率以及信号的摆率等参数。为了确保信号的完整性和高速传输的可靠性,SRIO接口使用低压差分信号技术(LVDS)来传输数据。

在FPGA设计中,这意味着需要特别关注FPGA的I/O模块。通常,FPGA提供专门的高速收发器(SerDes)模块用于支持LVDS信号。设计者必须根据SRIO的电气规格来配置这些模块,确保收发器能够在合适的速率下正常工作。

2.1.2 SRIO协议的层次结构

SRIO协议的层次结构与OSI模型相似,分为物理层、链路层、传输层和会话层。在FPGA实现中,我们通常关心的是物理层和链路层的实现,因为这两个层次直接关系到硬件设计和配置。

物理层定义了信号的电气特性和物理接口,链路层则负责数据的封装、错误检测和流控制。链路层为上层提供了可靠的数据传输服务,并通过特定的协议数据单元(PDU)来处理数据包。

2.2 SRIO接口的硬件设计

2.2.1 SRIO IP核的集成与配置

硬件设计阶段,开发者通常需要使用FPGA厂商提供的SRIO IP核,这是一种预先设计并经过验证的模块,可以在FPGA中直接使用。集成SRIO IP核涉及到许多硬件配置,包括端口数量、数据宽度、时钟设置等。

在Xilinx FPGA中,可以使用其提供的LogiCORE IP核作为参考。该IP核会包括一个参数化的设计,允许用户根据实际应用场景来调整。例如,用户可以指定设备ID、端口号以及传输速率等参数。

下面是一个简单的代码示例,展示如何在Vivado中初始化一个SRIO核:

# Vivado IP Integrator flowcreate_project -name \"srio_project\" -part \"xc7z020clg400-1\"create_ip -name \"srio_gen2_x1\" -vendor \"xilinx.com\" -library \"ip\" -version \"1.10\" -module_name \"srio_core\"# Generate output productsgenerate_target all [get_files srio_core.xci]update_ip_cache -module_name srio_core# Create an instance of the IP core in the projectcreate_ip_instance -name srio_core -module_name srio_core [current_fileset]# Set configuration propertiesset_property -name \"C_DEVICE_ID\" -value \"1\" -objects [get_ips srio_core]set_property -name \"C_DEVICE_VERSION\" -value \"1\" -objects [get_ips srio_core]set_property -name \"C_LC_LINK_WIDTH\" -value \"x1\" -objects [get_ips srio_core]# ...additional configurations# Run synthesislaunch_runs synth_1 -jobs 8wait_on_run synth_12.2.2 SRIO接口的信号完整性分析

在硬件设计完成之后,信号完整性分析是不可或缺的一环。SRIO接口由于其高速特性,对信号的完整性非常敏感。信号完整性问题包括反射、串扰、抖动和电磁干扰等,这些问题可能导致数据传输错误,影响整个系统的稳定性和性能。

对于FPGA设计来说,可以使用相应的EDA工具(如Cadence Sigrity)来执行信号完整性分析。设计者需要检查布线的拓扑结构、阻抗匹配、终端匹配等,并可能需要在FPGA引脚上添加一些特定的电路元件,比如匹配电阻、电容,来减少反射和噪声。

2.3 SRIO接口的FPGA编程实践

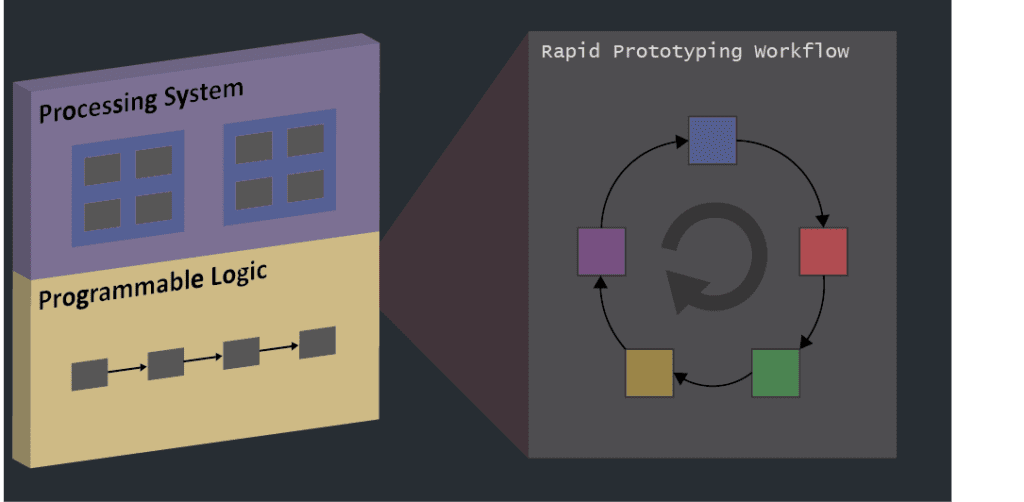

2.3.1 FPGA设计流程概述

在FPGA中实现SRIO接口,通常遵循以下设计流程:

- 需求分析:明确SRIO接口所需满足的功能、性能指标以及与其他模块的交互方式。

- IP核集成:根据需求选择合适的SRIO IP核,并在FPGA设计环境中进行集成和初步配置。

- 硬件设计:对SRIO IP核的信号进行布线、时钟分配以及必要的约束设置。

- 功能仿真:通过仿真工具验证SRIO接口的功能是否符合预期。

- 实现与布局布线:完成综合、布局布线等步骤,生成用于编程FPGA的比特流。

- 硬件测试:将设计下载到FPGA开发板上进行实际测试,确保在真实硬件环境中的性能和稳定性。

2.3.2 FPGA时序约束与优化技巧

为了确保SRIO接口在FPGA中能够稳定工作,时序约束是一个关键环节。正确的时序约束可以指导FPGA的实现工具在布局布线时遵循特定的时序要求。

针对SRIO接口,设计者通常需要设置输入和输出延迟约束,以确保信号在SRIO核内部正确同步。此外,对于高速信号,还需要特别注意建立时间和保持时间的约束,避免数据在寄存器之间的时序问题。

以下是时序约束的一个示例:

# Create a custom timing constraint for SRIO pinscreate_clock -name {srio_ref_clk} -period 10.0 [get_ports {srio_ref_clk_p}]set_input_delay -clock {srio_ref_clk} -max 2.0 [get_ports {srio_data_in_p}]set_input_delay -clock {srio_ref_clk} -min -0.5 [get_ports {srio_data_in_p}]set_output_delay -clock {srio_ref_clk} -max 2.5 [get_ports {srio_data_out_p}]set_output_delay -clock {srio_ref_clk} -min -0.8 [get_ports {srio_data_out_p}]在时序优化阶段,FPGA设计者需要关注关键路径上的逻辑优化。比如,可以使用流水线技术来分散逻辑延迟,从而提高时钟频率。同时,对于SRIO这类高速接口,还应该考虑信号的传输延迟,确保时序的余量。

# Example of pipelining a critical path# Let\'s assume we have a design with a long combinational path# We will add a register to break this pathcreate_generated_clock -name {clk_div} -source [get_pins {flipflop/Q}] -divide_by 2 [get_ports {clk}]以上内容涵盖从基础电气特性到硬件设计和编程实践的各个细节,体现了SRIO在FPGA中实现的复杂性和专业性。随着FPGA技术的不断发展,对高性能通信接口的需求日益增加,掌握SRIO技术是提升FPGA应用能力的重要途径。

3. Verilog语言在SRIO实现中的应用

3.1 Verilog语言基础

3.1.1 Verilog语法入门

Verilog语言是硬件描述语言(HDL)的一种,它能够让我们在高层次上描述电子系统的结构和行为。在SRIO实现中,Verilog被用来编写可综合的硬件代码,进而通过FPGA实现具体的硬件功能。

一个基本的Verilog代码模块通常包含以下几个部分:模块定义、输入输出声明、模块体。一个简单的模块定义示例如下:

module simple_module( input wire a, input wire b, output wire sum); assign sum = a + b; // 简单的加法器endmodule 在上面的代码中,我们定义了一个名为 simple_module 的模块,它有两个输入 a 和 b ,以及一个输出 sum 。我们使用了Verilog中的 assign 语句来描述硬件的行为,此处即实现了一个简单的线性加法器。

3.1.2 Verilog的数据类型和运算符

Verilog提供了多种数据类型来描述硬件结构。最基本的数据类型包括 wire 和 reg ,其中 wire 类型用于组合逻辑,而 reg 类型用于时序逻辑。此外,还有 integer 、 real 、 time 等类型,以及由这些基础类型构成的数组和向量。

运算符方面,Verilog提供了逻辑运算符、算术运算符、关系运算符、位运算符等。如 & 代表按位与运算, + 代表加法运算。

3.2 Verilog在SRIO设计中的角色

3.2.1 SRIO协议的Verilog实现要点

为了在FPGA中实现SRIO协议,需要对协议进行适当的简化和硬件优化。Verilog在这里的作用是将复杂的协议规则转换成可以通过FPGA硬件实现的结构。要点包括:

- 状态机设计 :SRIO协议需要清晰的状态机来管理不同的事务状态和转换逻辑。

- 时序控制 :由于SRIO是高速串行接口,对时序要求极为严格,需要精心设计时序逻辑,确保数据完整性和传输效率。

- 资源优化 :在有限的FPGA资源下,优化实现以减少逻辑单元和存储器资源的使用。

3.2.2 Verilog代码的模块化设计

为了便于维护和复用,Verilog代码应该模块化设计。每个模块实现一个功能,模块之间通过接口进行通信。模块化设计有助于:

- 代码复用 :功能相同的模块可以被不同项目重用。

- 易于测试 :模块化设计使得单独测试每个模块成为可能。

- 系统集成 :模块之间清晰的接口定义有助于系统集成。

3.3 Verilog的高级应用技巧

3.3.1 状态机的设计和应用

状态机是描述协议或系统行为的关键。在SRIO实现中,状态机用于控制数据包的发送与接收,以及协议状态的转换。

module state_machine( input clk, input reset, input start, input [3:0] state_in, output reg [3:0] state_out);always @(posedge clk or posedge reset) begin if (reset) begin state_out <= 4\'b0000; // 初始状态 end else begin case (state_in) 4\'b0001: state_out <= 4\'b0010; 4\'b0010: state_out <= 4\'b0100; // 其他状态转换逻辑 default: state_out <= 4\'b0000; endcase endendendmodule 在上述代码中,我们定义了一个简单的状态机,根据输入 state_in 的值来更新输出状态 state_out 。通过适当设计状态转换逻辑,可以实现复杂的状态转换。

3.3.2 仿真测试与调试方法

仿真测试是验证硬件设计正确性的重要步骤。使用Verilog编写测试平台(Testbench),可以在没有实际硬件的情况下对设计进行仿真和测试。

module testbench;reg clk;reg reset;reg start;wire [3:0] state_out;state_machine uut ( .clk(clk), .reset(reset), .start(start), .state_out(state_out));initial begin clk = 0; reset = 1; start = 0; #100; reset = 0; #100; start = 1; #500; $finish;endalways #5 clk = ~clk; // 产生周期为10个时间单位的时钟信号endmodule 上述测试平台生成了一个时钟信号和复位信号,并在特定时间点改变 start 信号的值,用于触发状态机的转换。通过观察输出 state_out ,可以验证状态转换是否正确。如果结果与预期不符,需要调整设计代码并重新仿真。

在实际工作中,除了手动编写测试平台,还可以使用仿真工具如ModelSim进行更高级的测试,例如系统级仿真和波形分析等。此外,现代FPGA开发环境中集成了许多诊断和调试工具,如逻辑分析仪和信号探针,这些工具可以帮助开发者深入了解FPGA内部信号的行为。

4. SRIO协议的帧结构和工作原理

4.1 SRIO协议的基本概念

4.1.1 SRIO协议的分层模型

SRIO(Serial RapidIO)协议是一种高速串行通信协议,广泛应用于高性能计算机系统和嵌入式系统中,特别是在FPGA(现场可编程门阵列)设备中。它具有低延迟、高带宽和可扩展性强的特点。

SRIO协议的分层模型主要由物理层(PHY)、链路层和传输层组成,如下图所示:

graph LR A[应用层] -->|封装数据| B[传输层] B -->|封装数据包| C[链路层] C -->|封装帧| D[物理层] D -->|串行化| E[物理介质] E -->|反串行化| D D -->|解析帧| C C -->|解析数据包| B B -->|解析数据| A- 物理层(PHY) :这是SRIO协议最底层,负责物理介质上的信号传输。物理层协议定义了电气特性、信号编码方式和信号的物理接口等。

- 链路层 :链路层处理数据的帧结构和流量控制。它确保数据包的有效传输,并提供错误检测和纠正机制。

- 传输层 :传输层定义了数据包的传输机制,包括事务请求、响应和事务的优先级管理。

4.1.2 SRIO的事务类型与特性

SRIO协议定义了多种事务类型来满足不同的数据传输需求:

- 读事务 :数据源设备向数据目的地设备请求数据的过程。

- 写事务 :数据源设备向目的地设备发送数据的过程。

- 读响应事务 :目的地设备向数据源设备返回请求的数据。

- 消息事务 :用于传输控制信息或者其它不需要返回数据的通信。

这些事务类型允许SRIO在不同的工作模式下高效运行,如请求响应模式、广播模式以及流模式。

4.2 SRIO的帧结构详解

4.2.1 数据帧的组成与格式

数据帧是SRIO协议中最核心的部分,它包含了必要的控制信息和数据负载。数据帧的主要组成部分包括:

- 开始分隔符(Start Delimiter) :标志一个帧的开始。

- 目的ID和源ID :标识数据帧的目标和源设备。

- 事务类型 :指示这个帧的事务类型。

- 序列号 :用于数据帧的排序和重发确认。

- 地址信息 :如果这是一个读或写请求,包含目标地址信息。

- 长度信息 :指示数据负载的大小。

- 数据负载 :实际传输的数据内容。

- 校验和 :用于错误检测。

数据帧格式通常以二进制形式表示,如下是一个简化的SRIO数据帧结构的例子:

+---------------+---------------+-------------+------------+----------+----------+-----------+| Start Delim. | DestinationID | SourceID | Transaction| Seq. No. | Address | Length || | | | Type | | Length | |+---------------+---------------+-------------+------------+----------+----------+-----------+| Data | Checksum | End Delim. | | | | |+---------------+---------------+-------------+------------+----------+----------+-----------+4.2.2 控制帧的作用与处理

控制帧用于SRIO链路的建立、管理和维护。它不包含数据负载,主要用于链路的初始化、错误恢复以及流控制等功能。控制帧可以是:

- 初始化帧 :用于链路双方初始化时的参数交换。

- 空闲帧 :当没有数据传输时,链路通过发送空闲帧来保持同步。

- 流控制帧 :用于告诉对方设备当前接收窗口的状态,以避免缓冲区溢出。

控制帧的处理通常需要硬件层面的支持,例如FPGA中的SRIO IP核会内置这些处理逻辑。

4.3 SRIO的工作原理与流程

4.3.1 数据传输过程分析

数据在SRIO协议中通过帧的形式进行传输。当一个源设备需要发送数据到目标设备时,它将数据封装成数据帧,并将其通过物理层发送出去。目标设备接收到数据帧后,通过链路层和传输层对帧进行解析,并将数据传递给应用层。

数据传输过程中的关键点包括:

- 帧封装 :数据被封装成符合SRIO格式的帧。

- 信号传输 :封装好的帧通过物理层进行信号的串行化和发送。

- 帧接收 :目标设备接收信号,并通过物理层进行反串行化和解码。

- 帧解析 :链路层和传输层解析帧内容,并将数据传递给上层。

4.3.2 流控制机制和时钟域交叉

为了保证数据的正确传输,SRIO协议采用了复杂的流控制机制。流控制机制允许数据传输在不丢失数据的情况下进行,主要方式包括:

- 反压机制 :当接收方的缓冲区即将满时,通过反压信号告知发送方减缓发送速度。

- 流量控制帧 :通过发送特定的控制帧,通知对方设备当前的流量控制状态。

此外,由于SRIO可能涉及多个时钟域,因此必须处理好时钟域交叉问题。这通常涉及到:

- 双缓冲机制 :使用两个缓冲区进行数据传输,一个缓冲区在接收数据时,另一个缓冲区在读取数据。

- 异步FIFO :在不同时钟域间使用异步的先进先出队列来缓冲数据。

以上描述了SRIO协议的帧结构和工作原理的基本内容,通过深入分析SRIO的物理层、链路层和传输层的交互,我们可以更好地理解其在FPGA和高性能计算系统中的应用。在下一节中,我们将探讨SRIO的仲裁机制和错误处理,进一步深化对SRIO协议工作的理解。

5. SRIO协议的仲裁机制和错误处理

5.1 SRIO的仲裁机制

5.1.1 仲裁算法的原理与实现

在分布式系统中,多主机环境下的设备间通信需要有效的仲裁机制来保证数据传输的有序性。SRIO协议通过内置的仲裁算法,管理多个节点在同一时间对共享通信资源的访问需求。SRIO协议的仲裁机制主要通过以下步骤实现:

- 请求阶段 :在这一阶段,所有的SRIO节点同时将它们想要传输数据的请求发送到仲裁器。

- 仲裁决策 :仲裁器根据预设的算法来决定哪个节点的请求将被优先处理。

- 授权阶段 :仲裁器通过仲裁响应信号告知各个节点,它们的请求是否被授权。

- 传输阶段 :被授权的节点将数据传输到目标节点,未被授权的节点等待下一轮仲裁。

在SRIO中,仲裁算法的设计需要考虑到公平性和效率。一个常见的仲裁策略是轮询(Round Robin)算法,它保证每个节点公平地获得访问资源的机会。除了轮询,也可以使用优先级仲裁(Priority Arbitration),通过设定节点优先级来决定访问顺序,或者使用预分配的仲裁策略,根据历史使用情况动态调整资源分配。

5.1.2 仲裁策略对性能的影响

仲裁策略的选取直接影响着整个系统的性能。例如:

- 公平性 :在系统资源有限时,采用高公平性的仲裁策略可以确保没有节点长时间被忽略,但这可能导致短时延迟较高。

- 效率 :如果系统需求中对实时性要求高,则优先级仲裁可能更为合适,尽管它可能会导致某些节点饥饿(长时间得不到服务)。

合理设计仲裁策略需要仔细考虑应用场景的特征,例如数据的实时性要求、网络负载状况、节点的接入数量等。例如,在实时性要求高的环境下,可以通过动态调整优先级来提高对关键任务的响应速度。

5.2 SRIO的错误检测与处理

5.2.1 错误检测机制的类型与原理

SRIO协议实现了一套全面的错误检测和纠正机制,以确保数据传输的可靠性。SRIO协议采用了以下几种错误检测机制:

- 奇偶校验 :通过在数据帧中加入奇偶校验位,接收方可以检测到单比特错误。

- 循环冗余检验(CRC) :通过使用CRC码,可以检测出帧内多个比特的错误。

- 序列号 :使用序列号确保帧的顺序正确,检测和纠正帧的丢失、重复或乱序。

- 流量控制 :通过流量控制机制避免缓冲区溢出,防止数据丢失。

每种机制都有其特定的检测范围和局限性,它们通常结合使用,以实现更高层次的错误检测。在实际应用中,开发者需要根据具体需求选择合适的错误检测机制,比如对于关键任务,可能需要更严格的CRC检测以确保数据完整。

5.2.2 错误恢复流程与策略

当SRIO检测到传输错误时,错误恢复流程便启动。基本的错误恢复步骤如下:

- 错误检测 :接收方通过奇偶校验、CRC或序列号检测出错误。

- 错误通知 :接收方发送错误通知给发送方,表明错误已检测到。

- 重传 :发送方接收到错误通知后,将重新发送错误的帧。

- 错误报告 :错误帧被记录在日志中,供后续分析。

在设计错误恢复策略时,重要的是要平衡系统的可靠性和性能。对于错误恢复,可以采用以下策略:

- 即时重传 :在检测到错误后立即重传,以减少等待时间。

- 延时重传 :给予系统一些时间来处理潜在的临时错误,避免不必要的重传。

- 重传次数限制 :为了防止系统陷入无限重传,需要对重传的次数进行限制。

此外,对于复杂系统来说,实现健壮的错误恢复策略需要对错误日志进行深入分析,优化算法,并在必要时进行软件或硬件的升级。

6. ```

第六章:SRIO测试平台的建立和使用

6.1 测试平台的需求分析

在测试SRIO平台之前,首先要进行需求分析,以确保测试覆盖所有相关的功能和性能指标。

6.1.1 功能测试与性能测试的分类

功能测试关注于SRIO协议实现的功能完整性,包括但不限于初始化、数据传输、流控制、错误处理等。性能测试则关注于在不同的工作负载和条件下,SRIO的传输速率、延迟、吞吐量等性能指标。

功能测试案例

- 初始化测试:验证SRIO链路建立和断开的过程是否符合规范。

- 数据传输测试:确保数据包的完整性和正确性,包括数据包的顺序和丢包情况。

- 流控制测试:模拟高负载条件下的流控制响应,以测试系统的稳定性。

- 错误处理测试:故意引入错误情况(如CRC校验失败)来验证错误检测和恢复机制是否有效。

性能测试案例

- 压力测试:逐步增加数据传输负载,直至找到系统的极限性能。

- 吞吐量测试:测量在特定条件下,SRIO链路能够处理的最大数据量。

- 延迟测试:在不同的负载条件下,测量数据包从发送到接收的总延迟。

6.1.2 测试用例的设计原则

设计测试用例时,应确保覆盖所有关键场景,并具有足够的变化和随机性以发现潜在问题。

测试用例设计原则

- 完整性原则:测试用例需要全面覆盖SRIO协议的所有功能。

- 可重复性原则:测试过程和结果应可重复,确保稳定性和可靠性。

- 独立性原则:每个测试用例应独立于其他用例,避免相互影响。

- 可维护性原则:随着SRIO协议的更新和变化,测试用例应易于更新和维护。

6.2 测试平台的搭建与运行

搭建测试平台是进行SRIO测试的重要步骤,确保平台稳定性和易用性对测试结果的准确性至关重要。

6.2.1 测试环境的配置方法

测试环境应该模拟真实的工作场景,包括硬件和软件的配置。

硬件配置

- FPGA开发板:应该选用支持SRIO接口的FPGA开发板。

- 连接线和接口:确保使用符合SRIO电气特性的连接线和接口。

软件配置

- SRIO驱动和固件:根据硬件平台的需要,安装最新的SRIO驱动和固件。

- 测试软件:安装或开发能够执行测试用例的软件,包括发送和接收数据、控制测试流程、记录和分析测试结果等。

6.2.2 测试过程的监控与日志分析

测试过程中的监控和日志记录对于后续问题定位和优化至关重要。

监控与日志分析流程

- 实时监控:实时监控测试过程中的关键性能指标,如传输速率、错误率等。

- 日志记录:详细记录测试过程中的每个事件,包括成功和失败的案例。

- 异常检测:及时发现异常情况并记录相关数据,便于后续问题分析。

- 日志分析:使用专门的工具或脚本分析日志,快速定位问题并提供改进建议。

在本节中,我们深入探讨了SRIO测试平台的需求分析、测试用例设计原则、环境配置方法以及监控与日志分析流程。每个测试用例都经过精心设计,确保覆盖所有可能的使用场景。同时,测试环境的配置和监控机制的建立是确保测试过程顺利进行和结果准确性的关键。在下一节中,我们将讨论如何在系统级集成中应用SRIO协议,以及如何进行集成测试与验证。 ```

7. SRIO协议的系统级集成

7.1 SRIO在系统级集成中的角色

7.1.1 系统级设计的考虑因素

在进行系统级设计时,SRIO协议的集成需要考虑多个因素以确保性能和可靠性。首先,设计者应考虑系统的数据吞吐率和带宽需求。SRIO以其高速和低延迟的特点,非常适合需要实时数据处理的应用。同时,系统级设计中还应考虑总线的扩展性,SRIO能够支持多达128个独立的链接,使得在设计高密度系统时具有很强的扩展能力。

7.1.2 SRIO与其他总线技术的对比

SRIO与传统的PCIe和千兆以太网等总线技术相比,具有明显的优势。SRIO提供更低的延迟和更高的数据吞吐量,这在高速数据通信和实时系统中尤为重要。此外,SRIO的全双工通信模式允许数据同时发送和接收,进一步提高了系统性能。

7.2 SRIO集成的实例分析

7.2.1 典型应用场景介绍

SRIO协议在多个领域得到了广泛应用,包括航空航天、高性能计算和工业自动化等。例如,在航空航天领域,SRIO常用于连接飞行器上的不同子系统,需要在恶劣环境下保证数据的高速稳定传输。在高性能计算领域,SRIO被用于构建高性能计算集群,通过高速互联减少节点间通信的时间延迟。

7.2.2 集成过程中的常见问题及解决方案

在SRIO的集成过程中,工程师可能会遇到信号完整性问题、时钟同步和协议兼容性问题。这些问题可以通过合理设计信号传输路径、使用高速时钟源和确保设计遵循标准协议来解决。针对信号完整性问题,可以在PCB设计中使用差分对和终端匹配技术;针对时钟同步问题,可以使用板载的时钟恢复器和同步器;针对协议兼容性问题,可以通过软件配置或硬件设计来调整FPGA中的SRIO IP核。

7.3 SRIO集成的测试与验证

7.3.1 集成测试的策略与方法

在SRIO的集成测试阶段,工程师需要确保所有的硬件和软件组件能够协同工作。测试策略应该包括单元测试、功能测试、性能测试和稳定性测试。单元测试可以使用Verilog的测试平台来验证单独模块的功能。功能测试需要验证SRIO链路在不同工作模式下的行为。性能测试关注于数据传输的吞吐量和延迟,而稳定性测试则着重于长时间运行的可靠性和散热性能。

7.3.2 验证标准与测试用例的建立

建立SRIO协议的验证标准是测试过程中的重要一环。验证标准应该包括电气特性的检查、协议栈的实现正确性以及系统级的性能指标。测试用例的设计需要覆盖各种应用场景和异常情况,确保所有可能的交互都能得到测试。例如,可以设计包括正常数据传输、链路恢复、错误注入和系统重启等测试用例,以此来确保系统的鲁棒性和可靠性。

本文还有配套的精品资源,点击获取

简介:本文档集合了SRIO(Serial RapidIO)协议的测试案例,详细探讨了SRIO在FPGA上的实现。SRIO是一种高速串行总线技术,适用于高性能数据传输场景。文档中包含了使用Verilog硬件描述语言编写的SRIO实现代码,以及相关的测试平台和配置文件。这些资料将指导读者如何设计和验证SRIO协议在FPGA上的应用,包括协议的帧结构、仲裁机制、错误检测与恢复等关键细节。

本文还有配套的精品资源,点击获取