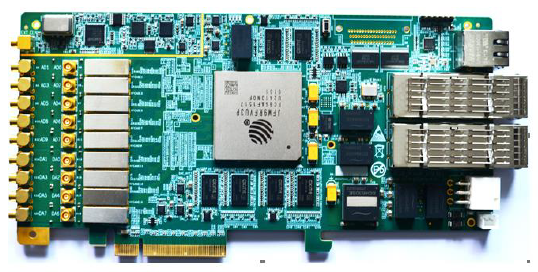

基于复旦微RFVU3P FPGA 的基带信号处理板(100%国产率)_jfm9rfvu3p

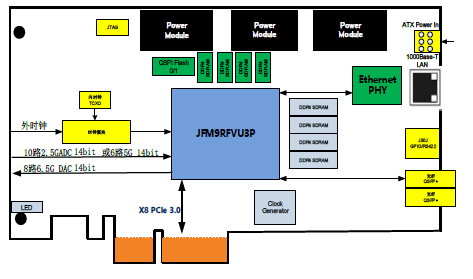

采用JFM9RFVU3P,实现了10 路 ADC 和8 路DAC 端口,并支持外部同源参考时钟,板载两组DDR4 64bit 2400M,以及一个千兆网口和2 个100G QSFP28+接口。

技术指标

FPGA 封装JFM9RFVU3P;

RF 接口:

10 路ADC (6 路14-bit 5GSPS 或者10 路14-bit、2.5GSPS);

8 路DAC (14-bit、6.5GSPS);

ADC 和DAC 支持信号频段范围1M~3G 或1M~6G;

性能:

挂载2 组DDR4 接口,64bit 2400MHz;

1 路千兆网口RJ45;

1 个SD 卡槽;

1 个 EMMC;

多个 GPIO 和RS422;

2 个4x 100G QSFP28+接口,支持线速率500M~25Gbps;

主机:

PCIe 3.0x8;

物理与电气特征

板卡尺寸:22cm * 11cm

板卡供电:4A max@+12V(±5%)

散热方式:风冷/导冷散热

软件支持

板上测试工程:

FPGA 各接口demo;

板上对外接口demo;

可根据客户需求提供定制化算法与系统集成:

应用范围

软件无线电;

雷达与基带信号处理;