STM32-时钟系统实战:AHB/APB配置详解_stm32 apb ahb

从 时钟树原理、RCC 寄存器配置、AHB/APB 时钟设置流程、实战案例 四个维度,深度解析 STM32 RCC 时钟系统中 AHB、APB 时钟的设置方法,并结合代码示例说明应用场景:

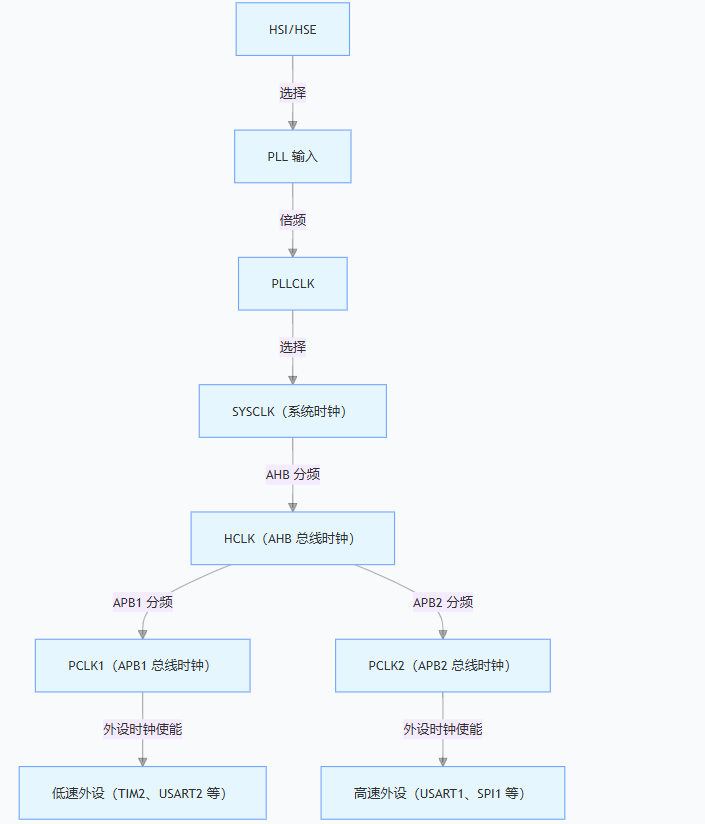

一、RCC 时钟系统的底层原理(时钟树核心逻辑)

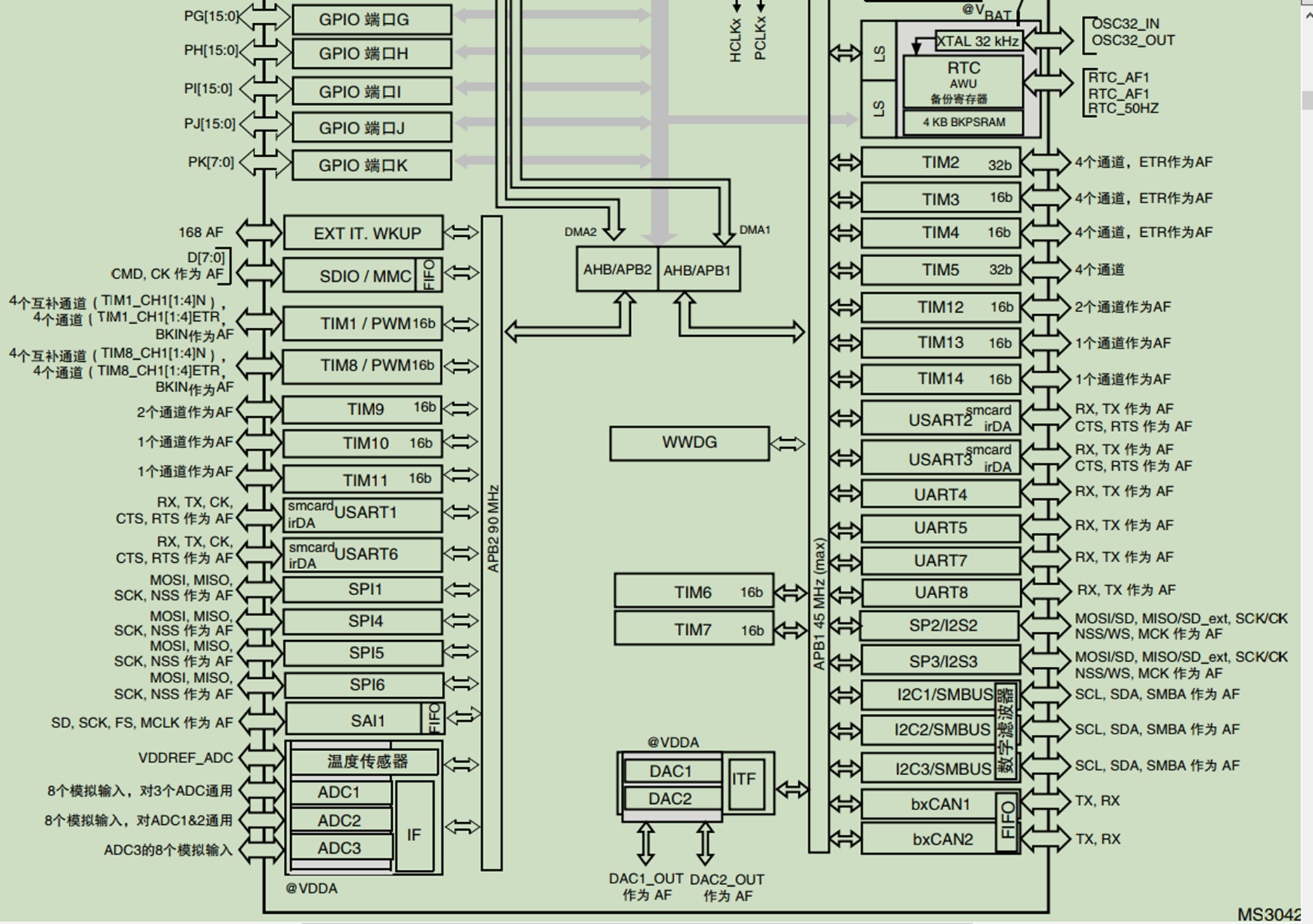

(一)时钟源与分频器的物理架构

STM32 的时钟系统通过 “时钟源 → 倍频 / 分频 → 总线分配” 三级架构实现,核心组件:

- 基础时钟源:

- HSI(内部高速时钟):默认 16MHz(不同系列可能不同,如 F4 系列为 16MHz),无需外部晶振,启动快但精度低。

- HSE(外部高速时钟):通常接 8MHz/25MHz 晶振,精度高,适合作为系统主时钟。

- PLL(锁相环):对 HSI/HSE 倍频,生成高频系统时钟(如 168MHz、216MHz 等,依系列而定)。

- 总线分频器:

- AHB 预分频器:决定 HCLK(AHB 总线时钟)频率,HCLK 是其他总线(APB1、APB2)的基础。

- APB1 预分频器:决定 PCLK1(APB1 总线时钟),挂载低速外设(如 USART2、I2C、TIM2 等)。

- APB2 预分频器:决定 PCLK2(APB2 总线时钟),挂载高速外设(如 USART1、SPI1、GPIO 等)。

(二)时钟树的硬件流程

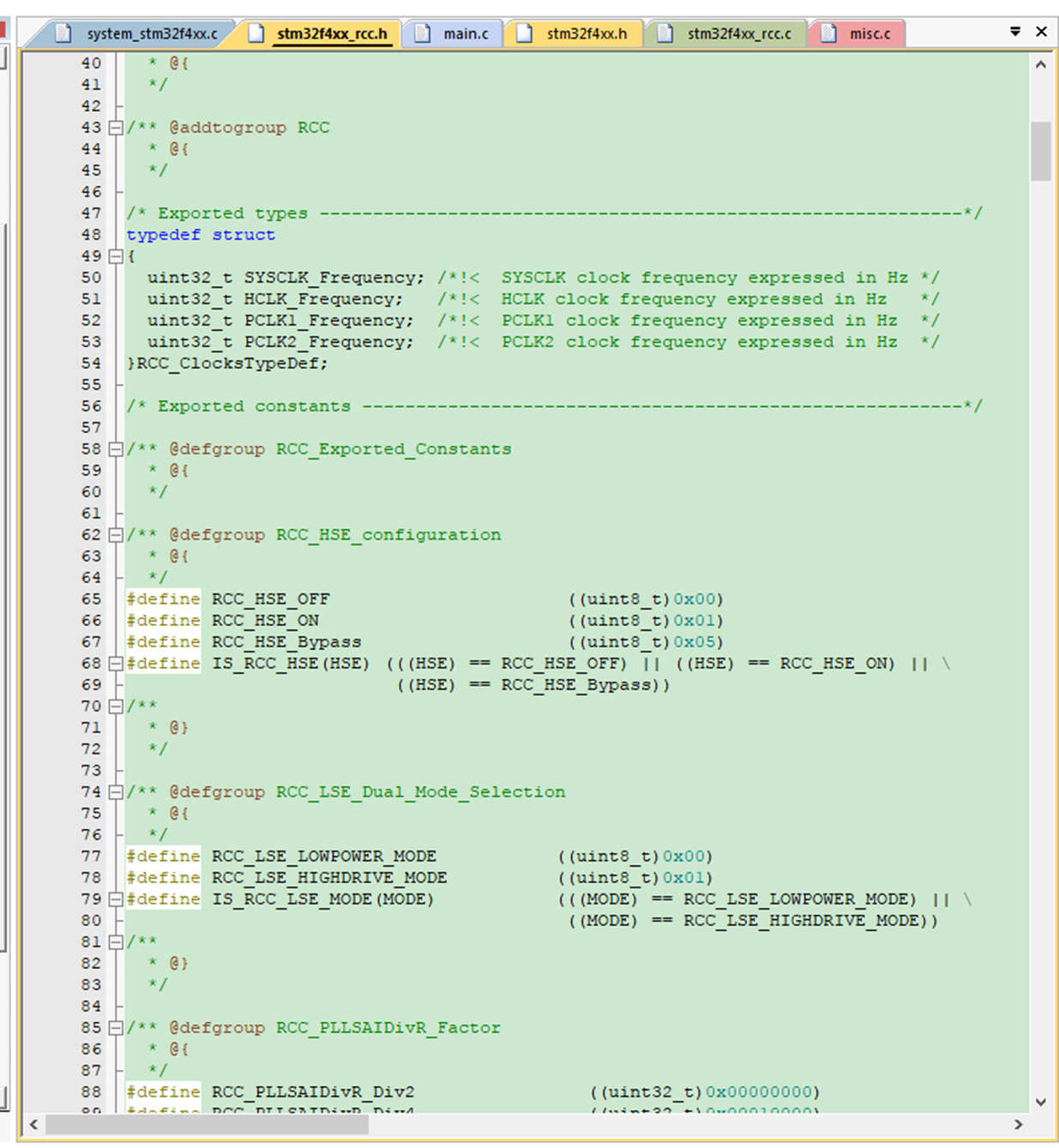

(三)关键寄存器的物理映射

- RCC 控制寄存器(RCC_CR):

- 位 16(HSEON):使能 HSE 时钟。

- 位 17(HSERDY):HSE 就绪标志(只读)。

- 位 24(PLLON):使能 PLL 时钟。

- RCC 配置寄存器(RCC_CFGR):

- 位 0-1(SW):选择系统时钟源(00=HSI,01=HSE,10=PLL)。

- 位 4-7(HPRE):AHB 预分频器配置(0b0000=1 分频,0b1000=2 分频,依此类推)。

- 位 8-10(PPRE1):APB1 预分频器配置(0b000=1 分频,0b100=2 分频,依此类推)。

- 位 11-13(PPRE2):APB2 预分频器配置(同 PPRE1 规则)。

- 外设时钟使能寄存器:

- RCC_AHB1ENR:AHB1 外设时钟使能(如 GPIOA、DMA2 等)。

- RCC_APB1ENR:APB1 外设时钟使能(如 TIM2、USART2 等)。

- RCC_APB2ENR:APB2 外设时钟使能(如 USART1、SPI1 等)。

二、AHB/APB 时钟设置的完整流程(以 HSE+PLL 为例)

需求:配置系统时钟为 168MHz(STM32F4 系列),并设置:

- HCLK(AHB 总线时钟)= 168MHz

- PCLK1(APB1 总线时钟)= 42MHz(HCLK/4)

- PCLK2(APB2 总线时钟)= 84MHz(HCLK/2)

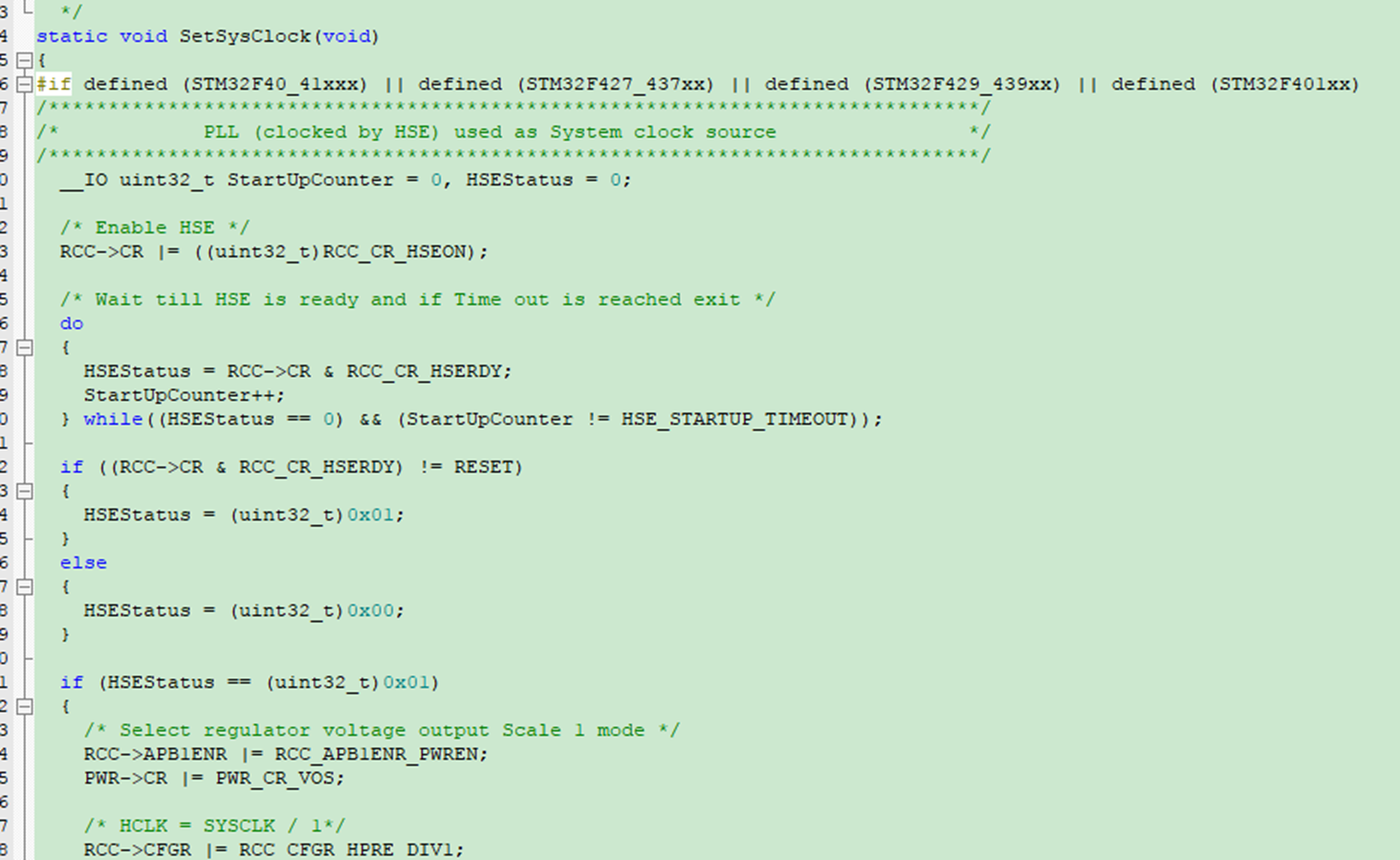

(一)步骤 1:使能 HSE 并等待就绪

c

// 1. 使能 HSE 时钟RCC->CR |= RCC_CR_HSEON; // 2. 等待 HSE 稳定(超时检测)uint32_t timeout = 0;while (!(RCC->CR & RCC_CR_HSERDY)) { if (timeout++ > 0xFFFF) { // HSE 启动超时,可添加错误处理(如切换到 HSI) break; }}(二)步骤 2:配置 PLL(倍频到 168MHz)

c

// PLL 输入选择 HSE,倍频系数 168MHz / HSE 频率(假设 HSE=25MHz)// PLL_M=25, PLL_N=336, PLL_P=2 → 25MHz * 336 / 2 = 4200MHz / 2 = 2100MHz? 不对,F4 系列 PLL 配置需参考手册!// 正确配置(以 STM32F407 为例,HSE=8MHz):// PLL_M=8, PLL_N=336, PLL_P=2 → 8MHz * 336 / 2 = 1344MHz / 2 = 672MHz? 仍错误,需严格按手册!// 正确流程(参考 STM32F4 参考手册):// PLL 时钟 = (HSE / PLL_M) * PLL_N / PLL_P// 目标 SYSCLK=168MHz,HSE=8MHz → (8 / 8) * 336 / 2 = 1 * 336 / 2 = 168MHz ✔️RCC->PLLCFGR = 0; // 清空配置RCC->PLLCFGR |= (8 <PLLCFGR |= (336 <PLLCFGR |= (2 <PLLCFGR |= RCC_PLLCFGR_PLLSRC_HSE; // PLL 输入选择 HSE// 使能 PLL 并等待就绪RCC->CR |= RCC_CR_PLLON;while (!(RCC->CR & RCC_CR_PLLRDY)) {}(三)步骤 3:配置 AHB/APB 分频器

c

// 配置 AHB 分频:HCLK = SYSCLK / 1 → HPRE=0b0000RCC->CFGR &= ~RCC_CFGR_HPRE; RCC->CFGR |= RCC_CFGR_HPRE_DIV1; // 配置 APB1 分频:PCLK1 = HCLK / 4 → PPRE1=0b100RCC->CFGR &= ~RCC_CFGR_PPRE1; RCC->CFGR |= RCC_CFGR_PPRE1_DIV4; // 配置 APB2 分频:PCLK2 = HCLK / 2 → PPRE2=0b100? 不,PPRE2_DIV2 是 0b101? 需查手册!// STM32F4 中:// PPRE2 位定义:0b000=1 分频,0b100=2 分频,0b101=4 分频...// 所以 PCLK2=HCLK/2 → PPRE2=0b100(DIV2)RCC->CFGR &= ~RCC_CFGR_PPRE2; RCC->CFGR |= RCC_CFGR_PPRE2_DIV2; (四)步骤 4:选择 PLL 作为系统时钟

c

RCC->CFGR &= ~RCC_CFGR_SW; // 清除原系统时钟选择RCC->CFGR |= RCC_CFGR_SW_PLL; // 选择 PLL 作为系统时钟// 等待系统时钟切换完成while ((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL) {}(五)步骤 5:配置外设时钟使能(以 GPIOA、USART1 为例)

c

// 使能 AHB1 外设时钟(GPIOA 属于 AHB1)RCC->AHB1ENR |= RCC_AHB1ENR_GPIOAEN; // 使能 APB2 外设时钟(USART1 属于 APB2)RCC->APB2ENR |= RCC_APB2ENR_USART1EN; 三、实战案例:配置时钟驱动 LED 闪烁(STM32F4 系列)

需求:通过配置 RCC 时钟,使系统时钟为 168MHz,并用 TIM2(APB1 外设)定时翻转 LED。

(一)完整代码(寄存器级实现)

c

#include \"stm32f4xx.h\"void SystemClock_Config(void) { // 1. 使能 HSE RCC->CR |= RCC_CR_HSEON; while (!(RCC->CR & RCC_CR_HSERDY)); // 2. 配置 PLL(HSE=8MHz → SYSCLK=168MHz) RCC->PLLCFGR = (8 << RCC_PLLCFGR_PLLM_Pos) | (336 << RCC_PLLCFGR_PLLN_Pos) | (2 <CR |= RCC_CR_PLLON; while (!(RCC->CR & RCC_CR_PLLRDY)); // 3. 配置 AHB/APB 分频 RCC->CFGR |= RCC_CFGR_HPRE_DIV1; // HCLK=168MHz RCC->CFGR |= RCC_CFGR_PPRE1_DIV4; // PCLK1=42MHz RCC->CFGR |= RCC_CFGR_PPRE2_DIV2; // PCLK2=84MHz // 4. 选择 PLL 作为系统时钟 RCC->CFGR &= ~RCC_CFGR_SW; RCC->CFGR |= RCC_CFGR_SW_PLL; while ((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL); // 5. 使能 GPIOA 时钟(AHB1) RCC->AHB1ENR |= RCC_AHB1ENR_GPIOAEN;}void TIM2_Init(void) { // 使能 TIM2 时钟(APB1) RCC->APB1ENR |= RCC_APB1ENR_TIM2EN; // 配置 TIM2 定时 1s(PCLK1=42MHz,分频后定时器时钟=42MHz) TIM2->PSC = 42000 - 1; // 预分频:42MHz / 42000 = 1000Hz TIM2->ARR = 1000 - 1; // 自动重装载:1000Hz → 1s 周期 TIM2->DIER |= TIM_DIER_UIE; // 使能更新中断 TIM2->CR1 |= TIM_CR1_CEN; // 启动定时器 // 配置 NVIC NVIC->IP[28] = 0x00; // 中断优先级 NVIC->ISER[0] |= 1 <SR & TIM_SR_UIF) { TIM2->SR &= ~TIM_SR_UIF; // 清除中断标志 GPIOA->ODR ^= (1 <MODER &= ~(0x03 <MODER |= (0x01 <OTYPER &= ~(1 <OSPEEDR |= (0x03 << 10); while (1) { // 主循环 }}(二)关键逻辑说明

- 时钟分频对定时器的影响:

- TIM2 挂载在 APB1,其时钟频率 = PCLK1 × 分频系数(若 APB1 分频为 4,且定时器分频器未加倍,则 TIM2 时钟 = PCLK1;若 APB1 分频≥2,定时器时钟会自动加倍,需参考手册)。

- 本案例中 PCLK1=42MHz,TIM2 时钟实际为 84MHz(因 APB1 分频为 4,触发定时器时钟加倍),所以

PSC=42000-1实现 1ms 计数。

- 外设时钟使能的必要性:

- 若未使能

RCC_AHB1ENR_GPIOAEN,GPIOA 寄存器操作无效,LED 无法翻转。 - 若未使能

RCC_APB1ENR_TIM2EN,TIM2 定时器无法运行,中断不会触发。

- 若未使能

四、高级应用:动态切换时钟源(HSI ↔ HSE)

需求:系统默认使用 HSE+PLL,当 HSE 故障时自动切换到 HSI+PLL。

(一)实现代码片段

c

void Clock_Error_Handler(void) { // 检测 HSE 故障 if (RCC->CR & RCC_CR_HSEBYP) { // HSE 旁路模式,可尝试切换到 HSI } // 切换到 HSI RCC->CR |= RCC_CR_HSION; while (!(RCC->CR & RCC_CR_HSIRDY)); // 配置 HSI 作为 PLL 输入(重新配置 PLL) RCC->PLLCFGR = (16 << RCC_PLLCFGR_PLLM_Pos) | // HSI=16MHz,分频为 16 (168 << RCC_PLLCFGR_PLLN_Pos) | // 倍频到 168 (2 <CR |= RCC_CR_PLLON; while (!(RCC->CR & RCC_CR_PLLRDY)); // 切换系统时钟到 HSI+PLL RCC->CFGR &= ~RCC_CFGR_SW; RCC->CFGR |= RCC_CFGR_SW_PLL; while ((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL);}// 在主循环中检测 HSE 状态int main(void) { SystemClock_Config(); while (1) { if (!(RCC->CR & RCC_CR_HSERDY)) { Clock_Error_Handler(); } // 其他任务 }}(二)关键机制

- 时钟故障检测:通过

RCC->CR的HSERDY位判断 HSE 是否就绪,若故障则执行切换。 - 动态 PLL 配置:切换时钟源后需重新配置 PLL 参数,确保系统时钟稳定。

- 系统时钟切换:需等待

SWS标志位更新,确保切换完成后再执行后续操作。

五、避坑指南与调试技巧

(一)常见问题:时钟配置后外设不工作

- 原因 1:未使能外设时钟(如

RCC_APB2ENR_USART1EN未置位,USART1 无法运行)。 - 原因 2:分频系数配置错误(如 APB1 分频为 4,但定时器时钟未正确加倍,导致定时不准确)。