【硬件基础篇】:TTL和CMOS电平_ttl电平

文章目录

- 1. 为什么数字电路需要 “电平规范”?

-

- 1.1 什么是 “电平”?

- 2. TTL 电平

- 3. CMOS 电平

- 4. 数字接口匹配

-

- 4.1 TTL 驱动 CMOS

- 4.2 CMOS 驱动 TTL

- 5. 电平转换

-

- 5.1 3.3V to 5V

- 5.2 5V to 3.3V

1. 为什么数字电路需要 “电平规范”?

这就好比不同国家的人说同一种语言才能交流,电平规范就是数字电路的 “通用语言”,没有它,电路之间就会 “鸡同鸭讲”。

1.1 什么是 “电平”?

在数字电路中,我们用 “高电平” 和 “低电平” 分别表示二进制的 1 和 0。

比如:

- 当芯片的某个引脚电压是 3V 时,可能代表 “1”(高电平);

- 当电压是 0V 时,代表 “0”(低电平)。

但问题来了:多高算 “高”?多低算 “低”?不同的电路(比如你做的电路板、别人做的芯片)可能有不同的定义。

电平规范的作用:规定一个 统一的 “高 / 低电平电压范围”,让所有电路都按这个标准设计。

假设 A芯片 “电压≥2V 是高电平(1)”,B芯片 “电压≥3V 才是高电平(1)”。

当A芯片输出 2.5V(A认为是 “1”),B芯片却认为这是 “低电平(0)”,结果就是 信号识别错误,电路瘫痪!

电平规范的 “噪声容限”:信号在传输时会受到 噪声干扰(比如电线摩擦、电磁干扰),电压可能会 “抖动”,规定一个 “安全范围”,只要信号在范围内,即使有噪声也不影响判断。

比如:TTL 的高电平输入门槛是 ≥2.0V,而实际输出至少是 2.4V,中间 0.4V 的差距 就是 “容限”,允许噪声在这个范围内波动而不报错。

明确 “驱动能力”,避免电路损坏:规定 输出电流下限(比如 TTL 输出高电平时至少能提供 -400μA 电流)和 输入电流上限(比如 CMOS 输入电流几乎为 0),确保前级电路能 “驱动” 后级电路,不会过载或信号失真。

芯片 A 的输出端最多能提供 10mA 电流,芯片 B 的输入端需要 100mA 才能工作,如果直接连接,B 无法工作。

2. TTL 电平

通过双极型晶体管(BJT)实现的逻辑电平标准,靠晶体管的饱和与截止状态表示逻辑 0 和 1。

- 电源电压(VCC):5V。

- 输出电平:

逻辑 1(高电平,VOH):最小值 2.4V。

逻辑 0(低电平,VOL):最大值 0.4V。 - 输入电平:

识别为 1 的最小输入(VIH):2.0V。

识别为 0 的最大输入(VIL):0.8V。 - 噪声容限:

高电平噪声容限:VOH (min) - VIH (min) = 2.4V - 2.0V = 0.4V。

低电平噪声容限:VIL (max) - VOL (max) = 0.8V - 0.4V = 0.4V。

3. CMOS 电平

通过互补的 NMOS 和 PMOS 场效应管(FET)实现的逻辑电平,靠栅极电压控制管子导通 / 截止。

- 电源电压(VDD):范围宽,常见 5V、3.3V、1.8V、1.2V 等。

- 输出电平(理想情况):

逻辑 1:接近 VDD(VOH ≈ VDD - 0.1V)。

逻辑 0:接近 0V(VOL ≈ 0.1V)。 - 输入电平(与 VDD 相关):

识别为 1 的最小输入(VIH):通常为 0.7×VDD(如 5V 时为 3.5V,3.3V 时为 2.31V)。

识别为 0 的最大输入(VIL):通常为 0.3×VDD(如 5V 时为 1.5V,3.3V 时为 0.99V)。 - 噪声容限:

高电平噪声容限:VDD - VIH = VDD - 0.7VDD = 0.3VDD。

低电平噪声容限:VIL - 0V = 0.3VDD(比 TTL 更高,抗干扰能力更强)。

4. 数字接口匹配

4.1 TTL 驱动 CMOS

5V TTL → 3.3V CMOS:TTL 输出高电平 2.4V ≥ 3.3V CMOS 的 VIH(2.31V),通常可直接驱动。

5V TTL → 5V CMOS:TTL 输出高电平 2.4V ≥ CMOS 输入高电平 3.5V? 不满足(5V CMOS 的 VIH=3.5V),需外接上拉电阻到 5V,将 TTL 的 2.4V 提升至 5V。

4.2 CMOS 驱动 TTL

5V CMOS → 5V TTL:CMOS 输出低电平 0.1V ≤ TTL 的 VIL=0.8V,高电平 5V ≥ TTL 的 VIH=2.0V,可直接驱动。

3.3V CMOS → 5V TTL:CMOS 输出高电平 3.3V ≥ TTL 的 VIH=2.0V,低电平 0.1V ≤ 0.8V,可直接驱动。

5. 电平转换

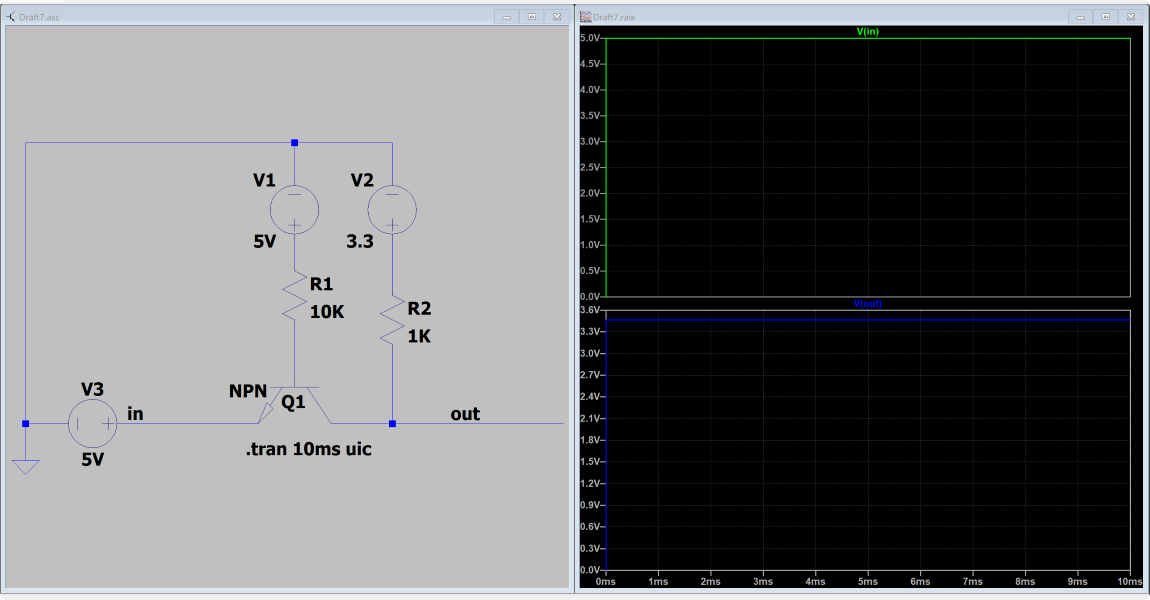

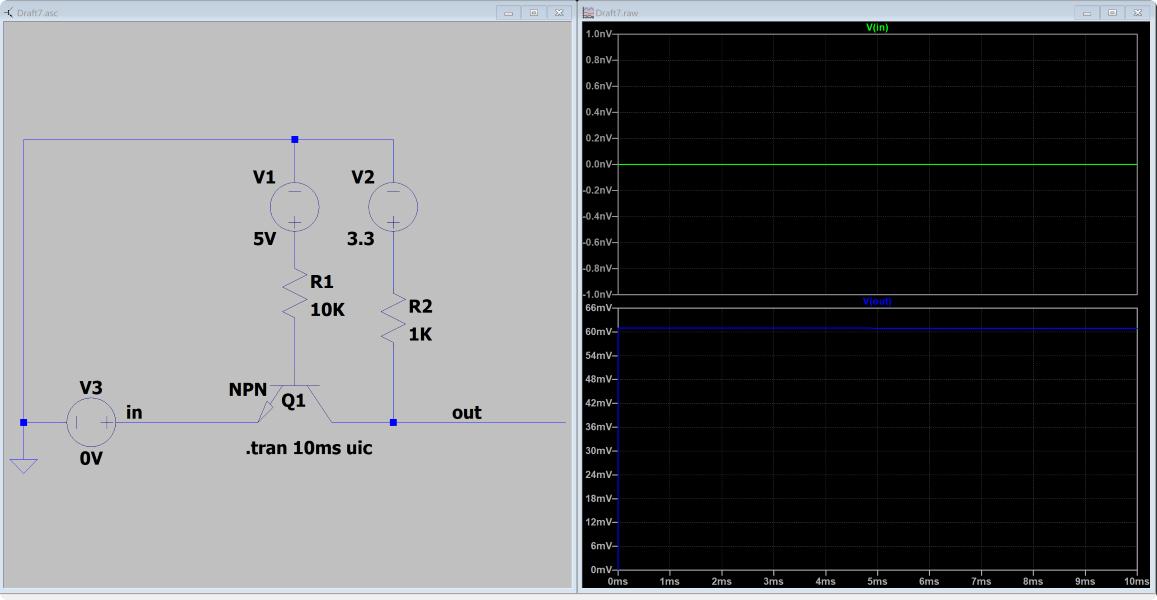

5.1 3.3V to 5V

R1与Q1组成OC门,配合R2上拉至5V,实现电平转换。

in输入0V,Q1导通,out端为0V左右,完成电平转换功能。

in输入3.3V,Q1截止,out端为5V,完成电平转换功能。

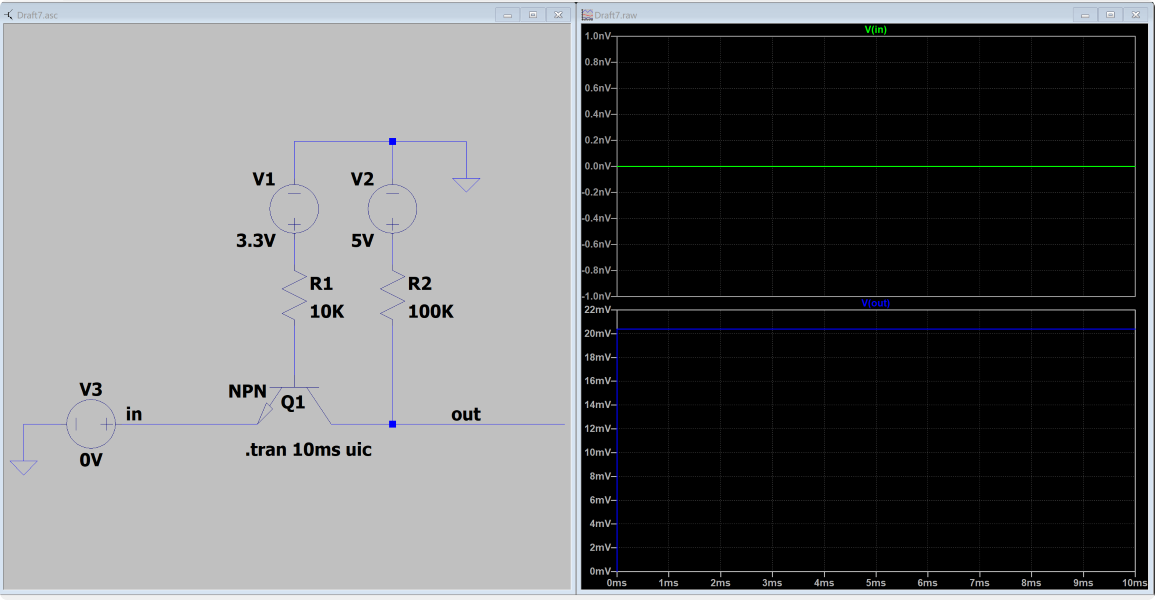

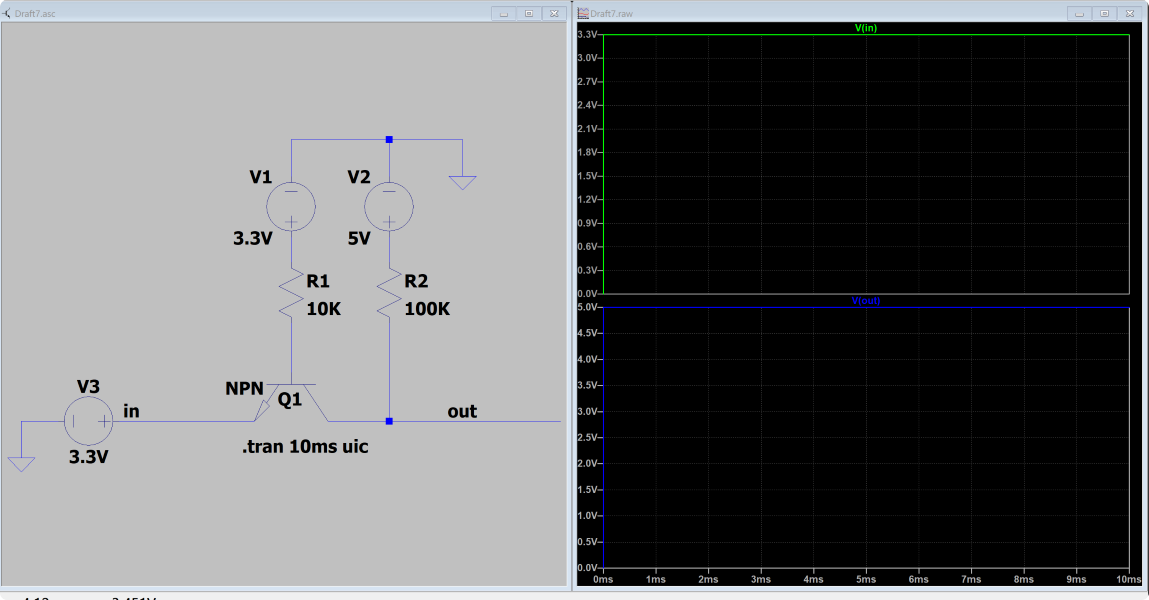

5.2 5V to 3.3V

R1与Q1组成OC门,配合R2上拉至3.3V,实现电平转换。

in输入0V,Q1导通,out端为0V左右,完成电平转换功能。

in输入5V,Q1截止,out端为3.3V,完成电平转换功能。