FPGA以太网通信实战(一):实现MDIO接口驱动,掌控PHY芯片的钥匙_yt8531

一、以太网简介

以太网(Ethernet)是当今局域网(LAN)领域应用最广泛的通信协议标准,它定义了网络中使用的物理介质(如电缆类型)和数据传输的信号处理方法。凭借低成本、通信速率高、抗干扰性强等显著优势,以太网被广泛应用于网络远程监控、交换机、工业自动化等对通信速率有较高要求的场景。

以太网技术不断发展,其速率经历了显著提升:

- 标准以太网: 10 Mbit/s

- 快速以太网: 100 Mbit/s

- 千兆以太网: 1000 Mbit/s (1 Gbit/s) - 满足大部分应用场景的理论最高速率。

- 万兆以太网: 10 Gbit/s - 通过扩展 IEEE 802.3 协议和 MAC 规范实现。

从硬件角度看,一个典型的以太网接口主要由两大核心部件构成:

- MAC(Media Access Control,媒体访问控制)控制器: 负责处理数据链路层的核心协议,如帧的组装/拆分、寻址(源/目的MAC地址)、错误检测(CRC)等。MAC控制器定义了数据如何组织并准备在物理介质上传输。

- PHY(Physical Layer,物理层接口)芯片: 负责处理实际的物理信号转换和连接管理。它的核心功能包括:

-

- 发送: 接收来自MAC的并行数据(对PHY而言是原始数据流),将其转换为串行数据流,并根据物理层编码规则(如曼彻斯特编码、4B/5B编码等)调制为可在线缆上传输的模拟信号。

- 接收: 执行相反过程:将从线缆接收到的模拟信号解调、解码,恢复成数字信号,并转换为并行数据发送给MAC。

- 连接管理(关键!): 当网线接入时,PHY通过自协商(Auto Negotiation) 机制与对端设备通信。双方交换能力信息(支持的速率、双工模式、流控等),并自动协商出两者都能支持的最高性能和最优配置(如1Gbps全双工)。PHY通常通过LED指示灯直观显示当前的连接状态(如链路是否建立)和工作状态(如速率)。

二、MDIO接口——PHY芯片的管理通道

2.1 简介

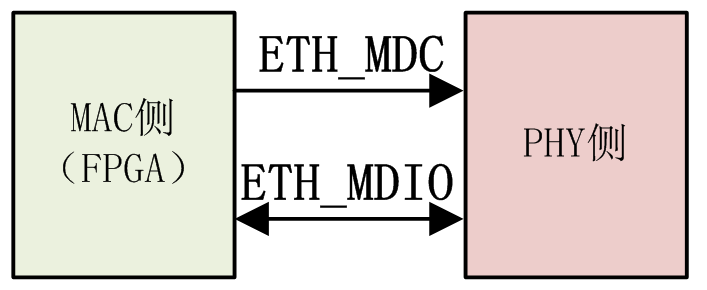

MDIO(Management Data Input/Output)接口是MAC和PHY芯片之间的一个配置接口,也称为SMI 接口( Serial Management Interface,串行管理接口)。该接口用来配置PHY 芯片的工作模式以及获取 PHY 芯片的状态信息。PHY 芯片内部包含一系列寄存器,用户通过这些寄存器来配置 PHY 芯片的工作模式以及获取 PHY 芯片的状态信息,如连接速率、双工模式、自协商状态等。FPGA 通过 MDIO 接口对PHY 芯片内部的寄存器进行配置。通常情况下, PHY芯片在默认状态下也可以正常工作。MAC(FPGA)和PHY芯片连接示意图如下:

MAC和PHY连接示意图 MDIO 接口包括 ETH_MDC(数据管理时钟)和 ETH_MDIO(数据管理输入输出)两条信号线。 ETH_MDC 为 ETH_MDIO 提供时钟,ETH_MDC 的最大时钟不能超过 12.5Mhz。 ETH_MDIO 为双向数据引脚,既用于发送数据,也用于接收数据。

2.2 MDIO接口帧格式

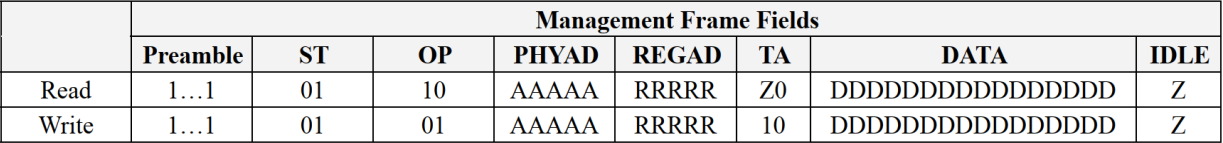

MDIO接口读写通信帧格式如下:

MDIO接口帧格式 名称 长度 说明 Preamble 32 bits 前导码,有MAC发送32位逻辑“1”,用于同步PHY芯片

ST 2 bits 帧开始码,用01表示 OP 2 bits 操作码,读:10, 写:01 PHYAD 5 bits PHY地址,用于表示与哪个PHY芯片通信 REGAD 5 bits 寄存器地址 TA 2 bits 转向码。

在读命令中, MDIO 在此时由 MAC 驱动改为 PHY 驱动,在第一个 TA位, MDIO 引脚为高阻状态,第二个 TA 位, PHY 将 MDIO 引脚拉低,准备发送数据;

在写命令中,不需要 MDIO 方向发生变化, MAC 固定输出 2’b10,随后开始写入数据。

DATA 16 bits 数据,高位在前,低位在后。 IDLE - 空闲状态,此时 MDIO 为无源驱动,处于高阻状态,但一般用上拉电阻使其上拉至高电平。 2.3 YT8531以太网PHY芯片

本次使用的PHY芯片是裕太微电子的YT8531芯片,接下来简单介绍YT8531芯片相关寄存器。

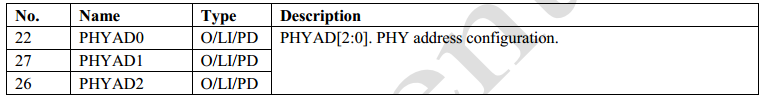

2.3.1 PHY地址

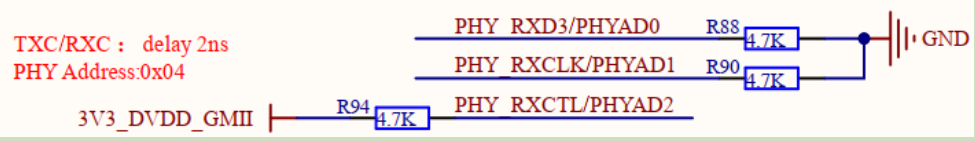

YT8531芯片的PHY地址一共有3位,由PHYAD0,PHYAD1和PHYAD2引脚决定。通过硬件电路设置PHYAD[2:0]引脚为上拉或下拉,可以表示不同的地址。

YT8531芯片的PHY地址引脚

PHY地址引脚原理图 从原理图上可以看出,以太网 PHY 芯片 PHYAD2 接上拉电阻,PHYAD1和PHYAD0 接下拉电阻,因此 PHY 地址为 5’h04。

2.3.2 复位

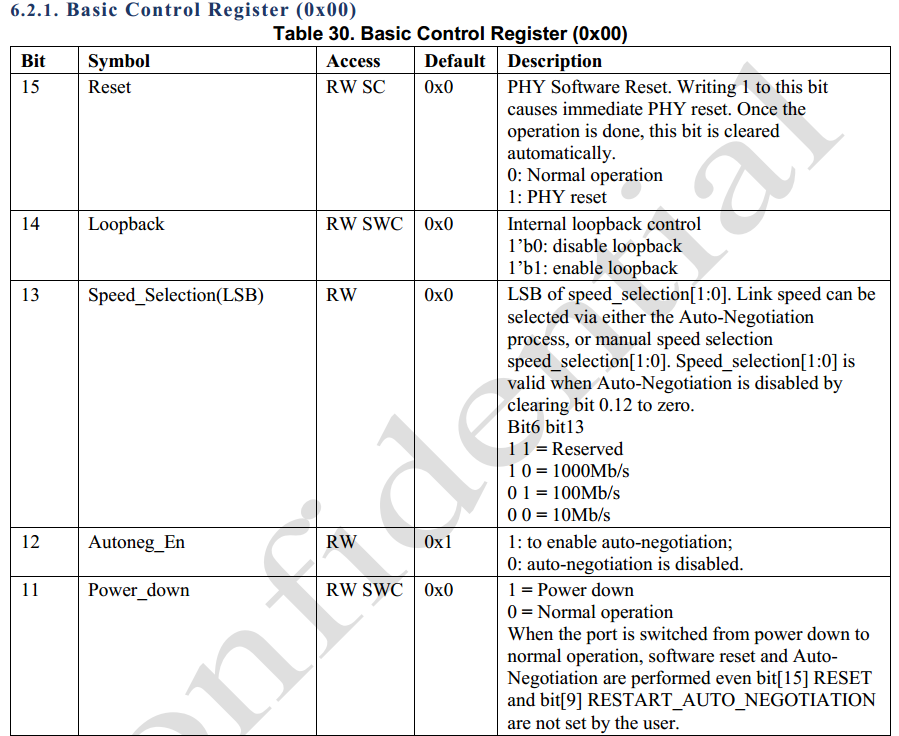

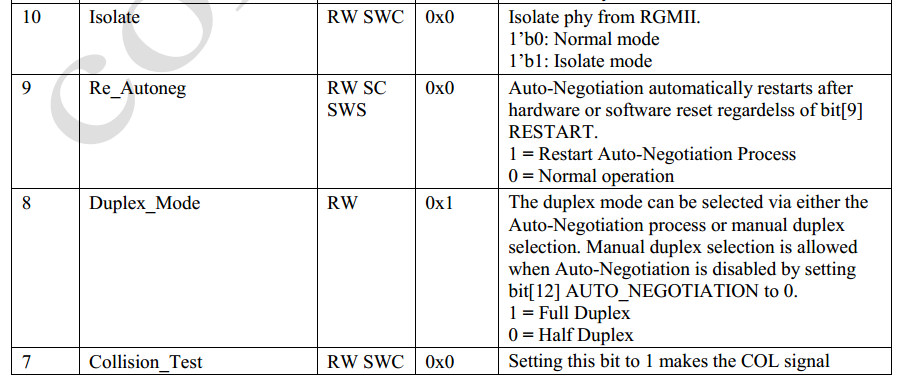

YT8531 芯片复位后,PHY内部寄存器的数据会恢复默认的状态,并且重新开始和 MAC 进行自协商。YT8531 支持两种复位方式,一种是硬件复位,另外一种是软件复位。硬件复位时通过 PHY_RST_N引脚实现对 PHY 芯片的复位,当 ETH_RST_N 引脚持续 10ms 的低电平时,即可实现对 PHY 芯片的复位。软件复位通过向寄存器地址 0x00 的 Bit[15]写入1进行复位,并且在完成复位后,该位会自动清零。

2.3.3 寄存器

YT8531共有22个寄存器,这里仅介绍用到的三个寄存器,基本控制寄存器、基本状态寄存器以及PHY芯片特定状态寄存器。

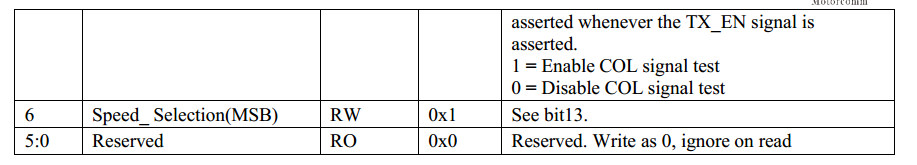

1. 基本控制寄存器(Basic Control Register, Address 0x00),简写为BCR,用于芯片的复位和其他功能控制。

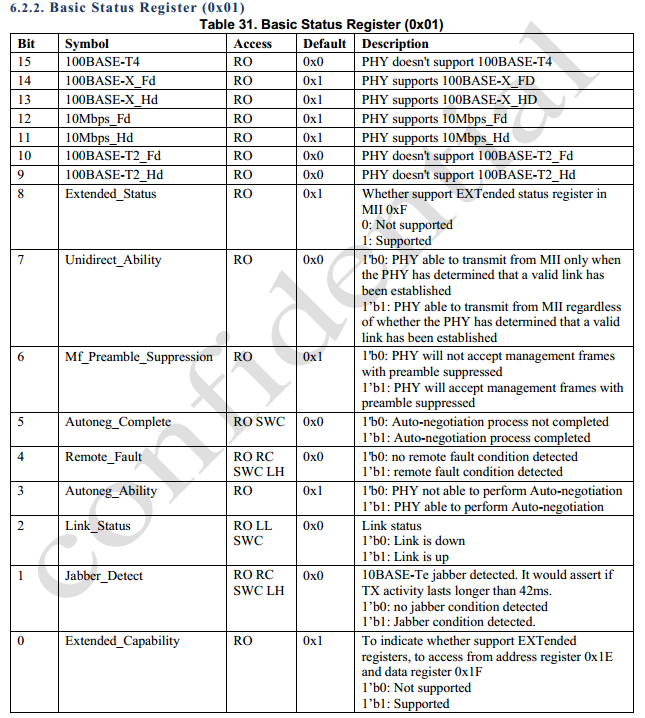

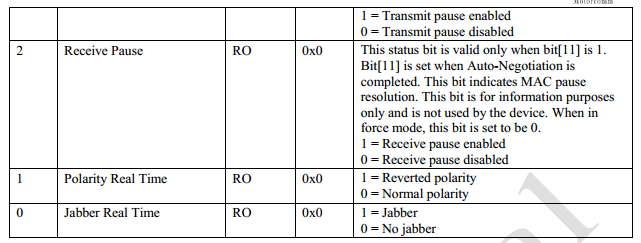

2. 基本状态寄存器(Basic Status Register, Address 0x01),简写为:BSR,用于读取PHY芯片一些基本状态。

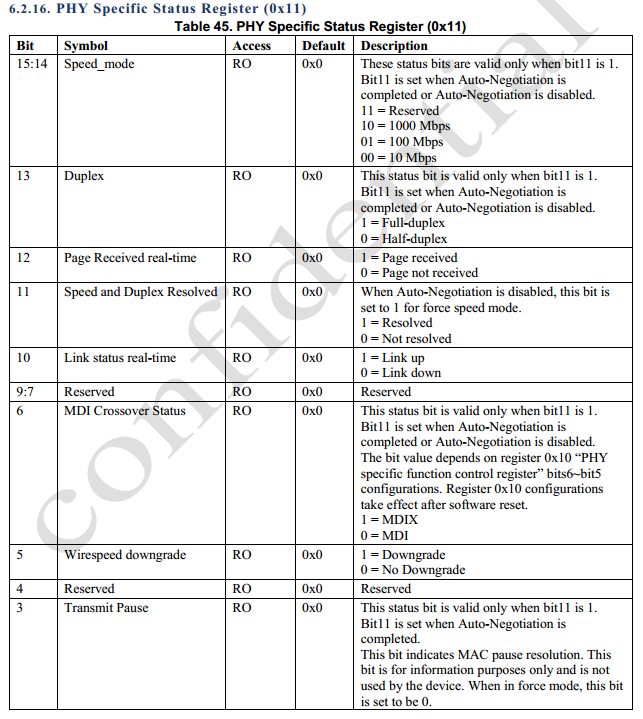

3. PHY 特定状态寄存器( PHY Specific Status Register , Address 0x11),简写为: PHYSR,用于读取PHY一些特殊状态。

三、FPGA MDIO接口读写通信实验

3.1 实验任务

FPGA通过MDIO接口与PHY芯片进行读写通信,具体要求如下:

1. 板载的触摸按键( TPAD)控制 MDIO 接口进行软复位

2. 通过两个 LED 灯实时指示当前网口的连接速度。当 LED0 灯亮的时候,表示当前的网口速率为 10Mbps;当 LED1 亮的时候,表示当前网口的速率为100Mbps;当两个 LED 都亮的时候,表示当前网口的速率为 1000Mbps;当两个 LED 灯都熄灭时,说明当前网络自协商失败,硬件或者网络存在异常。

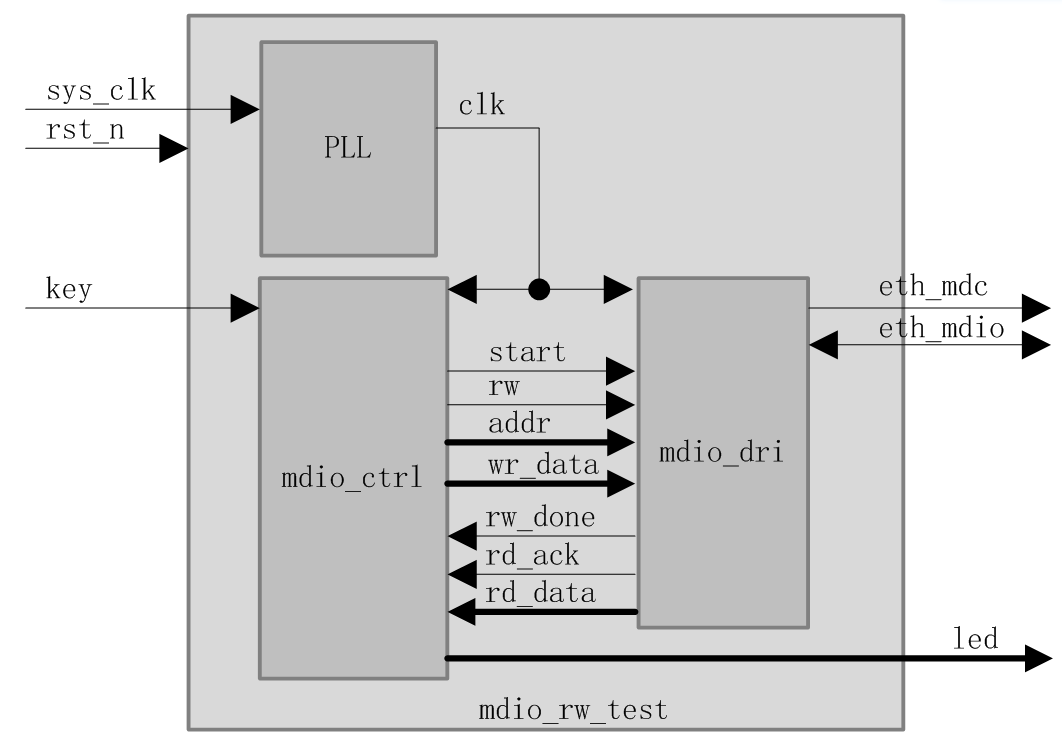

3.2 顶层架构

3.3 mdio_dri模块

3.3.1 功能描述

mdio_dri模块主要功能是通过 mdio 接口读写 phy 芯片内部寄存器的数据。

当 start 信号拉高后,表示开始读写PHY芯片;根据 rw 信号判断本次通信读与写,低电平进行写操作,高电平进行读操作;addr 信号为寄存器地址,位宽为5;wr_data 为写操作的写数据,位宽为16;rd_data 为读操作的读数据,位宽为16;当写或读操作完成是,rw_done 信号拉高一个时钟周期;rd_ack 信号为读应答信号,默认为高电平,当进入读操作后,应答完成会拉低应答信号,并读取寄存器中的数据;eth_mac 信号是在clk 的基础上进行分频,频率不超过12.5Mhz;eth_mdio 信号是MDIO 接口的双向数据信号。

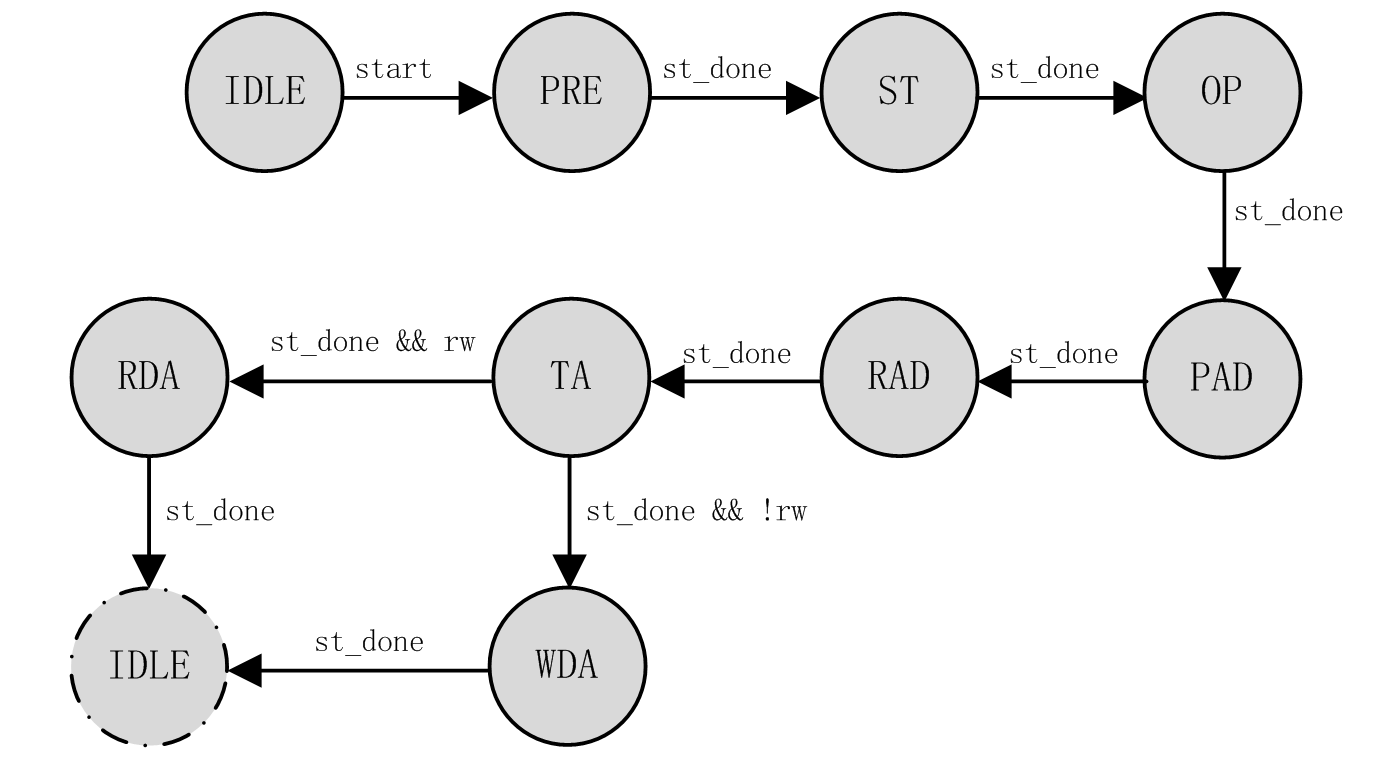

3.3.2 状态转移图

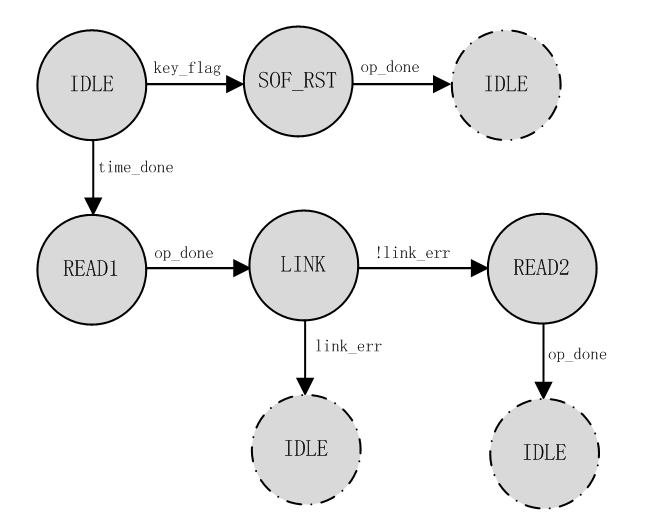

状态描述:

- IDLE:空闲状态,当start 信号拉高,进入前导码状态。

- PRE:前导码状态,该状态发送32位前导码,发送完成拉高st_done 信号。

- ST:帧开始码状态,该状态发送2位帧开始码,发送完成拉高st_done 信号。

- OP:操作码状态,该状态发送2位操作码,根据rw 信号决定发送10 和 01,发送完成拉高st_done 信号。

- PAD:PHY地址状态,该状态发送5位PHY地址5’h04,发送完成拉高st_done 信号。

- RAD:寄存器地址状态,该状态发送5位寄存器地址,发送完成拉高st_done 信号。

- TA:转向码状态,根据rw 信号决定该状态是否为高阻态,并决定进入写数据状态或读数据状态。

- RDA:读数据状态,该状态接收eth_mdio 信号上的数据,合并成16bits数据,接收完成拉高st_done 信号。

- WDA:写数据状态,该状态发送16bits数据,发送完成拉高st_done 信号。

3.4 mdio_ctrl模块

3.4.1 功能描述

mdio_ctrl 模块主要使用板载的按键控制 MDIO 接口进行软复位,并通过两个 LED 灯实时指示当前网口的连接速度。

- 检测key 按键是否按下,若按下对PHY芯片进行软复位,向5\'h0寄存器的bit[15]写入1。

- 定时检测以太网连接状态,即读取5\'h01寄存器;若连接成功检测以太网速度,即读取5\'h11寄存器;若连接失败,则等待下次检测连接状态。

- 若成功检测到以太网速度,根据速度使相应led 亮起。

3.4.2 状态转移图