FPGA 三速自适应udp协议栈,支持8192字节的巨型帧分片重组和发送,使用IP为RAM与fifo。_fpga 巨型帧

一、引言

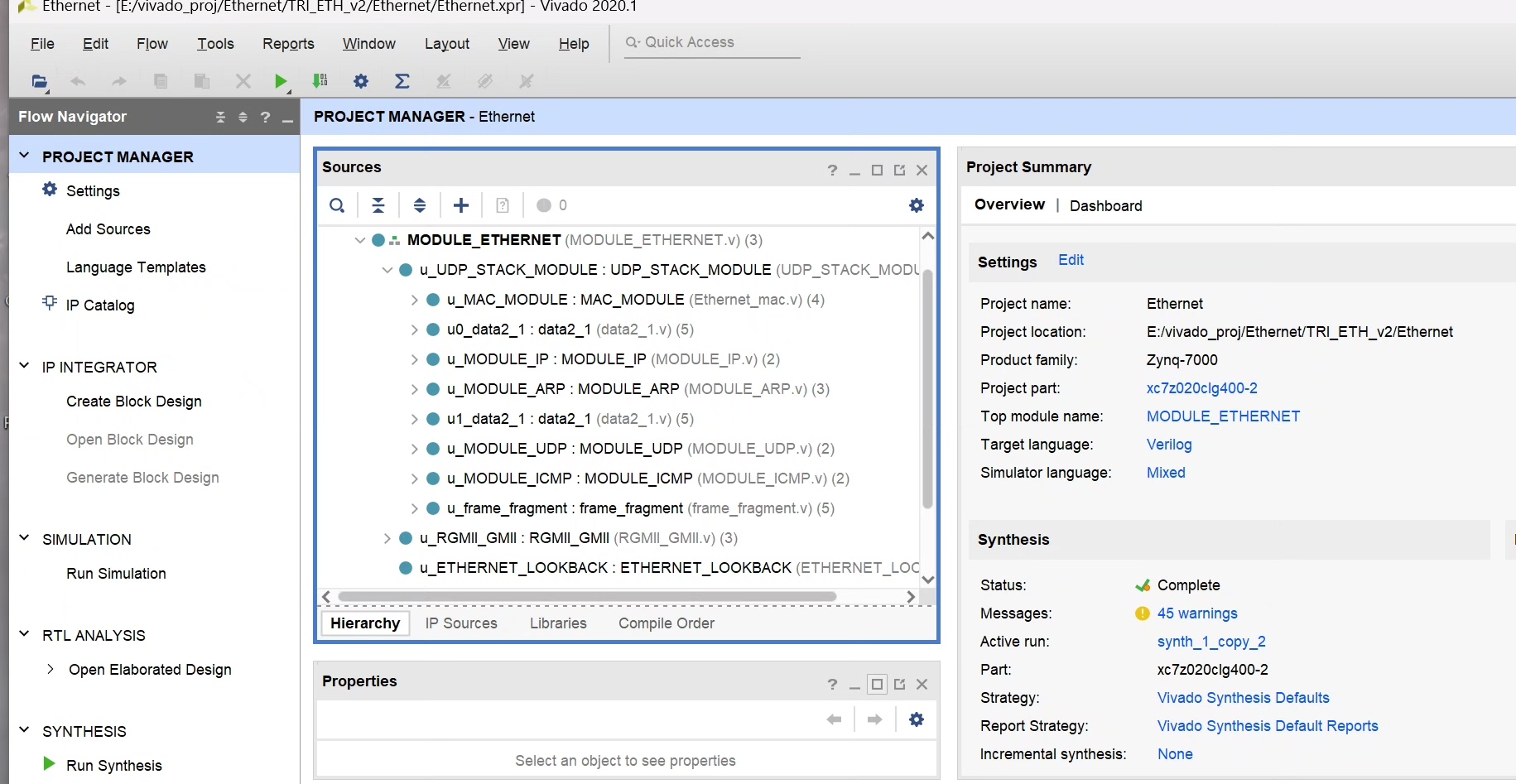

随着网络技术的飞速发展,数据传输的速度和效率要求日益提高。为了满足这一需求,本文将探讨一种基于FPGA(现场可编程门阵列)的三速自适应UDP(用户数据报协议)协议栈的设计与实现。该协议栈支持8192字节的巨型帧分片重组和发送,利用IP为RAM与fifo进行优化,并支持ARP(地址解析协议)与ICMP(因特网控制消息协议)。

二、FPGA与UDP协议栈的结合

FPGA作为一种可编程的硬件设备,具有高速、低功耗、高可靠性的特点,被广泛应用于网络通信、数据处理等地方。UDP协议是一种无连接的传输层协议,具有简单、高效、实时性强的特点。将FPGA与UDP协议栈结合,可以充分利用FPGA的高速处理能力和UDP协议的优点,实现高效、可靠的网络通信。

三、三速自适应UDP协议栈设计

为了满足不同网络环境下的需求,本文设计了一种三速自适应UDP协议栈。该协议栈可以根据网络状况动态调整发送速率,以适应不同的网络环境。具体而言,该协议栈包括低速、中速和高速三种模式,可以根据网络带宽、延迟等因素进行自动切换。

四、巨型帧分片重组与发送

为了进一步提高数据传输的效率,该协议栈支持8192字节的巨型帧分片重组和发送。在发送端,大帧数据将被分片成多个小帧进行传输;在接收端,小帧将被重组成原始大帧数据进行处理。这种机制可以充分利用网络带宽,减少传输过程中的延迟和丢包率。

五、IP为RAM与fifo优化

为了提高数据处理速度和效率,该协议栈采用IP为RAM的设计。这种设计可以将IP协议栈的数据处理过程存储在RAM中,实现高速的数据读写和传输。同时,利用fifo(先进先出)缓冲区对数据进行缓存和处理,可以有效地减少数据传输过程中的抖动和延迟。

六、支持ARP与ICMP

该协议栈还支持ARP和ICMP协议。ARP协议用于实现IP地址到MAC地址的解析,ICMP协议用于实现网络层消息的传输和控制。这两个协议的加入使得该协议栈具备了更强的网络通信能力和更丰富的功能。

七、结论

本文设计了一种基于FPGA的三速自适应UDP协议栈,通过结合FPGA的高速处理能力和UDP协议的优点,实现了高效、可靠的网络通信。该协议栈支持巨型帧分片重组和发送、IP为RAM与fifo优化、支持ARP与ICMP等功能,可以满足不同网络环境下的需求。未来,我们将继续对该协议栈进行优化和完善,以适应更多场景和网络需求。

FPGA 三速自适应udp协议栈,支持8192字节的巨型帧分片重组和发送,使用IP为RAM与fifo。

支持ARP与ICMP。