嵌入式Linux实战项目全开源-华为嵌入式开发大赛初赛获奖作品-基于LS1046A的时间同步系统设计与可视化监控平台开发_嵌入式比赛获奖开发文档

一、项目描述

高精度时间同步技术是分布式嵌入式系统中保障事件一致性和时序协同的关键。本项目围绕IEEE 1588标准构建同步网络,在嵌入式平台上完成了从系统搭建到时钟节点部署的全流程实现,支持主从与透明时钟结构下的多种同步拓扑。进一步,设计了一种集设备管理、网络配置与同步监控于一体的图形化交互平台,实现了对多网口节点的可视化配置与联通性检测,并可对时间同步过程进行实时观测与参数追踪。该软硬件协同方法为工业控制、边缘计算等对时延敏感的分布式系统提供了一种具可操作性与可扩展性的实践路径。

二、项目说明

当前分布式嵌入式系统在工业自动化、能源调度、通信与航空航天等地方中日益普及,对多节点设备间高精度时间一致性提出了更高要求。IEEE 1588 精密时间协议(PTP)因其低成本、高精度的优势成为主流同步方案。然而,在复杂网络拓扑中构建一个具备透明时钟支持的高精度同步系统仍面临实现复杂、配置不便、实时监测能力不足等挑战。

有鉴于此,本项目旨在设计并实现一种软硬件协同的时间同步系统,集成多节点配置、网络拓扑构建与时间同步过程监控等关键功能,解决当前工业嵌入式平台中时间同步部署与可视化操作难的问题。系统基于LS1046A这一多网口嵌入式处理平台构建,以 IEEE 1588 时间同步协议为核心,支持主节点、从节点与透明节点的灵活配置,适用于多跳网络环境下的精准时间同步场景。

首先,在多节点配置方面,系统实现了对多个嵌入式节点的自动识别、串口通信管理与网口级别的 IP 地址配置功能。用户可针对设备上不同的以太网接口分别设定网络参数,实现透明节点在多个链路方向间的时间戳中继能力,从而提升复杂拓扑下的同步链完整性与准确性。

其次,在网络拓扑构建方面,系统提供图形化拓扑编辑功能,支持用户通过拖拽操作构建节点之间的逻辑连接关系,并自动检测节点间的网络连通性。每一条连接线均由系统自动触发 ping 命令验证是否可达,并以颜色和日志形式反馈状态,有效简化了网络配置的调试流程,提高组网的效率与准确性。

最后,在时间同步过程监控方面,系统支持对节点角色的配置与同步控制命令的远程下发,能够实时采集并图形化展示主从节点时钟相位偏差(offset)、往返平均链路传输时延(delay)及时钟频率偏移(drift) 等时钟同步关键参数。用户可在可视化界面中观察同步稳定性、调整同步策略,并结合交互日志追踪同步过程中的异常事件,实现系统级时间同步性能的可视、可控与可调。

通过对多网口嵌入式设备的统一管理、透明时钟支持的组网机制设计,以及同步状态的实时可视化,本系统显著提升了时间同步系统的构建效率与调试能力,降低了部署复杂度,为后续的工业控制系统、分布式传感器网络和边缘协同计算等应用中的时间一致性保障提供了可复用、可扩展的技术支撑。

三、项目开发平台

本项目的开发平台由软件平台与硬件平台两部分构成,形成软硬件协同的时间同步系统整体架构,旨在实现工业嵌入式环境中对时间同步配置、组网与监测的全面支撑。

软件平台方面,开发与运行环境依托于本地主机。主机配置为Intel(R) Core(TM) i5-9500 CPU @ 3.00GHz 六核心处理器;搭配 16.0GB RAM内存;运行 64 位 Windows 操作系统。在此主机上搭建了 Python 3.8 环境,作为可视化软件的运行基础。该软件以 PyQt 为主要开发框架,结合多线程与串口通信模块,构建图形化操作界面,实现对多网口嵌入式节点的识别、IP配置、拓扑组网、通信检测及时间同步状态的实时监控等功能。可视化软件具备良好的系统资源适配能力,可稳定运行,响应性能良好,界面交互流畅,满足对时间同步过程全程可视化的工程需求。

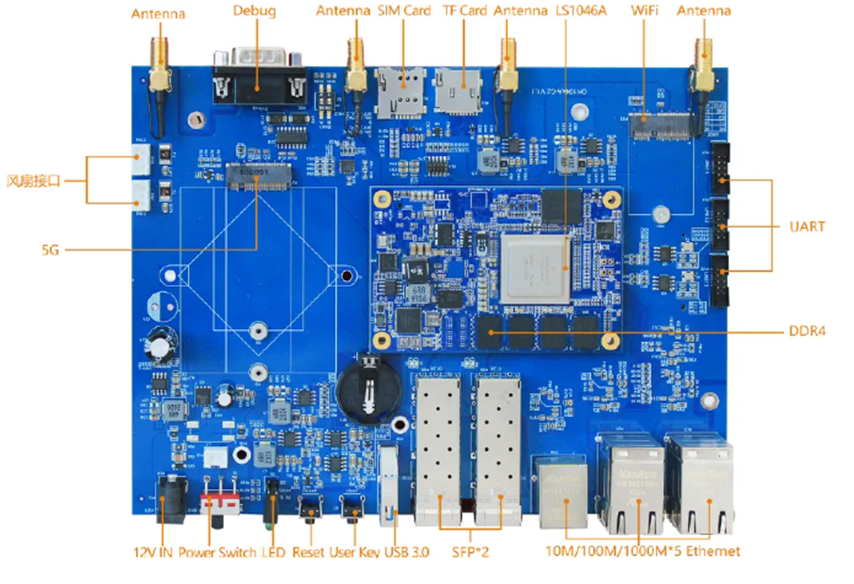

硬件平台方面,系统以 NXP 公司推出的 LS1046A 嵌入式多核通信处理器为核心,开发板具体实物图及接口介绍如下图2.1所示。LS1046A 芯片基于 ARM Cortex-A72 架构,提供四核 64 位处理能力,主频达 1.8 GHz,ARM Cortex-A72 架构。CPU原生支持7 个Ethernet:2 个SFP+接口(10Gb)和5 个1000Mbps。支持PCIe 3.0、SATA3.0、USB3.0、UART 、IIC等功能接口,以及Ubuntu、OpenWrt 操作系统,具备较强的数据处理和网络通信能力,适用于多节点同步网络的部署与透明中继场景的实现。各嵌入式节点均运行移植后的嵌入式 Linux 系统(内核为Linux 4.14.47 64bit),系统中已提前裁剪无关模块并集成了定制化的设备树、网卡驱动与串口管理模块,为同步软件运行与多网口数据转发提供支持。在节点时间同步功能方面,系统集成了 IEEE 1588 标准协议栈,分别采用开源的 ptpd 与 linuxptp 软件。ptpd 用于主从节点的同步控制,支持高精度同步参数配置与 servo 调节;linuxptp 则用于透明时钟节点的报文转发与延时修正,支持多网口同步报文处理。嵌入式设备通过串口与主控主机通信,接受用户命令,反馈状态信息,构成一个可控制、可观测、可配置的同步节点群。(具体的对于想复现的朋友,只要找一块能够运行ptpd 与 linuxptp 软件的开发板即可,本项目主要在于软硬件的协同创新,不侧重于硬件开发板)

四、方案详述

4.1 硬件集成方案

本项目基于 NXP LS1046A 多核通信处理器平台构建同步网络。该平台具有丰富的网络接口资源,集成四核 ARM Cortex-A72 处理器,配套多个独立以太网 MAC 控制器,支持高带宽、低时延的多网口并发通信,具备部署 IEEE 1588 精密时间协议(PTP)的硬件基础。

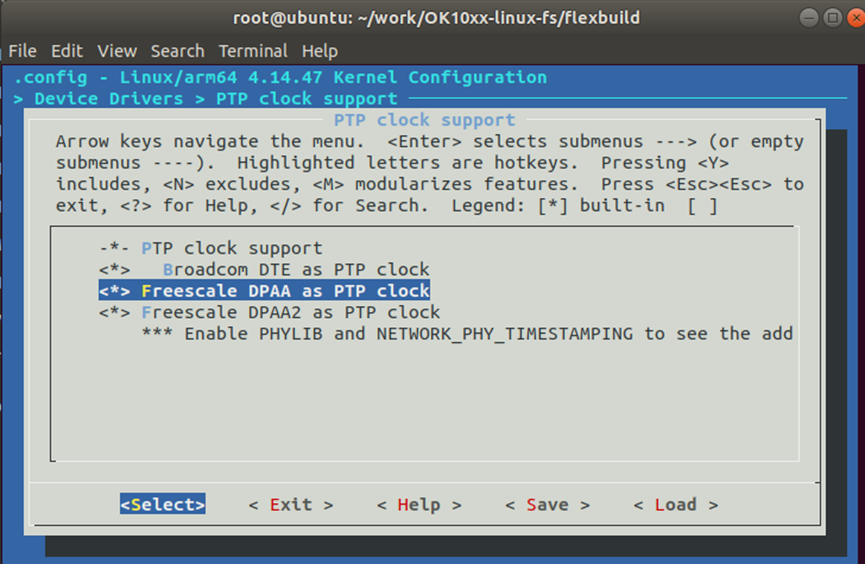

将 LS1046A 作为硬件实现 IEEE 1588 时钟节点,考虑到 PTPd和 LinuxPTP 的使用依赖于 Linux 环境,因此首先需要将 Linux 操作系统的镜像文件烧写到LS1046A的存储设备(EMMC)中,LS1046A软件镜像编译整体分为两部分,第一部分为启动第一阶段相关内容,主要包含了复位控制字、网络相关固件、安全相关固件等,整体被编译为一个大小为16M的firmware镜像。第二部分是Ubuntu文件系统。在编译镜像之前要配置好支持 IEEE 1588 协议堆栈运行的必要环境,分别是设备驱动程序和编译选项。详细步骤如下:首先运行 source setup.env 进入到 NXP 官方提供的 flexbuild 编译环境;其次进入到内核配置界面,配置之前要清除之前的编译记录,如下图所示为配置选项,表示启用 IEEE 1588 驱动支持和 DPAA 驱动支持;在配置完成后需要编译内核,重新生成Ubuntu 镜像,同时要修改设备树文件,将网口所绑定的时钟修改为DPAA 所驱动的 PTP 时钟;最后将编译好的内核、修改好的设备树文件烧写到 LS1046A 硬件平台,至此适用于IEEE1588协议栈运行的硬件环境搭建完毕。

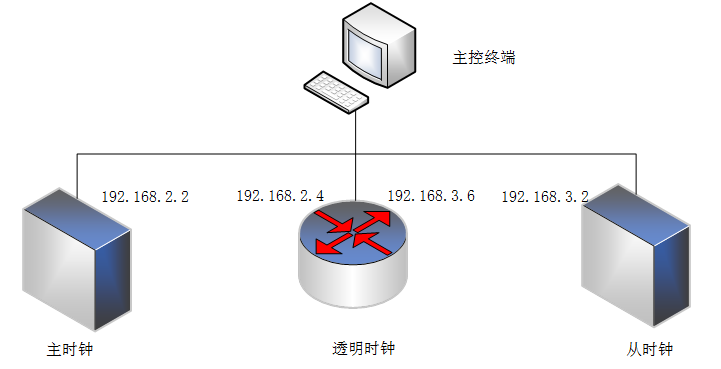

系统整体通信结构如下图所示。各 LS1046A 设备通过串口与主控终端连接,构成多节点下位机集群。在不同的应用场景下,设备可被配置为主节点、从节点或透明节点。通过修改设备树文件与内核配置,实现对以太网控制器的绑定、MAC 地址管理、PTP精准时间戳等功能。在设备驱动层,通过调试网卡驱动与系统时间源绑定逻辑,保障系统对 IEEE 1588 时间戳寄存器的精确访问。

透明时钟的设计为本系统的一大亮点。不同于传统的主从直连拓扑,透明节点具有多个物理网口,需在不同接口上分别配置独立 IP 地址,并实现同步报文的时间戳补偿与透明转发功能。在物理层,透明节点支持多跳路径下的时间同步,消除传输时延的累计误差,提高网络规模扩展能力。具体的配置中,系统允许用户为每一物理端口绑定独立逻辑接口,确保其能正确参与报文转发与时延修正计算。

4.2 软件实现方案

4.2.1 时钟同步软件

本项目在时间同步实现上采用 IEEE 1588 精密时间协议(Precision Time Protocol, PTP),该协议广泛应用于工业控制、能源系统、通信基站等对高精度时间要求较高的分布式系统中。IEEE 1588 协议通过在网络节点间交换时间戳报文,结合时延测量与漂移补偿,实现亚微秒级甚至纳秒级的时钟对齐。相比传统的 NTP 协议,PTP 支持硬件时间戳与透明时钟机制,能有效减少中间节点转发时延带来的同步误差,是构建高精度同步系统的关键技术基础。在本课题中,选用了开源社区广泛使用的两种 PTP 软件实现作为同步服务核心:linuxptp 和 ptpd2。这二者各具优势,适用于不同类型节点的同步任务。

linuxptp 是由 Linux 官方维护的 PTP 实现,提供了高效的透明时钟(Transparent Clock)与边界时钟(Boundary Clock)支持,具备良好的硬件接口兼容性与稳定性。在本系统中,透明时钟节点采用 linuxptp 提供的 ptp4l 工具,具体使用时的核心命令为“ptp4l -E -4 -H -i fm1-mac4 -m -i fm1-mac6”。其中 -E 表示启用每秒 1 次的增强对称时延机制;-4 表示使用 IPv4 协议;-H 表示启用硬件时间戳功能;-i 指定参与同步的网络接口,本设计中指定了两个网络接口(fm1-mac4 和 fm1-mac6),构成透明转发链路。该配置使透明节点具备中间转发与时延补偿能力,实现对主从同步路径的时间戳修正,从而提升多跳网络下的同步精度。

ptpd2 是基于 PTPv2 标准的另一开源实现,具有结构简洁、可配置性强、易于调试等优势。其在主从同步节点部署中展现了出色的灵活性。系统中配置主时钟的核心命令为“ptpd2 -i fm1-mac4 -MV -E”。其中,-i 指定同步接口;-M 表示设置节点为主时钟;-V 表示启用详细日志输出;-E 表示启用延时机制,以增强对网络变化的适应性。配置从时钟的核心命令为“ptpd2 -i fm1-mac6 -sV --servo:kp=0.32 --servo:ki=0.05 -E”。其中,-s 表示将节点设置为从时钟;--servo:kp/ki 明确了 PI 控制器中的比例增益与积分增益参数,用以控制从节点时钟频率调整的灵敏度与收敛速度。通过对 servo 控制器参数的微调,可在不同链路稳定性与同步精度要求下优化同步过程。

通过上述linuxptp与ptpd2搭配使用,本系统形成了“主—透明—从”结构的完整时间同步路径,其中 linuxptp 负责中间透明节点的转发与时延修正,ptpd2 负责主从节点之间的时钟传播与调节。二者协同工作,有效兼顾了网络路径修正能力与从节点稳定控制能力,保障了多跳环境下的同步稳定性与系统鲁棒性。此外,系统通过串口远程控制机制实现对 ptp 服务的动态启动与终止,配合 GUI 实现了对时间同步服务的可视化管理。同步参数如主从节点时钟相位偏差(offset)、往返平均链路传输时延(delay)及时钟频率偏移(drift)会被实时捕获并在界面中曲线化呈现,辅助用户分析同步过程中的抖动特性与系统误差演化趋势。

4.2.2 可视化监控平台实现方案

可视化监控平台采用 Python 与 PyQt 实现,构建统一的图形用户界面,实现设备控制、网络组网与同步监测的全流程支持。整体结构采用模块化设计,包括三个核心功能子系统:设备识别与多网口配置模块、拓扑构建与通信检测模块、时间同步控制与实时监控模块。各模块的具体实现如下所述。

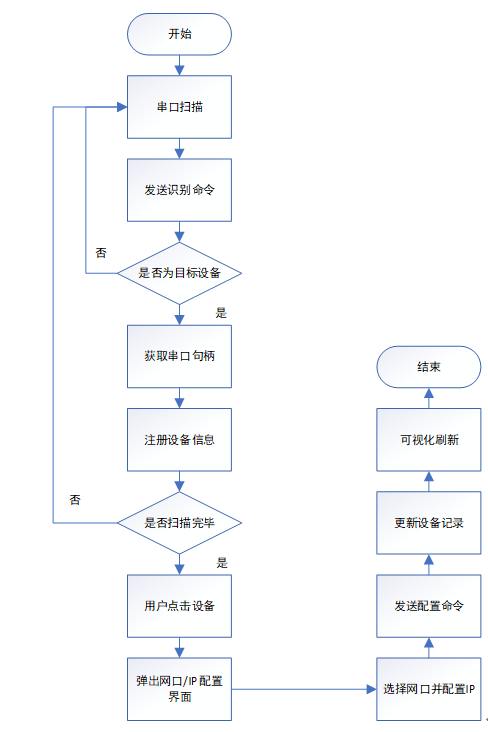

(1) 设备识别与 IP 配置模块

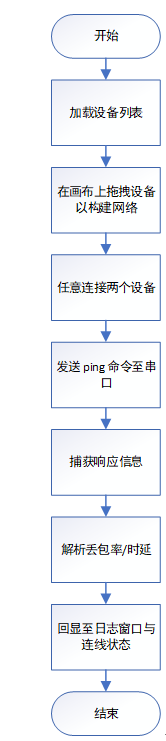

该模块负责通过串口扫描自动识别已连接的 LS1046A 设备,并将识别到的每一块开发板注册入设备列表。用户可点击任一设备,打开 IP 配置对话框,为其多个以太网接口(fm1-mac1~mac6)分别指定 IP 地址,是整个系统构建中下位机统一管理的基础环节。该模块核心流程如下图所示。

(2) 拓扑构建与连通性检测模块

该模块提供基于 QGraphicsScene 的画布式可视化操作平台,旨在为用户提供一个图形化、交互式的组网平台,使其能够直观地设计和验证设备间的网络连接关系。用户可将已识别设备通过图标拖拽至画布,自主构建所需网络拓扑结构。点击并连接任意两个节点后,系统自动触发基于串口远程命令的 ping 通信测试,判断网络连通性,并将检测结果通过日志输出与连线颜色实时反馈,其中绿色表示连通,红色表示断开。该模块核心流程如下图所示。

(3) 时间同步控制与状态监控模块

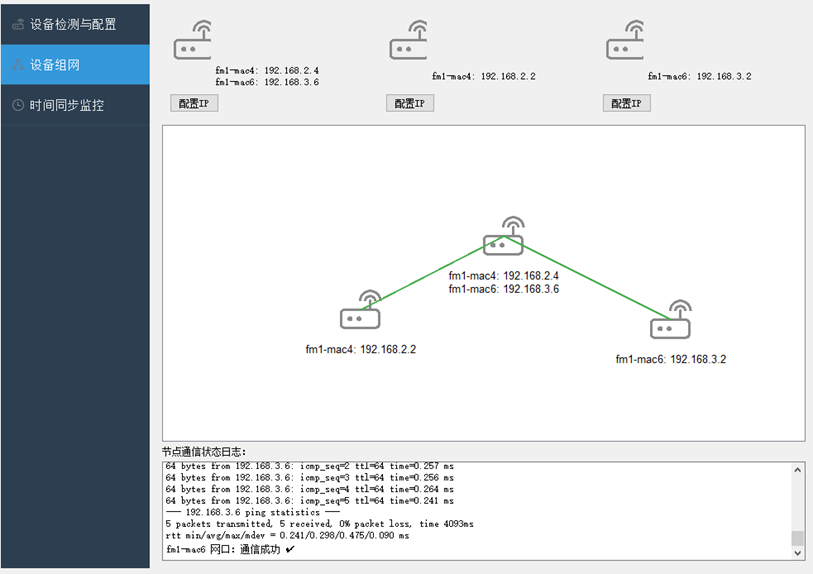

本模块是系统的核心功能,支持节点角色配置与同步过程的实时可视化监控。用户可对每个设备设置其同步角色(主时钟Master / 从时钟 Slave /透明时钟 Transparent Clock),并点击“启动时间同步”按钮启动时间同步服务。系统通过串口控制远程设备运行对应同步程序,并实时解析其标准输出中的主从节点时钟相位偏差(offset)、往返平均链路传输时延(delay)及时钟频率偏移(drift)等关键参数。这些参数将以 CSV 流的形式被捕获,并动态绘制成实时曲线,帮助用户观察同步过程的收敛性、稳定性及系统漂移。该模块核心流程如下图所示。

五、结果展现

本项目通过多模块的可视化界面截图与配套描述,全面呈现从设备识别、网络组网到时间同步控制与状态监测的全过程,体现系统的工程实用价值与交互体验优化程度。本节将配套展示各功能模块的实际运行界面,包括设备识别列表、IP配置、组网画布、拓扑连接检测效果以及同步参数曲线图等界面。系统性展示课题成果的实现效果,充分体现所设计平台的功能完整性、操作便捷性与工程适用性。

(1)设备识别与IP配置模块

首先,在设备识别与IP配置模块运行界面中,系统启动后通过串口自动扫描连接的多块 LS1046A 嵌入式设备。界面清晰地展示了每块设备的串口编号、连接状态、分配的板卡ID及描述信息。在识别成功后,用户可点击相应设备项进入网口 IP 配置界面,系统支持对多个以太网接口(fm1-mac1 ~ fm1-mac6)分别配置独立 IP 地址,界面设计简洁明晰,交互响应迅速。配置完成后,设备列表中自动更新对应网口的 IP 显示,辅助用户管理多网口透明时钟节点。设备识别与IP配置成功后的界面如下图所示。

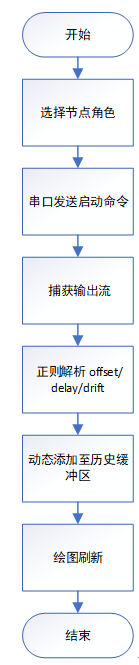

(2)设备组网与连通性检测模块

在设备组网与连通性检测模块中,系统提供图形化的拓扑构建界面。用户可将已识别的开发板设备以拖拽方式添加至组网画布中,通过连线方式定义逻辑通信关系。建立连接后,系统自动触发 ping 检测机制,对设备间连通状态进行验证,并以线条颜色标识联通与否,同时在日志区打印检测结果与延迟信息。该模块直观辅助用户构建复杂网络拓扑,并确保物理连接状态准确无误,尤其适用于多跳透明时钟网络场景下的调试需求。设备组网与连通性检测成功后的界面如下图所示。

(3)设备组网与连通性检测模块

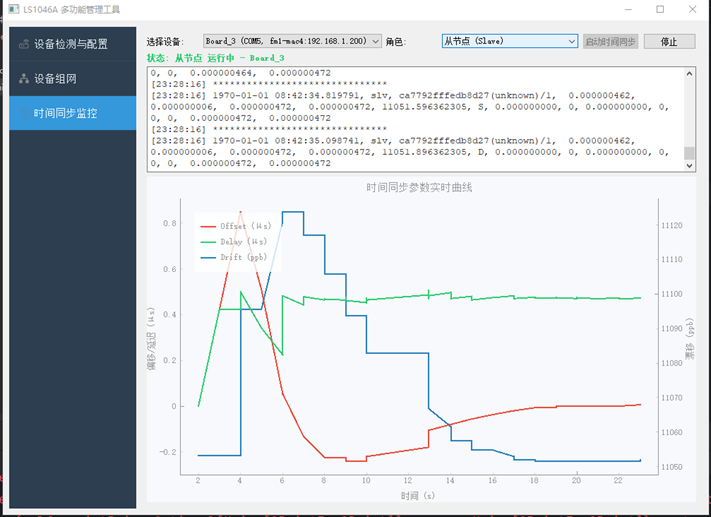

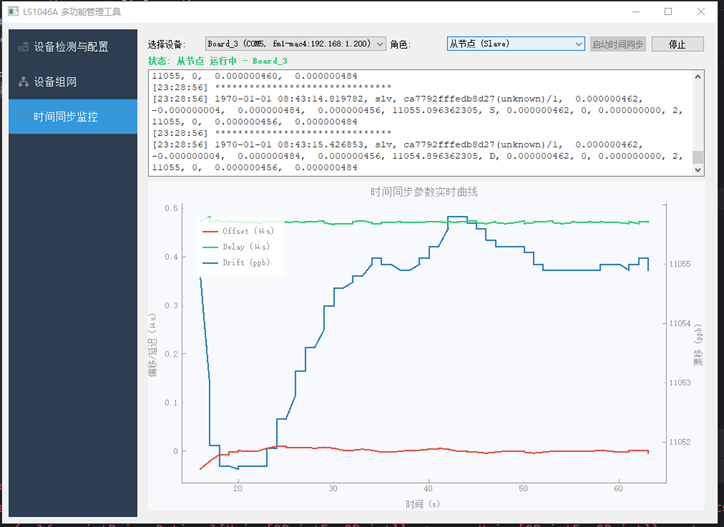

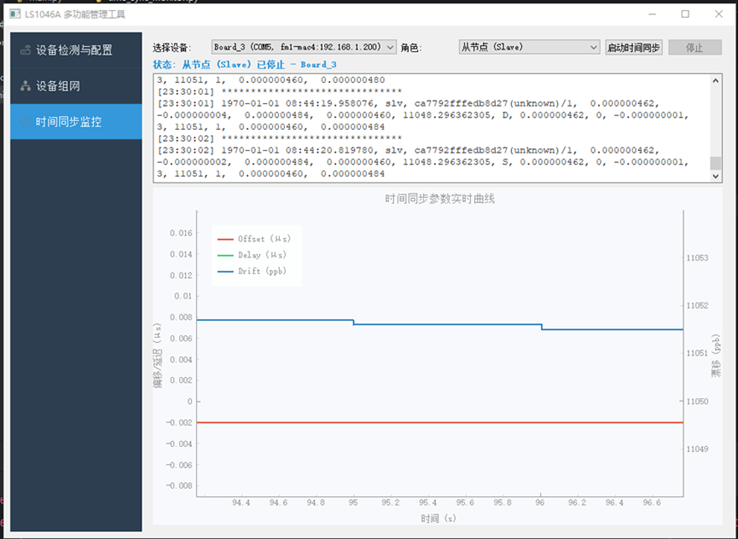

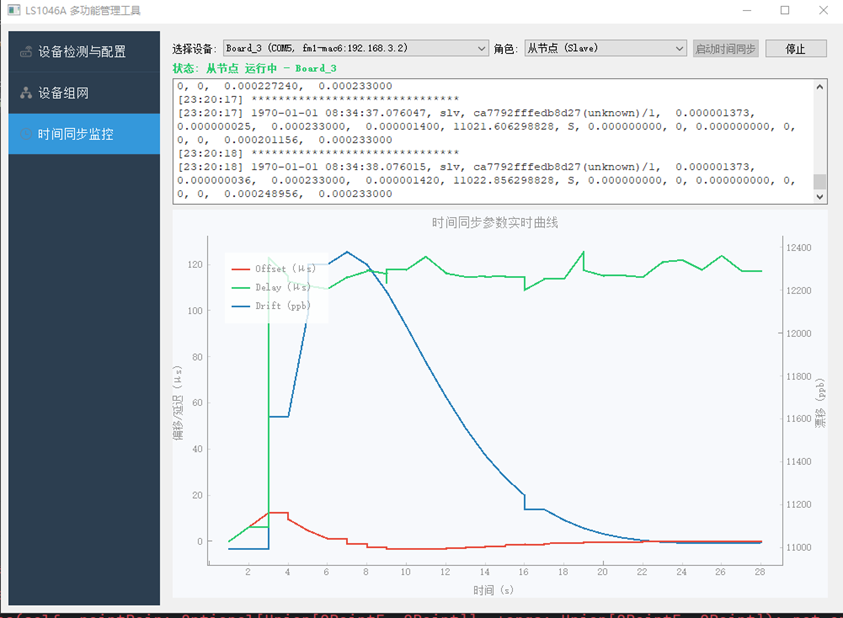

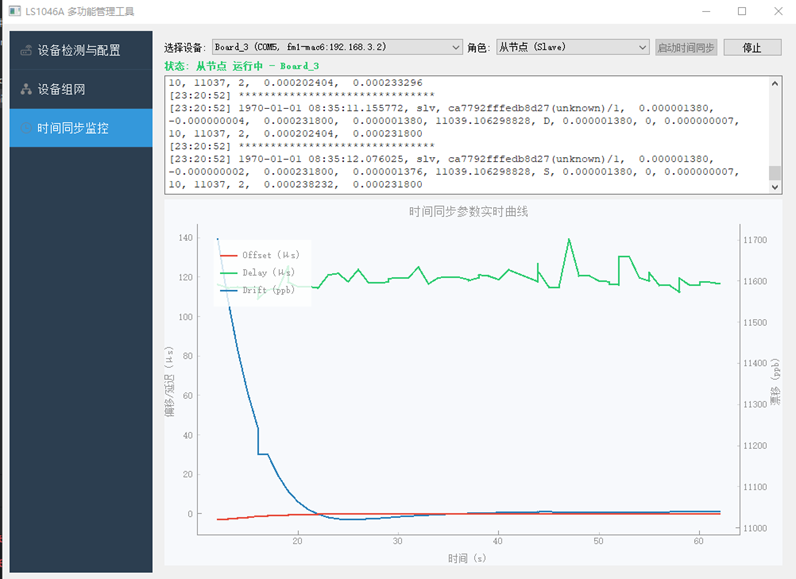

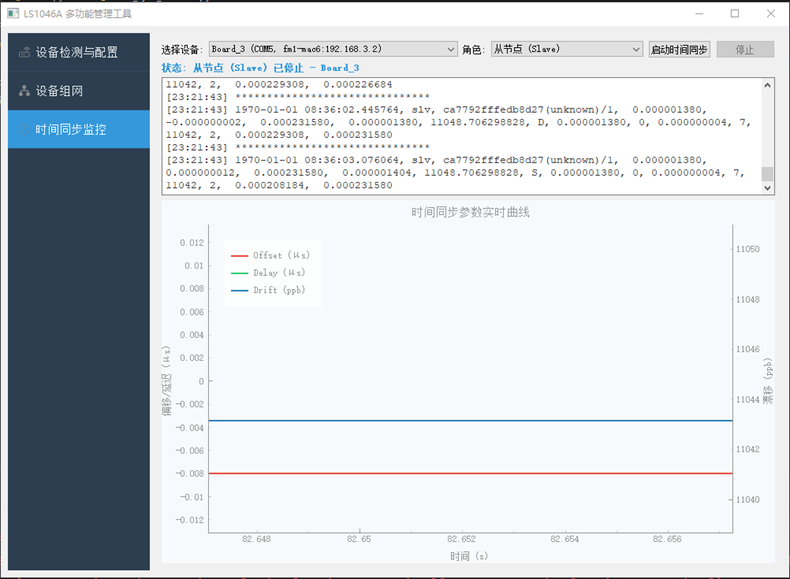

在时间同步控制与状态监测模块中,系统允许用户在界面中为每块节点配置角色(主节点、从节点或透明节点),在点击“启动时间同步”后,由上位机发送控制指令至各设备,启动时间同步程序。在同步运行过程中,系统实时读取从节点输出的 offset、delay、drift 等关键同步参数,并在曲线图中动态绘制。为验证系统在不同网络拓扑下的同步性能与功能完整性,分别进行了两类典型实验:一是主从节点直接连接的基础时间同步测试,二是引入透明时钟的多跳同步网络测试。实验旨在评估在不同同步路径结构下,系统对时钟偏移量(offset)、网络延迟(delay)及频率漂移(drift)等关键参数的控制能力,以及可视化界面对同步过程的呈现效果。

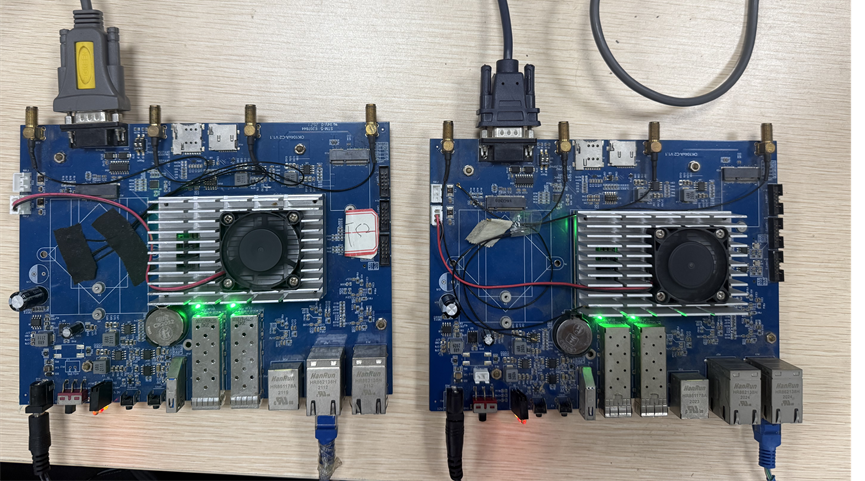

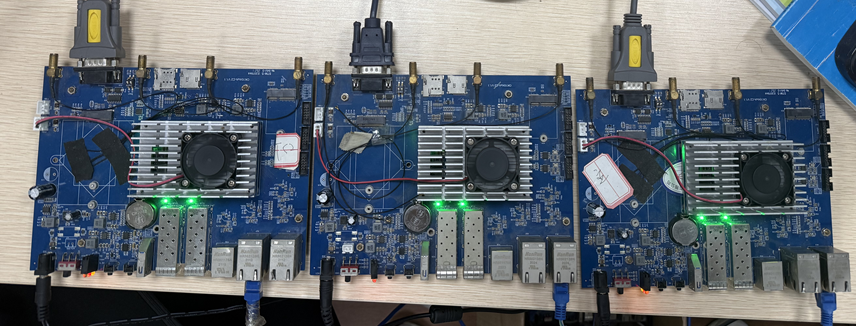

在主从节点直连实验中,将两块 LS1046A 开发板分别配置为主节点与从节点,通过一条以太网线直接连接形成最基本的同步结构。上位机软件通过串口对两节点下发同步启动指令,系统在从节点中启动时间同步服务并实时读取其输出信息,实物连接图如下图所示。

实验过程中,可视化界面实时绘制 offset、delay、drift 参数曲线。从下图实验曲线中可以观察到,offset 值在同步启动初期波动较大,但在经过若干同步周期后迅速收敛至微秒级范围内,drift 曲线趋于平稳,delay 保持稳定在合理范围,最终时钟相位偏差offset稳定在0.002微秒处,验证了系统在基础结构下实现纳秒级同步的能力。

在透明节点参与的多跳同步实验中,构建三节点网络拓扑,主节点与从节点间插入一块配置为透明时钟的中间节点,实物连接图如下图所示。

透明节点具备多网口转发能力,分别在不同接口上配置独立 IP,通过两条网线连接至主从两端,形成典型的主—透—从拓扑结构。系统通过图形化界面将三节点拖入画布并构建连接线,确认通信连通后启动同步流程。透明节点不主动参与时钟计算,但会对同步报文进行精确时间戳转发,确保同步路径时延被准确标定。从下图实验曲线中可以观察到,在引入透明节点的情况下,同步过程依旧具备良好的收敛性和稳定性,offset 与 drift 曲线变化趋势与基础直连结构基本一致且收敛速度更快,说明系统对多跳路径下的透明同步机制支持良好,透明节点的加入未对整体同步精度造成显著干扰。最终时钟相位偏差offset稳定在0.008微秒处,验证了系统在多跳网络下仍能实现纳秒级同步的能力。

通过上述实验,系统在功能与性能两个维度均体现出良好效果。用户可通过可视化平台对节点角色配置、同步过程控制及状态变化观测实现统一操作,系统运行数据以图形方式直观展示,极大提升了时间同步网络的实验效率与调试可视性,为进一步研究多节点精密同步提供了稳定的实验平台与工具支撑。后续还可扩展至更复杂拓扑结构及时钟失配干扰场景下的鲁棒性测试,以全面验证系统在实际工业环境中的适应能力。

基于LS1046A的时间同步系统设计与可视化监控平台开发源码:有需求可自行下载https://github.com/WUZ111/LS1046A

关于硬件平台,想复现的朋友,只要找一块能够运行ptpd 与 linuxptp 软件的开发板即可,本项目主要在于软硬件的协同创新,不侧重于硬件开发板。