STM32 FSMC接口与SDRAM交互详解

本文还有配套的精品资源,点击获取

简介:STM32微控制器的FSMC(灵活静态存储器控制器)支持与多种外部存储器高效通信,特别是SDRAM。本文档包含了一个示例,展示如何使用STM32的FSMC接口访问SDRAM。FSMC的配置涉及地址总线、数据总线、控制信号及时序。示例中将引导开发者完成SDRAM的初始化、地址映射和读写操作,从而扩展STM32应用中的存储能力。

1. STM32 FSMC介绍与优势

STM32微控制器的灵活静态存储控制器(FSMC)是为提供到外部存储器和并行接口设备的接口而设计的,它允许微控制器与外部存储器(例如SRAM、PSRAM、NOR Flash)以及外设(如LCD、ADC等)进行无缝连接。FSMC作为一种灵活的接口方案,为嵌入式系统的扩展和模块化设计提供了极佳的便利性。

FSMC的优势

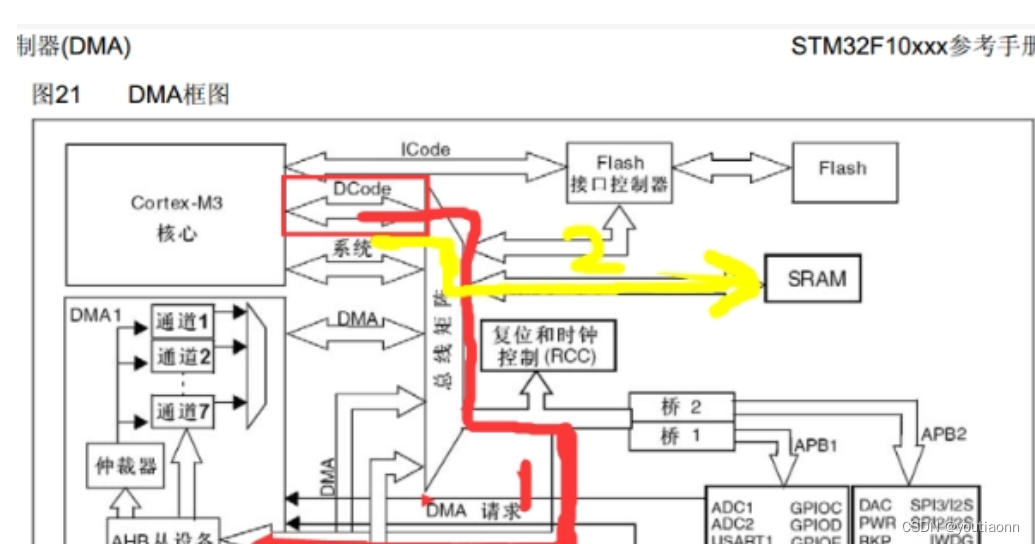

FSMC的优点首先体现在其灵活性上,它支持多种存储器类型和并行接口设备,这意味着开发者可以根据不同的项目需求选择合适的外部组件。其次,FSMC通过直接内存访问(DMA)模式提高了数据传输的效率,这对于需要高速数据处理的应用场景尤为重要。FSMC还具有低功耗优势,因为它支持多个电源模式,能够在不同的工作状态下调节能耗。

在接下来的章节中,我们将深入探讨FSMC的关键组成部分,解析其硬件结构和功能特性,以及如何在嵌入式系统中高效利用FSMC进行数据读写操作和系统集成。

2. FSMC的关键组成部分与功能

FSMC(Flexible Static Memory Controller)是ST公司的微控制器系列STM32中用于扩展静态存储器的外设,通过这个外设,可以方便地连接到并行存储设备,如SRAM、PSRAM、NOR Flash、LCD模块等。其优势在于提供一种灵活而高效的接口,为开发者提供了丰富而灵活的存储扩展解决方案。这一章节将重点介绍FSMC的关键组成部分以及其主要的功能特性。

2.1 FSMC的硬件结构解析

FSMC的硬件结构是其能够与不同存储设备通信的核心。理解这个结构对于合理配置和使用FSMC至关重要。

2.1.1 FSMC的引脚配置

FSMC的主要功能通过一组引脚实现,其中包括数据线、地址线、控制信号线和一些专用的信号线。例如,FSMC的NE(Noise Enable)引脚可以用于改善存储器读写时的数据完整性。在设计电路时,这些引脚需要根据存储设备的具体要求进行配置。

flowchart LR A[FSMC] -->|Data bus| B[Data lines D0-D15] A -->|Address bus| C[Address lines A0-A25] A -->|Control Signals| D[Control Lines,如 NE, NOE, NWE, NIOR, NIOW] A -->|Other Signals| E[Other Signals,如 NCE, NOISE]2.1.2 FSMC与CPU的接口

FSMC与CPU的接口定义了数据、地址和控制信号如何在两者之间传输。其接口的灵活性使得系统设计师能够优化对存储设备的访问速度和效率。

2.2 FSMC的功能特性

FSMC具备多种功能特性,这些特性在设计存储系统时提供了极大的便利性。

2.2.1 并行接口特性

FSMC支持多种并行接口模式,包括SRAM、PSRAM、NOR Flash以及LCD。这些接口模式通过编程配置FSMC的相关寄存器实现,如BANK结构和读写时序参数等。

| 存储器类型 | 配置模式 | 读写时序 | 用途 ||------------|----------|----------|------|| SRAM | ASYNC | 可编程 | 通用数据存储 || PSRAM | ASYNC | 可编程 | 动态数据存储 || NOR Flash | ASYNC | 可编程 | 固定数据存储 || LCD | SYNC | 固定 | 显示输出 |2.2.2 存储器类型支持

FSMC支持多种存储器类型,这使得它非常灵活和强大。可以将不同类型的存储器连接到一个FSMC上,只要它们被配置为不同的BANK。

// FSMC 转换到新的存储器类型配置的示例代码// 用于设置FSMC以连接NOR FlashFSMC_Bank1->BTCR[1] = 0x00001000; // 设置FSMC控制寄存器FSMC_Bank1E->BWTR[0] = 0x00000000; // 设置FSMC时序寄存器2.2.3 控制信号与时序管理

FSMC允许用户细致地控制与存储器通信时的各种信号时序,包括访问时间、保持时间、延迟时间等。这在高速存储器接口中尤为重要。

gantt title FSMC 信号时序控制配置流程 dateFormat YYYY-MM-DD section 读操作 CS setup :a1, 2023-04-01, 1d Address setup:after a1, 1d Data read :after a2, 2d section 写操作 CS setup :b1, 2023-04-03, 1d Address setup:after b1, 1d Data write :after b2, 2dFSMC通过其引脚配置、接口模式、存储器类型支持和时序控制提供了强大的静态存储解决方案,为嵌入式系统的设计者提供了必要的灵活性和效率。在本章节中,我们对FSMC的关键硬件结构进行了详细解析,并探讨了其关键功能特性。随着对FSMC理解的深入,接下来的章节将介绍FSMC与SDRAM通信的初始化配置方法,为深入应用这一技术打下坚实的基础。

3. SDRAM特性与应用场景

SDRAM(Synchronous Dynamic Random Access Memory)是一种同步动态随机存取存储器,是目前广泛使用的一种内存类型,具有高数据传输速率和良好的扩展性。本章节将深入解析SDRAM的工作原理和主要特性,并探讨其在嵌入式系统中的应用场景,对比SDRAM与Flash存储器的不同,以此来展示SDRAM在当前技术领域的重要性。

3.1 SDRAM技术概述

3.1.1 SDRAM的工作原理

SDRAM通过其同步特性,与CPU的时钟频率同步工作,能有效地提升数据存取速度。它采用了动态存储单元,每个单元由一个晶体管和一个电容组成,晶体管用作开关,电容用来存储数据信息的电荷。由于电容会有漏电问题,SDRAM需要周期性地进行刷新操作以维持数据不丢失。

SDRAM的工作流程涉及多个命令的执行,包括初始化、读写操作以及自刷新等。典型的SDRAM操作周期包括激活(ACT)、读取(READ)、写入(WRITE)和预充电(PRECHARGE)。在激活命令后,相应行列的存储单元被选中,数据传输到行缓冲区中,随后可以进行读取或写入操作。完成操作后,通过预充电命令将行缓冲区中的数据写回到存储单元,并关闭行缓冲区,为下一次操作做准备。

3.1.2 SDRAM的主要特性

SDRAM有多种类型,常见的有SDR(Single Data Rate)和DDR(Double Data Rate)。DDR SDRAM比SDR SDRAM快,因为它可以在上升沿和下降沿两次传输数据。此外,SDRAM支持突发模式(Burst Mode),允许在单个命令下连续读写多个数据,显著提高了数据吞吐量。

SDRAM的内部结构复杂,具有多个存储阵列和独立的bank。Bank的并行工作方式提高了内存的访问效率。此外,SDRAM还支持不同的延迟配置,如CAS延迟(CL),这是衡量内存性能的关键参数之一。

3.2 SDRAM在嵌入式系统中的应用

3.2.1 SDRAM应用场景分析

在嵌入式系统中,SDRAM通常用于运行操作系统和复杂应用软件。系统在启动时,通常会将操作系统代码和应用程序从非易失性存储器(如Flash)加载到SDRAM中,利用SDRAM的高速读写能力来提升执行效率。多任务操作系统中的任务切换、数据交换以及高速缓存等都需要依赖于SDRAM来实现。

此外,SDRAM还广泛用于图像处理和视频播放等需要大量内存的应用中。在这些应用中,SDRAM作为帧缓冲区,能够快速地读写大量图像数据,满足图形处理的实时性需求。

3.2.2 SDRAM与Flash的比较

SDRAM和Flash都是现代电子设备中不可或缺的存储介质,但它们在工作原理、速度、使用方式等方面有显著差异。SDRAM是易失性存储器,必须在供电的情况下才能保持数据。而Flash属于非易失性存储器,即使断电后仍能保存数据。

从速度角度看,SDRAM能够提供极高的数据读写速度,适合运行实时系统。相比之下,Flash的读写速度慢,且写入次数有限。因此,在需要高速数据访问的场合,SDRAM是首选。

然而,SDRAM也有其劣势,如成本高、功耗大、需要持续供电等。因此在选择存储器时需要根据实际应用场景的需求,考虑成本、功耗和性能等因素,决定使用SDRAM或Flash,或二者的组合。

在嵌入式系统中,SDRAM与Flash往往共同使用,互补长短。例如,系统固件存储在Flash中,而运行时变量存储在SDRAM中。

在本章节中,我们从技术层面对SDRAM的原理和特性进行了详细介绍,并对比了SDRAM与Flash存储器的差异。接下来的章节将详细探讨如何初始化FSMC和SDRAM,以及如何在嵌入式系统中进行地址映射与系统集成。

4. FSMC与SDRAM通信的初始化配置

4.1 FSMC初始化配置流程

在嵌入式系统中,FSMC(Flexible Static Memory Controller)提供了一种灵活的方式来连接外部存储器,如SRAM、PSRAM、NOR Flash、PC Card/NAND Flash等。而SDRAM作为动态随机存取存储器,因其高性能和低成本的特性,广泛应用于需要大量内存的嵌入式系统中。在这些系统中,FSMC与SDRAM的通信初始化配置是至关重要的第一步。

4.1.1 配置FSMC时钟源

FSMC时钟源配置对于FSMC的性能至关重要。FSMC的时钟(FMC_K)通常来源于系统时钟(HCLK),但也可以通过分频器来降低FSMC的工作频率,以适应不同的外部存储器要求。初始化FSMC时钟源通常涉及以下步骤:

- 计算所需的FSMC时钟频率。

- 选择合适的时钟源,并对其进行配置,以确保它满足FSMC的工作频率需求。

- 设置FSMC时钟的分频比例,以达到最佳的性能和功耗平衡。

// 示例代码:配置FSMC时钟源void FSMC_Clock_Config(void) { RCC->CFGR |= RCC_CFGR_PPRE2_DIV2; // 设置APB2时钟分频器为2分频 RCC->AHB3ENR |= RCC_AHB3ENR_FMCEN; // 使能FSMC时钟 // 注意:以上代码仅为示例,实际应用中需要根据具体硬件设计进行时钟配置}4.1.2 设置FSMC的参数

FSMC的配置参数包括读写时序、模式设置等,这些参数将直接影响到FSMC与SDRAM的通信效率。以下是一些关键参数的设置方法:

- 设置访问时间和延迟。

- 配置读写模式,如是否启用写缓存。

- 配置FSMC的内存映射和等待状态。

// 示例代码:配置FSMC参数void FSMC_Configuration(void) { FSMC_NORSRAM_TimingTypeDef timing = {0}; FSMC_NORSRAM_TimingTypeDef extendedTiming = {0}; FSMC_NORSRAM_TimingTypeDef writeTiming = {0}; FSMC_NORSRAM_TimingTypeDef extendedWriteTiming = {0}; // 配置读写时序参数(此处需要根据SDRAM的规格和时钟频率进行调整) timing.AddressSetupTime = 1; // 地址建立时间 timing.AddressHoldTime = 0; // 地址保持时间 timing.DataSetupTime = 2; // 数据建立时间 timing.BusTurnAroundDuration = 0; timing.CLKDivision = 2; timing.DataLatency = 0; timing.AccessMode = FSMC_ACCESS_MODE_A; // ...其他参数配置... // 设置FSMC参数 FSMC_NORSRAM_Init(&FSMC_NORSRAMDEVICE, &timing, &extendedTiming); FSMC_NORSRAM_Timing结构体用于配置基本的FSMC参数,而extendedTiming用于配置扩展的FSMC参数。}4.2 SDRAM的初始化序列

SDRAM的初始化序列相对复杂,包括了对SDRAM进行初始化设置,如模式寄存器的配置、刷新率的设定等,以确保SDRAM在FSMC的控制下稳定运行。

4.2.1 SDRAM预充电命令

SDRAM的预充电命令用于打开所有的存储单元,使得SDRAM在被访问前处于一个已知的状态。通常在设备上电后或者从休眠模式恢复后需要执行预充电命令。

// 示例代码:执行SDRAM预充电命令void SDRAM_Precharge(void) { __IO uint32_t tmpreg; tmpreg = FSMC_Bank1->SDRTR; tmpreg |= FSMC_SDRTR_PR; // 设置预充电位 FSMC_Bank1->SDRTR = tmpreg; // 执行预充电命令 // 此时应加入适当的延时等待SDRAM完成预充电}4.2.2 自刷新与模式寄存器设置

自刷新模式允许SDRAM在没有外部访问的情况下,定时自动刷新存储单元,保持数据不丢失。模式寄存器的配置则包括设置SDRAM的行列地址位宽、延迟时间等。这些设置对于SDRAM的稳定运行和性能提升至关重要。

// 示例代码:设置SDRAM模式寄存器void SDRAM_Mode Register_Config(void) { __IO uint32_t tmpreg; tmpreg = FSMC_Bank1->SDRTR; tmpreg &= ~(FSMC_SDRTR_MWID | FSMC_SDRTR_NRFS | FSMC_SDRTR_NC); // 清除旧的设置 tmpreg |= (FSMC_SDRTR_MWID_0WS | FSMC_SDRTR_NRFS_16 | FSMC_SDRTR_NC_12); // 设置模式寄存器的值 FSMC_Bank1->SDRTR = tmpreg; // 执行模式寄存器设置命令 // 此时应加入适当的延时等待SDRAM完成模式寄存器设置}初始化SDRAM是一个复杂且细致的过程,涉及到众多寄存器的配置和各种时序参数的设定。在实际应用中,开发者应遵循存储器制造商提供的规格书,通过细致的配置来确保存储器的可靠性和性能。

FSMC与SDRAM通信的初始化配置是嵌入式系统开发中的关键技术环节,它直接影响了系统的稳定性和性能。通过上述章节的介绍,我们对如何进行FSMC初始化配置和SDRAM的初始化序列有了深入的理解。这些知识为我们在第五章深入探讨地址映射与系统集成打下了坚实的基础。

5. 地址映射与系统集成

5.1 地址映射策略

5.1.1 内存空间的规划

在嵌入式系统中,内存空间的规划是至关重要的。一个良好的地址映射策略可以优化内存的使用效率,提高系统的性能。规划内存空间时,需要考虑以下几个方面:

-

静态与动态映射: 根据存储资源的特性选择静态或动态映射。静态映射适合于那些在系统启动时就已经确定的资源,而动态映射则允许在系统运行时根据需要来分配内存空间。

-

内存对齐: 为了获取最佳的性能,内存地址应该与数据宽度对齐。例如,在32位数据总线上,32位的数据访问应该从4字节对齐的地址开始。

-

优先级分配: 对于具有不同优先级的内存资源,需要合理规划地址空间,以确保高优先级的资源能够迅速响应。通常情况下,频繁访问的资源应该分配在低地址区间。

-

扩展性考虑: 设计地址空间时,应该预留足够的空间用于未来的扩展,这可以避免后续系统升级时出现地址冲突的问题。

5.1.2 地址线的连接方法

在将FSMC集成到系统中时,地址线的连接方法直接影响到内存的访问效率。正确的连接方法可以确保FSMC能够正确地与外设或内存模块通信。

-

多片设备的地址线设计: 当使用多片FSMC设备时,需要合理分配地址空间。通常需要通过地址线的高位来选择对应的FSMC设备。

-

地址总线的去抖动: 连接地址总线到FSMC时,需要确保信号稳定,避免由于信号干扰导致的地址读取错误。可能需要在硬件层面增加去抖动电路。

-

地址线的缓冲与驱动: 如果系统的工作频率较高或者地址线需要经过较长的传输路径,可能需要使用地址缓冲器或驱动器来保证信号的质量。

5.2 集成FSMC到系统中

5.2.1 硬件连接的注意事项

在硬件连接方面,将FSMC成功集成到系统中需要注意以下几点:

-

确保电源和地线连接正确: 对于FSMC这类高速接口,稳定的电源和地线布局对信号的完整性至关重要。

-

使用阻抗匹配: 高速信号在传输过程中可能会发生反射,使用阻抗匹配可以减少这种反射,改善信号质量。

-

信号布局的优化: 优化信号布线,避免长距离的并行走线,减少信号间的串扰。

5.2.2 软件层面的集成步骤

在软件层面,集成FSMC需要遵循一系列步骤,以确保其功能正确实现:

-

驱动开发: 编写或配置适合FSMC的驱动程序,该驱动程序应能够正确初始化FSMC模块并提供标准的内存访问接口。

-

内存测试: 在软件集成之后,进行内存测试是必要的。这可以验证地址映射是否正确,以及FSMC是否能够正常工作。

-

性能验证: 最后,通过一系列性能测试来验证FSMC集成后的系统性能是否达到预期。例如,通过基准测试程序来测量数据吞吐量和访问延迟。

通过以上硬件和软件层面的详细规划和配置,FSMC可以有效地集成到嵌入式系统中,提供所需的存储扩展和并行接口功能。这样不仅优化了系统的内存结构,也提高了系统的整体性能和数据处理能力。

6. 数据读写操作与FSMC使用

FSMC(Flexible Static Memory Controller)是STMicroelectronics(意法半导体)为其STM32系列微控制器提供的一种灵活的静态存储控制器。FSMC能够将微控制器的接口扩展到外部的存储器和设备上,比如SRAM、PSRAM、Flash、EEPROM、液晶显示器等。FSMC模块的使用,为开发者提供了极大的便利性,使得嵌入式系统的扩展变得更加灵活和高效。

6.1 数据读写操作原理

数据的读写操作是FSMC使用中最核心的部分。理解FSMC的读写时序,对于提高数据操作的稳定性和效率至关重要。

6.1.1 读操作的时序分析

FSMC的读操作涉及多个控制信号的精确时序,以确保从外部存储器正确读取数据。以下是读操作的关键步骤:

- 地址信号被发送到外部存储器。

- 存储器使能(NExE)和输出使能(NOE)信号被激活。

- 数据被外部存储器放置到数据总线上。

- FSMC捕获数据并将其传递给CPU。

以下是相应的FSMC读操作时序图:

sequenceDiagram participant CPU participant FSMC participant SDRAM CPU->>FSMC: 请求读取数据 FSMC->>SDRAM: 发送地址及控制信号 SDRAM->>FSMC: 输出数据 FSMC->>CPU: 传递数据确保读操作时序的准确实现,需要在FSMC初始化阶段正确设置相关的时序参数。

6.1.2 写操作的时序分析

写操作与读操作类似,但增加了写使能(NWE)信号。以下是写操作的步骤:

- 地址信号和数据被发送到外部存储器。

- 存储器使能(NExE)、输出使能(NOE)和写使能(NWE)信号被激活。

- 数据被写入外部存储器。

FSMC的写操作时序图如下:

sequenceDiagram participant CPU participant FSMC participant SDRAM CPU->>FSMC: 请求写入数据 FSMC->>SDRAM: 发送地址及数据和控制信号 SDRAM->>SDRAM: 写入数据在写操作中,控制信号需要精确的时序来确保数据的正确写入。

6.2 FSMC接口代码示例分析

接下来,我们通过一个简单的代码示例,来分析如何使用FSMC接口进行数据读写。

6.2.1 代码结构与逻辑

下面的代码段演示了如何通过FSMC接口对SDRAM进行写操作:

#define SDRAM_START_ADDR (u32)(0xD0000000)#define SDRAM_END_ADDR (u32)(0xD3FFFFFF)void FSMC_SDRAM_Write(u32 startAddress, u32 endAddress, u8 *data) { u32 i; u32 *ptr = (u32 *) startAddress; u32 size = (endAddress - startAddress) / sizeof(u32); for (i = 0; i < size; i++) { *ptr++ = *((u32 *) data); data += sizeof(u32); }}6.2.2 代码中的关键函数与变量

在这个例子中,我们定义了SDRAM的起始地址 SDRAM_START_ADDR 和结束地址 SDRAM_END_ADDR 。 FSMC_SDRAM_Write 函数接收起始地址、结束地址和要写入的数据指针。

-

u32表示一个32位无符号整数。 -

size变量计算出需要写入的32位数的数量。 -

ptr是一个指针,指向SDRAM中的当前位置。

在实际应用中,你可能还需要初始化FSMC,设置SDRAM控制器的参数,并确保时序正确配置。

以上章节内容展示了FSMC在数据读写操作中的应用,以及如何通过代码实现对FSMC接口的操作。理解这些原理和步骤对于高效使用FSMC至关重要。接下来的章节将探讨地址映射策略和FSMC在嵌入式系统中的集成方式。

本文还有配套的精品资源,点击获取

简介:STM32微控制器的FSMC(灵活静态存储器控制器)支持与多种外部存储器高效通信,特别是SDRAM。本文档包含了一个示例,展示如何使用STM32的FSMC接口访问SDRAM。FSMC的配置涉及地址总线、数据总线、控制信号及时序。示例中将引导开发者完成SDRAM的初始化、地址映射和读写操作,从而扩展STM32应用中的存储能力。

本文还有配套的精品资源,点击获取