FX10/20 (CYUSB401X)开发笔记3-固件配置_cyusb4024

上个笔记导入了FX20的固件,大概介绍了固件的结构,本周介绍下固件的配置。

(FX20和FX10的固件是通用的)

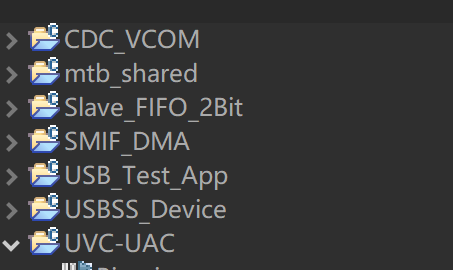

FX20的固件demo有很多,如下:

个人感觉使用UVC-UAC这个demo修改为自己的应用好一些,因为这个demo比较全面,内容多,配置也多。

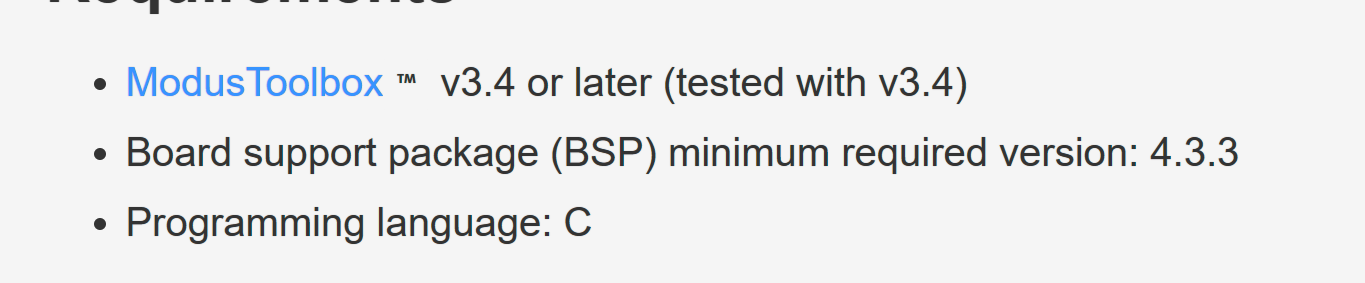

要使用这个demo,首先读一下readme.md从这个文件中可以看到一些关键信息:

比如demo的软件环境:

还有编译链工具环境,这里就不截图了

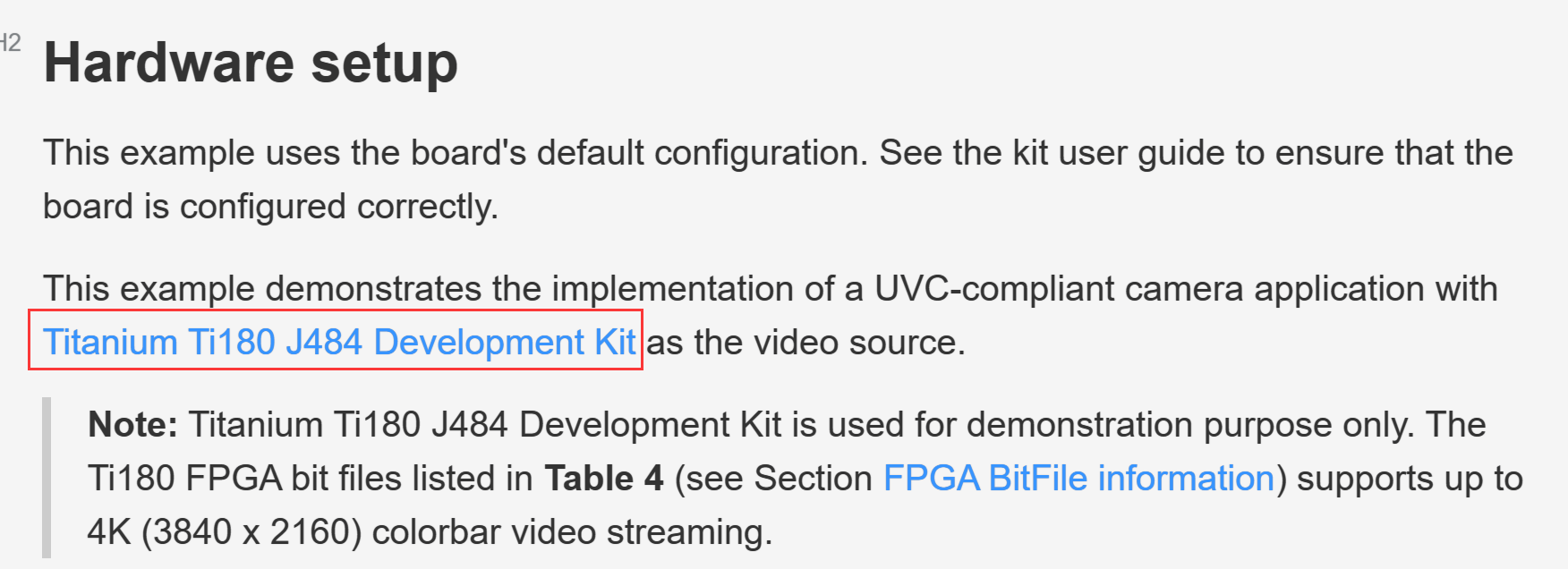

demo对应的硬件是:后期我们会根据这个硬件查看原理图,查看代码的GPIO怎么配置的。

文档中还介绍了一些demo的架构,初始化流程等,今天先看下配置的选项:

对于一些不懂的配置,先保持默认好了。

1 USB_CONN_TYPE:

选择默认的USB连接速度:

CY_USBD_USB_DEV_SS_GEN2X2(FX20)、CY_USBD_USB_DEV_SS_GEN2(FX10)、CY_USBD_USB_DEV_SS_GEN1X2(超高速第一代双通道)、

CY_USBD_USB_DEV_SS_GEN1(超高速第一代)、CY_USBD_USB_DEV_HS(高速)和CY_USBD_USB_DEV_FS(全速)

2 LVDS_LB_EN 启用链路环回

1u\' 启用链路环回

\'0u\' 禁用

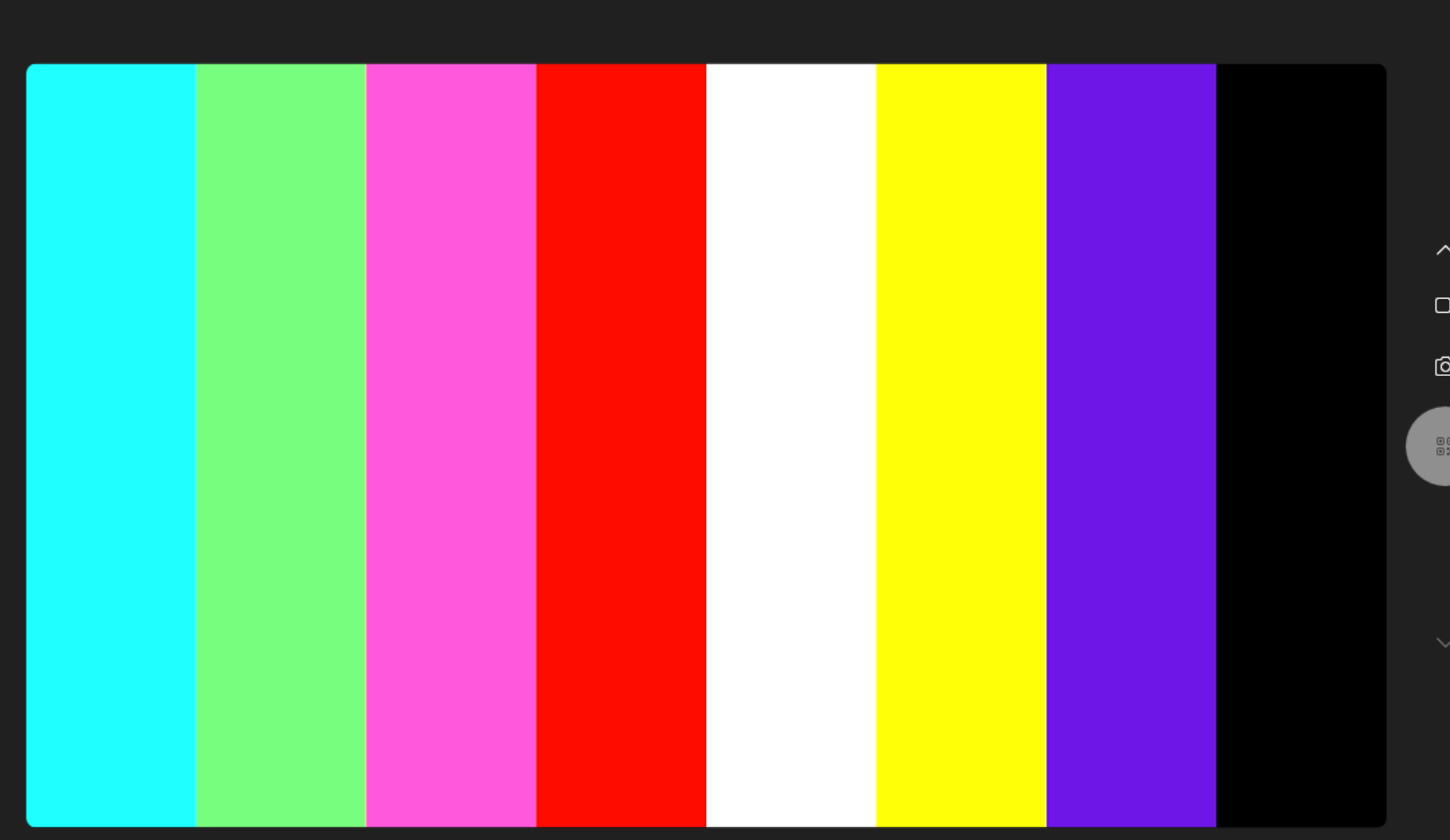

意思是说FX20内部有一个回环设置,当使能的时候,芯片会自动从 内部向电脑发uvc彩条视屏流,实验结果如下:下个笔记做这个

3 LVCMOS_EN 选择 LVCMOS/LVDS

\'1u\' 选择 LVCMOS

\'0u\' 选择 LVDS

FX20 对接FPGA 的接口有LVCMOS和LVDS,选用哪个,根据自己实际情况选择

4 LVCMOS_DDR_EN 选择 LVCMOS 时钟配置

\'1u\' 选择 LVCMOS DDR 时钟

\'0u\' 选择 LVCMOS SDR 时钟

选择和FPGA对接的接口的数据随路时钟是双沿还是单沿。

如果LVCMOS_EN 设置了 LVDS,这里的时钟配置必须改成SDR时钟。

5 WL_EN 选择宽链路或窄链路

\'1u\' 选择 32 位/宽链路(WideLink)

\'0u\' 选择窄链路(Narrow Link)

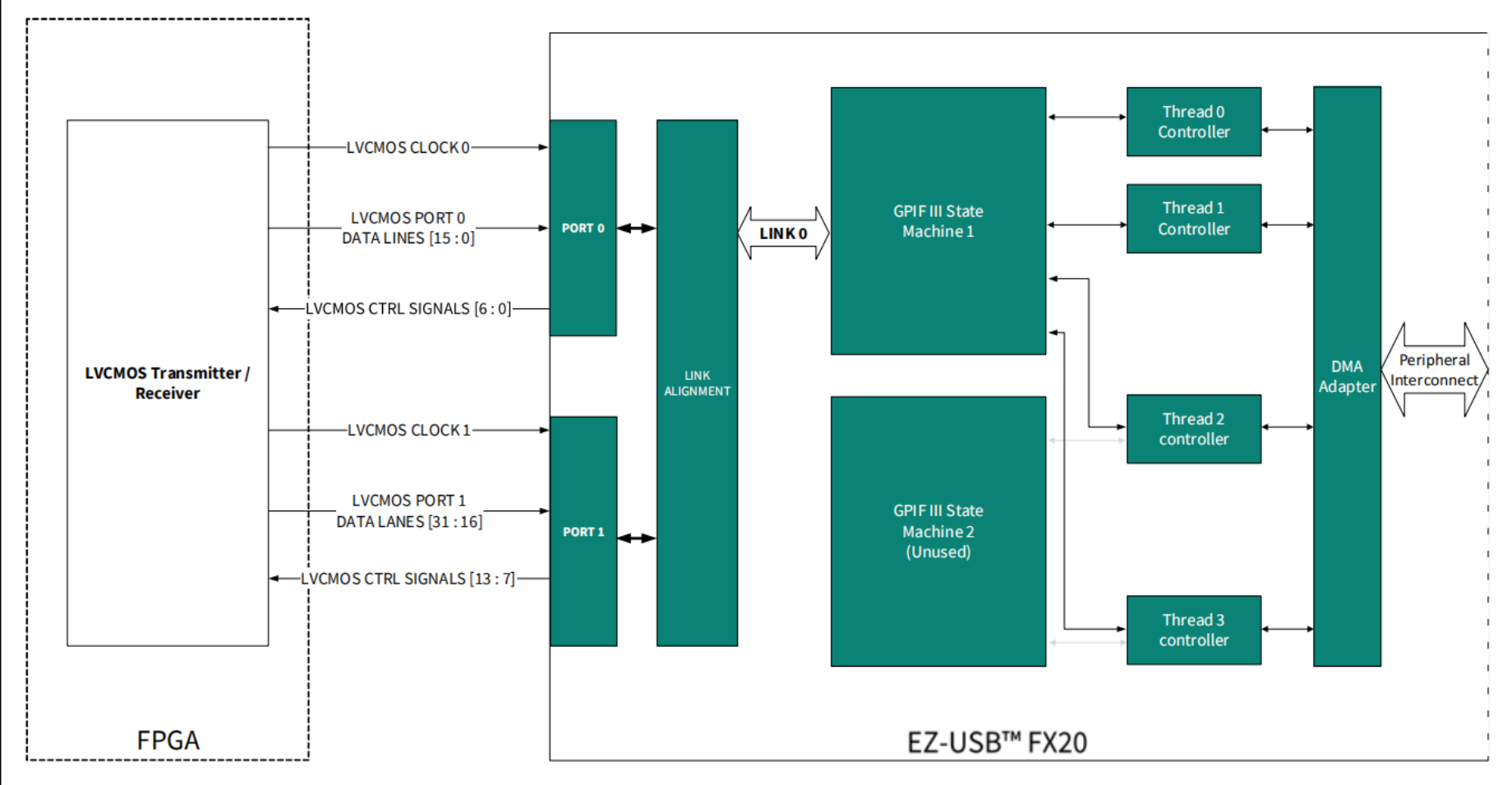

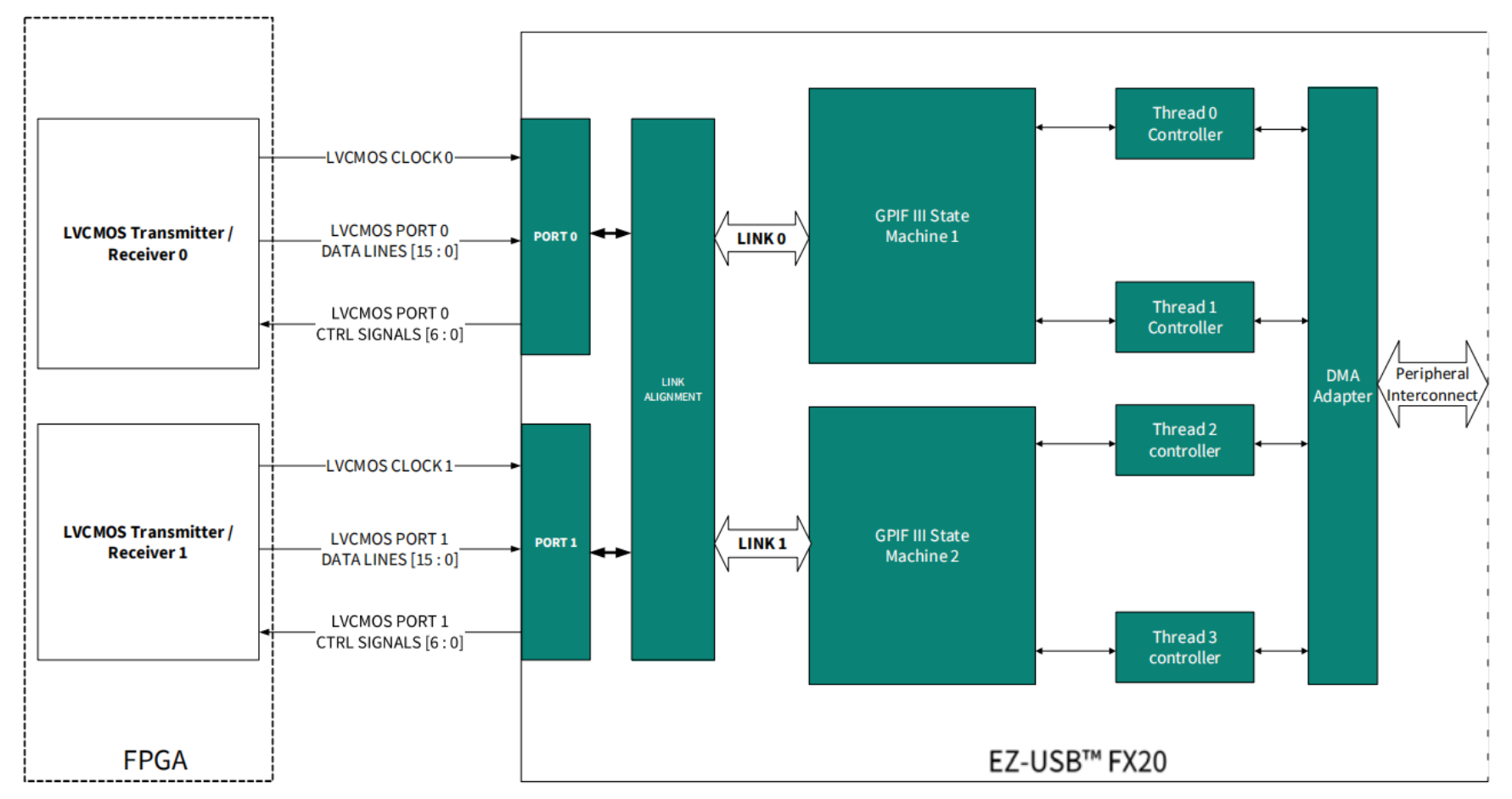

这个意思是说选择Fx20内部数据传输的方式,有两种方式:

wide link:所有的THread controller 都挂在 GPIF MACHINE1上:

Narrow link :2个 GPIF 状态机 MACHINE 各连接2个port

6 PORT1_EN 选择 LVCMOS/LVDS 端口

\'1u\' 选择 PORT1

\'0u\' 选择 PORT0

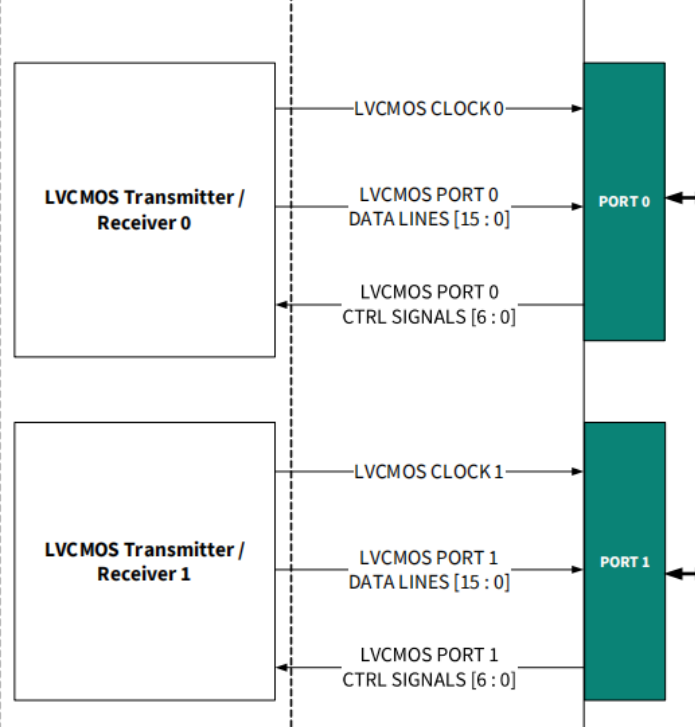

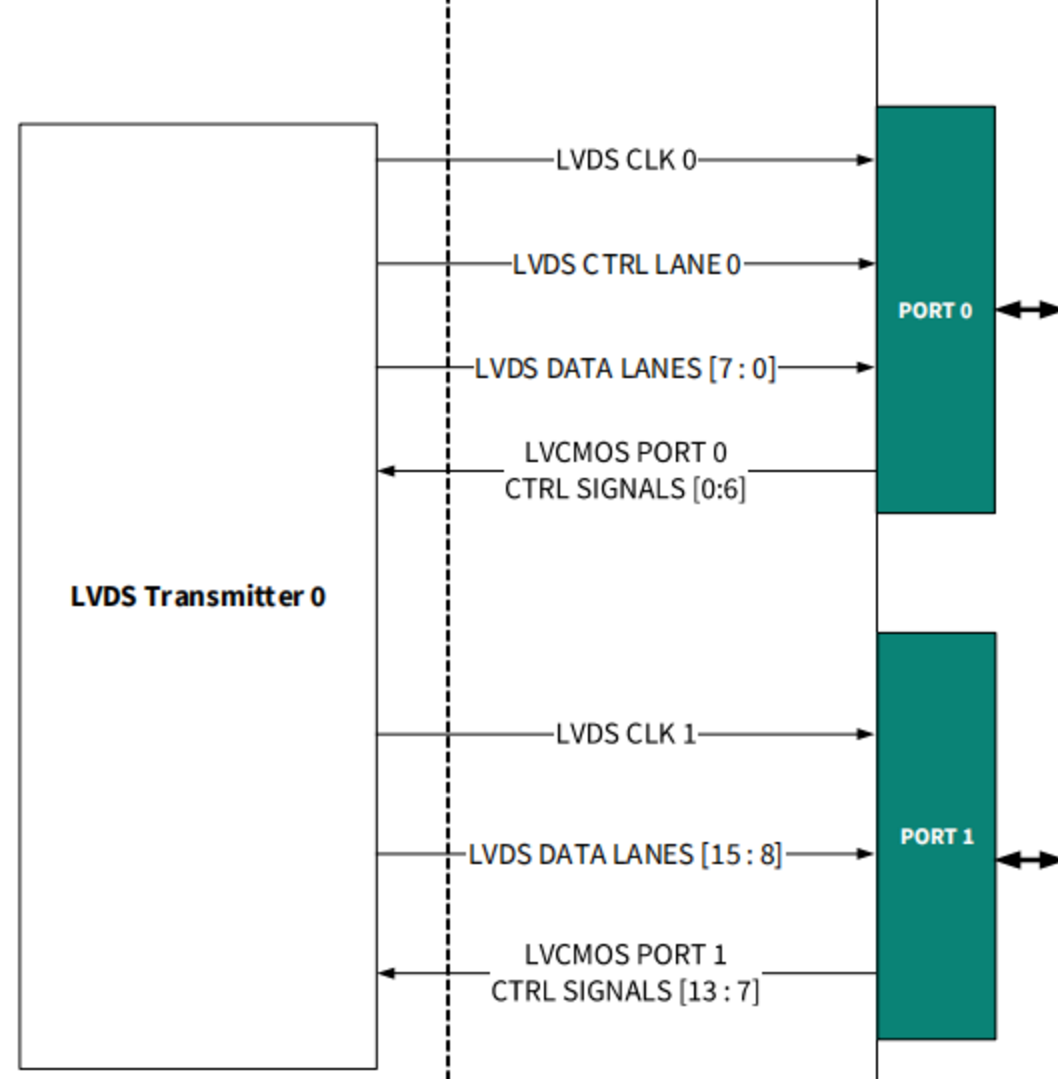

PORT0/1:对接 FPGA的两组信号:

LVCMOS:

LVDS:

上个选项如果选择了wide link,则内部代码是PORT0 和1都使用的

7 INTERLEAVE_EN 启用 PORT0 线程交错

\'1u\' 在 PORT0 上启用线程交错

\'0u\' 选择单线程

Fx20内部收到Fpga的数据以后,会通过DMA发送到上位机,内部有线程控制,这里选择是否启动线程交错

8 FPGA_ENABLE 选择 FPGA 作为数据源

\'1u\' 如果 FPGA 连接到 EZ-USB™ FX20

\'0u\' 禁用 FPGA 接口

估计是测试用的,一般都需要FPGA吧

9 FPGA_ADDS_HEADER UVC 头添加

\'1u\' FPGA 添加头

\'0u\' EZ-USB™ FX20 添加头

UVC的头可以是fx20 CPU加,这个情况下,数据到了FX20以后,会触发 FX20的中断,然后cpu加UVC的头。

一般来说FPGA做这个比较好。

10 AUDIO_IF_EN 启用集成 UAC 功能

\'1u\' 启用

\'0u\' 禁用

是否启用UAC功能,我这里禁止了,我不需要这个功能。

11 USBFS_LOGS_ENABLE 通过 USBFS 端口启用调试日志

\'1u\' 调试日志通过 USBFS 输出

\'0u\' 调试日志通过 UART (SCB1) 输出

这里是指日志的调试输出,这个FX20芯片内部有个专用的USBFX设备,和FX20是独立的,这个设备可以在电脑上枚举成一个串口设备,然后打印内部的信息,当然这里也可以使用串口打印,

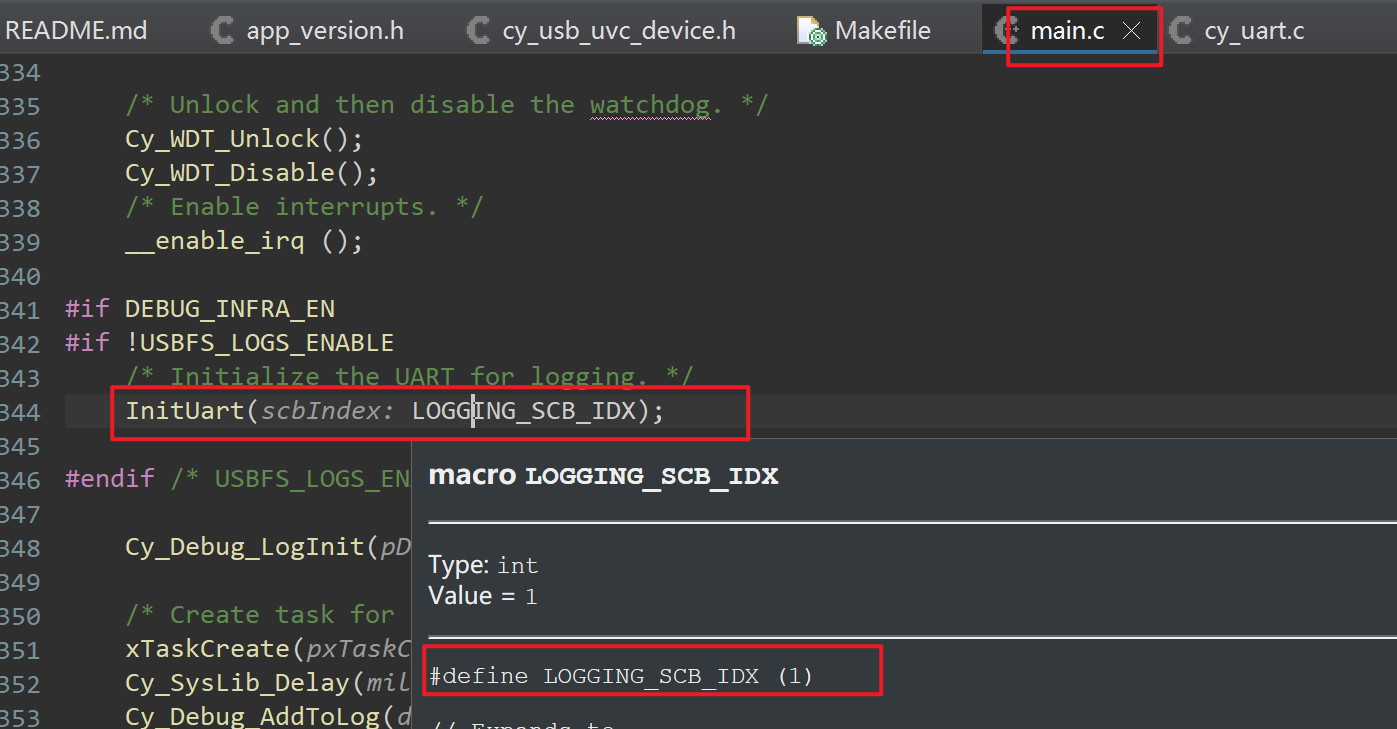

这里注意这个打印信息的前提是以下这个选项是打开的:

12 USB3_LPM_ENABLE 启用 USB LPM 处理

\'1u\' 启用 USB LPM 处理

\'0u\' 禁用

是否启动低功耗。

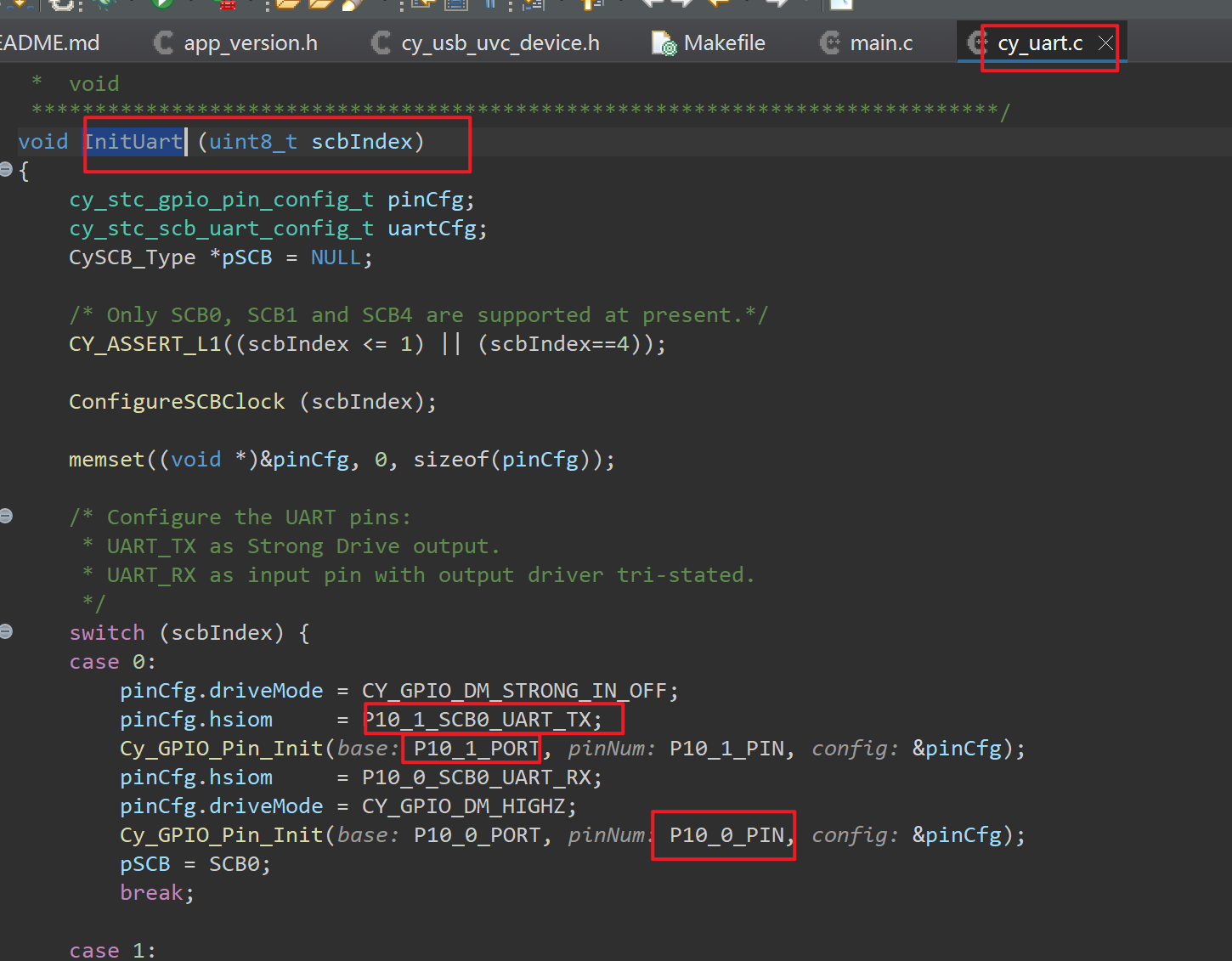

以上是一些基本的配置,根据自己的情况设置就好了,我这里debug使用了UART ,注意,uart打印信息是可以选择串口使用硬件上的哪个GPIO的:

默认P8_1_PORT是TX,P8_0_PIN是RX.

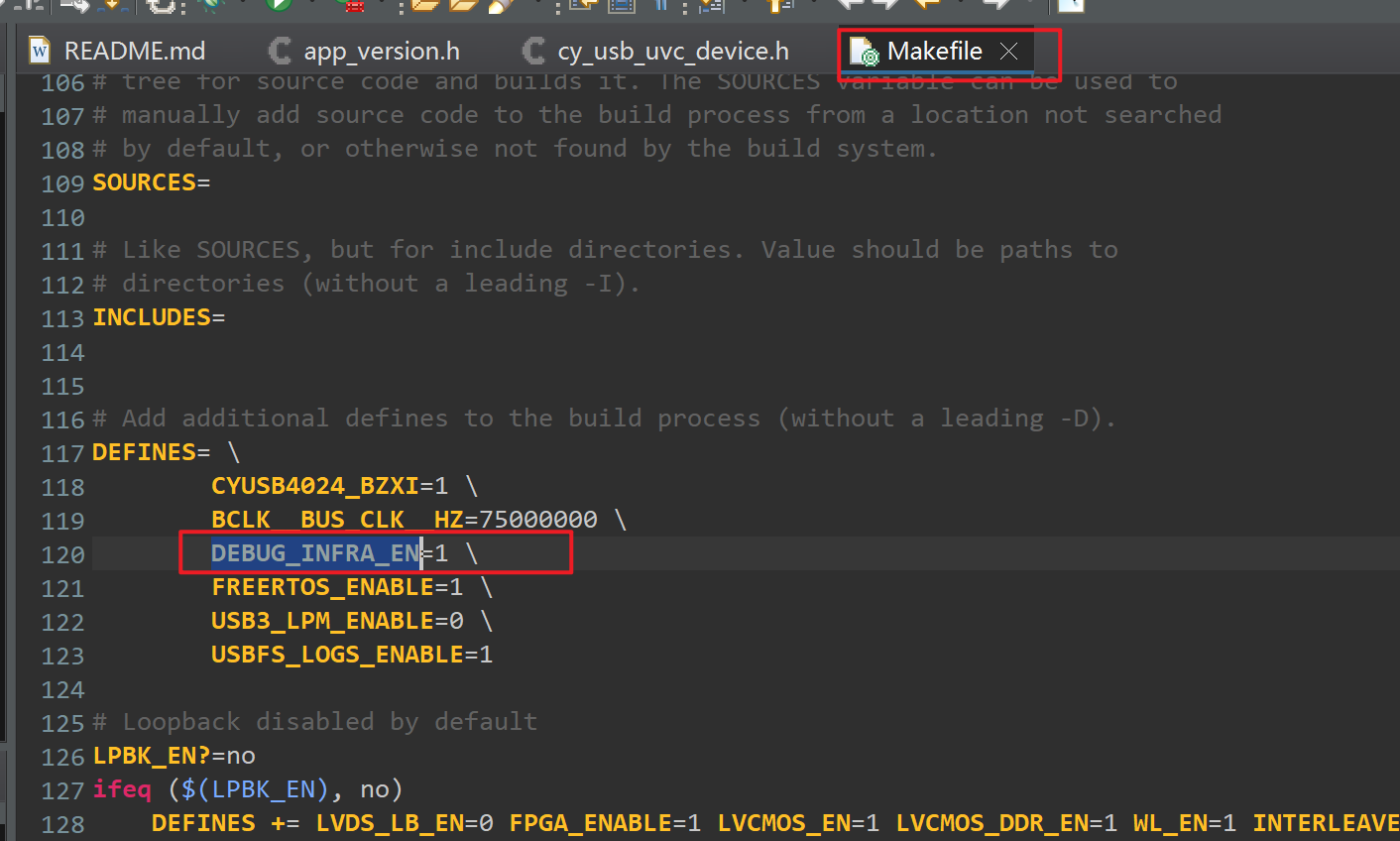

我这里makefike 配置如下:

# Add additional defines to the build process (without a leading -D).DEFINES= \\ CYUSB4024_BZXI=1 \\ BCLK__BUS_CLK__HZ=75000000 \\ DEBUG_INFRA_EN=1 \\ FREERTOS_ENABLE=1 \\ USB3_LPM_ENABLE=0 \\ USBFS_LOGS_ENABLE=0# Loopback disabled by defaultLPBK_EN?=noifeq ($(LPBK_EN), no) DEFINES += LVDS_LB_EN=0 FPGA_ENABLE=1 LVCMOS_EN=0 LVCMOS_DDR_EN=0 WL_EN=1 INTERLEAVE_EN=0 PORT1_EN=0 FPGA_ADDS_HEADER=1 AUDIO_IF_EN=0 INMD_EN=0else DEFINES += LVDS_LB_EN=1 FPGA_ENABLE=0 LVCMOS_EN=0 LVCMOS_DDR_EN=0 WL_EN=0 INTERLEAVE_EN=0 PORT1_EN=0 FPGA_ADDS_HEADER=0 AUDIO_IF_EN=1 INMD_EN=0endif下个笔记先弄个彩条实验看看图像吧