CH347使用笔记:CH347作为FPGA下载器的几种方式

CH347简介

CH347是一款高速USB总线转接芯片,通过USB总线提供异步串口、I2C同步串行接口、SPI同步串行接口和JTAG接口等。JTAG接口最高支持60Mhz。

详细介绍:

CH347-高速USB转串口、JTAG/SWD、SPI、I2C芯片介绍

CH347下载FPGA程序的三种方式

- 使用OpenOCD

OpenOCD(Open On-Chip Debugger)作为开源的硬件调试器,除了可以对嵌入式芯片进行下载和调试,其实还支持一些型号的FPGA下载。

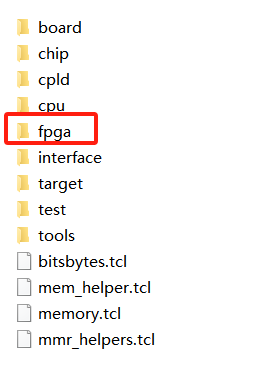

在OpenOCD目录中的share\\openocd\\scrips目录中可以看到支持的FPGA型号。

具体使用可参考

CH347应用–USB TO JTAG进行FPGA调试下载

- 使用OpenFPGALoader

类似于成熟的openOCD项目,openFPGALoader主要专注于对FPGA的固件下载,支持Xilinx, Altera/Intel, Lattice, Gowin等常见FPGA。

项目链接:https://github.com/ZhiyuanYuanNJ/openFPGALoader/tree/master

目前支持的FPGA型号如下:

https://trabucayre.github.io/openFPGALoader/compatibility/fpga.html

具体使用可参考:

CH347应用 USB转JTAG功能:开源项目openFPGALoader实现对FPGA高速下载

- 使用VIVADO xvcd

Xilinx Virtual Cable Daemon(xvcd)是Xilinx推出的基于 TCP/IP协议 的虚拟调试工具,主要用于替代传统的平台电缆 (如 Impact 工具)实现FPGA的远程调试和程序加载。

具体使用流程如下:

1、下载编译xvcd-ch347。

https://github.com/AIOT-CAT/xvcd-ch347

2、运行程序

首先使用-h,查看使用说明

ch347_xvcd.exe -h Usage: -h, --help display this message -a, --address <host add xxx> specify host address, default is 127.0.0.1 -p, --port <port num> specify socket port, default is 2542 -i, --index <index num> specify CH347 index, default is 0 -s, --speed <ch347 speed> specify CH347 JTAG speed, default is 30MHz一般使用时需要关注JTAG速率,一般单纯下载程序速率可以设置的稍高,程序固化时速率不宜过高。

设置JTAG速率3.75Mhz:

xvcd_ch347.exe -s 3750000Open CH347 Succes.CH347:[0] init done.可以看到CH347成功打开,程序不要关闭,随后打开vivado。

3、vivado连接CH347

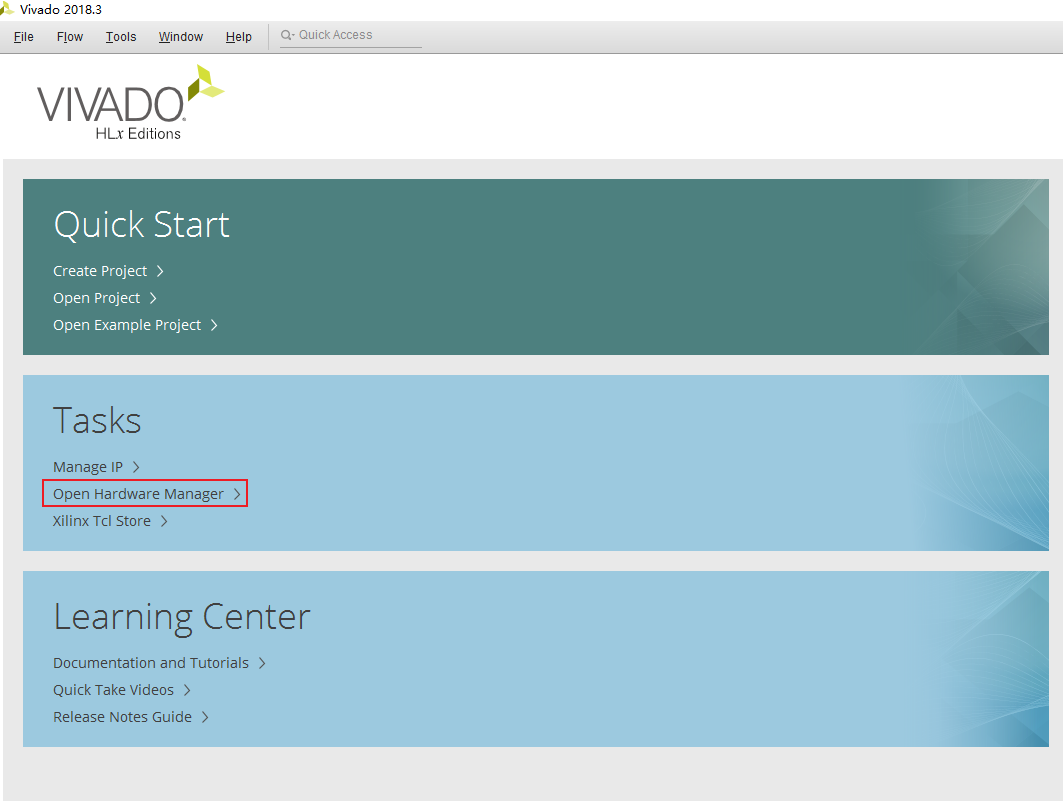

初始界面打开硬件管理。

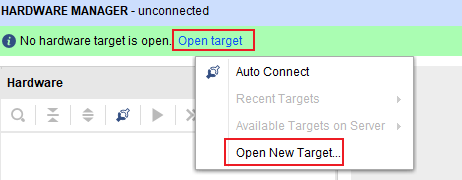

点击New Target

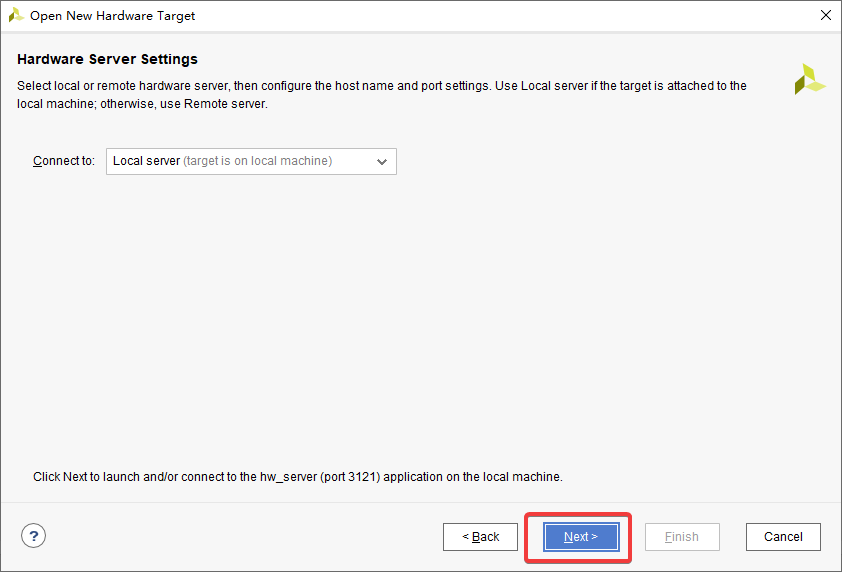

点Next

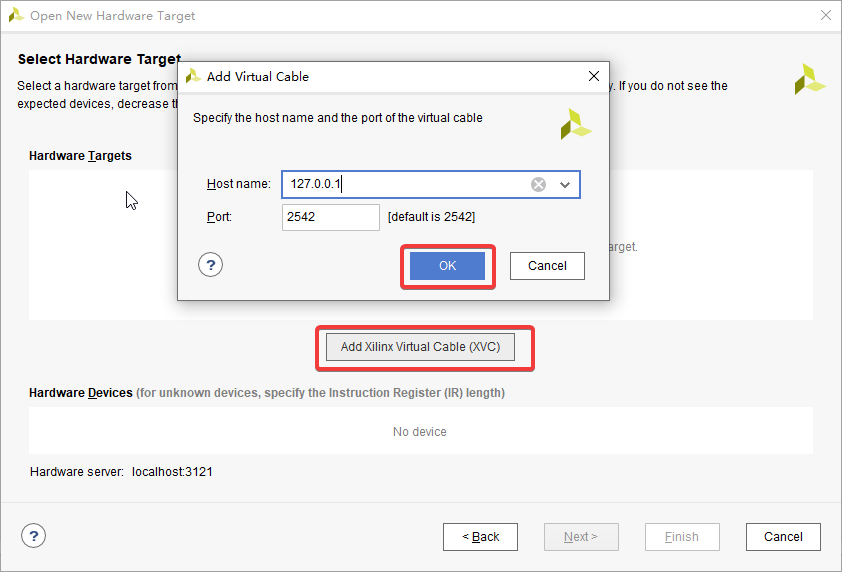

添加XVC虚拟线缆,并确认Host name:127.0.0.1 port:2542

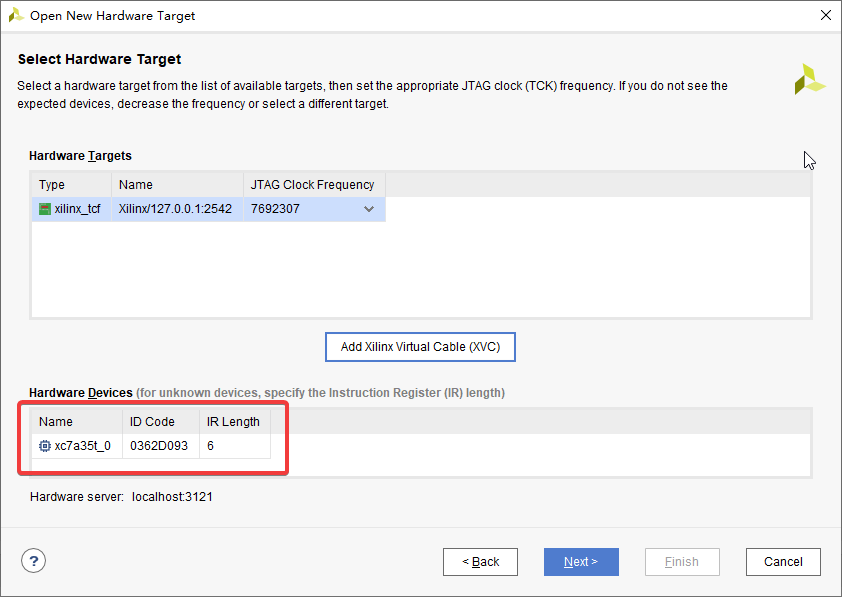

此时应能够看到FPGA的型号已经被扫描到。

点击Next、Finish。

4、程序下载

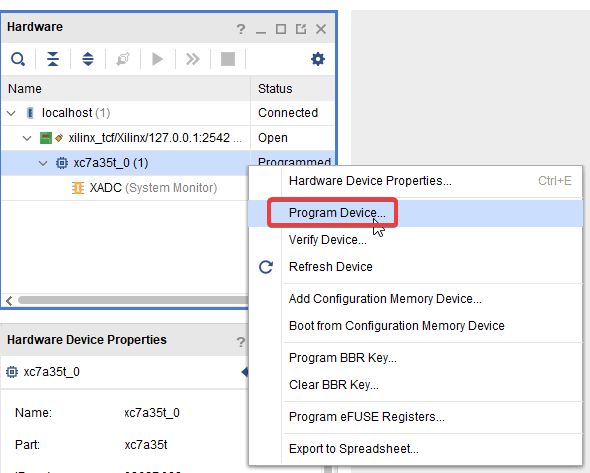

右键FPGA并选择Program Device。

在弹出的界面选择bit文件,点击Program并等待下载完成。

5、FPGA程序固化

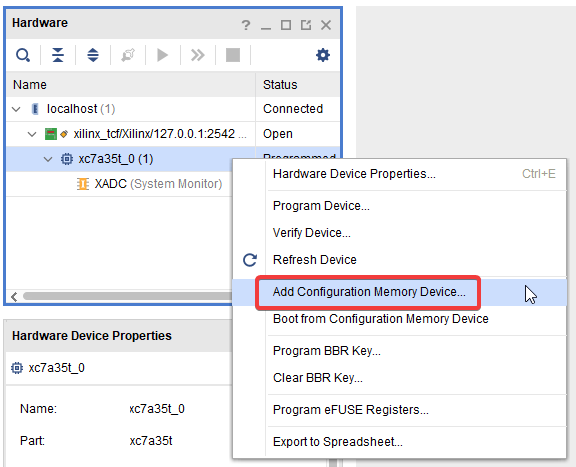

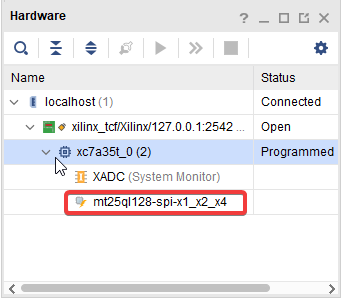

为FPGA选择自己的flash型号。

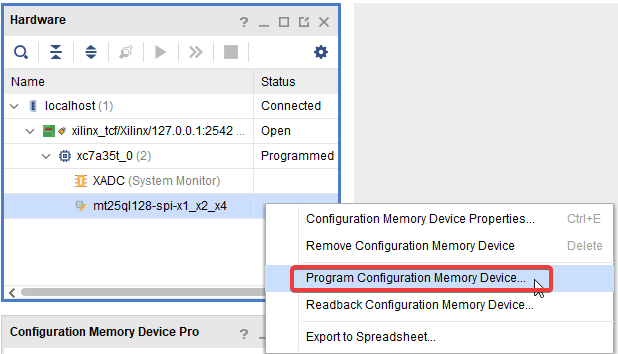

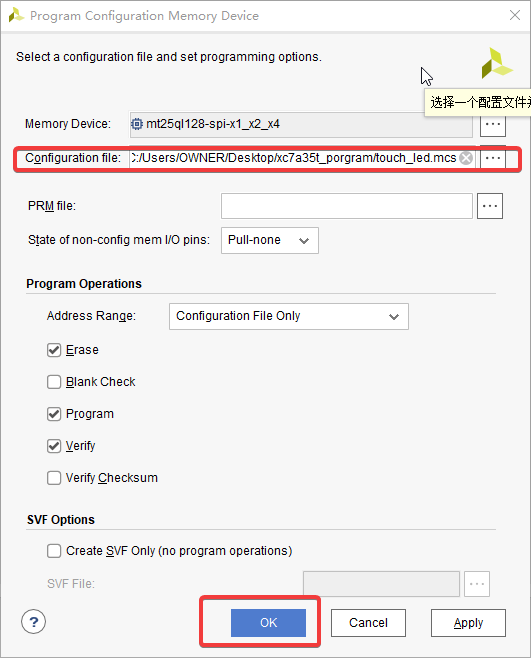

选择MCS文件并下载。

等待固化完成,并重启FPGA即可。