ARM Cortex-M0 MCU Design Learning | Part0

目录

1. 简介

1.1 Cortex-M0 DesignStart 组件包含:

1.2 Cortex-M0 DesignStart 组件目录结构:

2. 系统级结构

2.1 System-level Design Hierarchy

Item

Description

2.2 Cortex-M0 example system

Item

Description

3. 学习思路

项目资料地址:Cortex-M0_code

全部资料(补充):ARM_Learning_Materials

1. 简介

Cortex-M0 DesignStart 组件旨在用于基于 Cortex-M0 处理器的原型 SoC 的 SystemVerilog 设计与仿真。

1.1 Cortex-M0 DesignStart 组件包含:

-

An ARM Cortex-M0 processor from DesignStart.(处理器)

-

An example system-level design for the ARM Cortex-M0 processor.(样例系统)

-

Reusable AMBA components for system-level development.(AMBA 组件)

1.2 Cortex-M0 DesignStart 组件目录结构:

cortexm0ds|——cores/ <————Location for the processor files| |__cortexm0_designstart_r1p0/ <————Obfuscated Cortex-M0 RTL| |__logical/| |__cortexm0_dap/| |__cortexm0_integration/| |__cortexm0ds/| |__models/|——documentation/|——implementation_tsmc_ce018fg/| |__cortex_mO_mcu_system_synopsys/ <———Synthesis scripts for synthesizable parts of the example system|——logic/| |__cmsdk_xxx/| |__verilog/|——software/| |__cmsis/ <———CMSIS files, and header file for the example system and the example device driver code| ||__CMSIS/| ||__Device/| | |__ARM/| | |__CMSSDK_CM0/| |__common/ <—————Common software files| |__bootloader/| |__demos/| |__dhry/| |__retarget/| |__scripts/ <—————Linker scripts and other utility scripts| |__validation/|——systems/| |__cortex_m0_mcu/| |__rtl_sim/| ||__scripts/| ||__makefile| |__testcode/| ||__test_name/ <————————Software compilation setup files| |__verilog/ <————————Verilog and Verilog command files2. 系统级结构

2.1 System-level Design Hierarchy

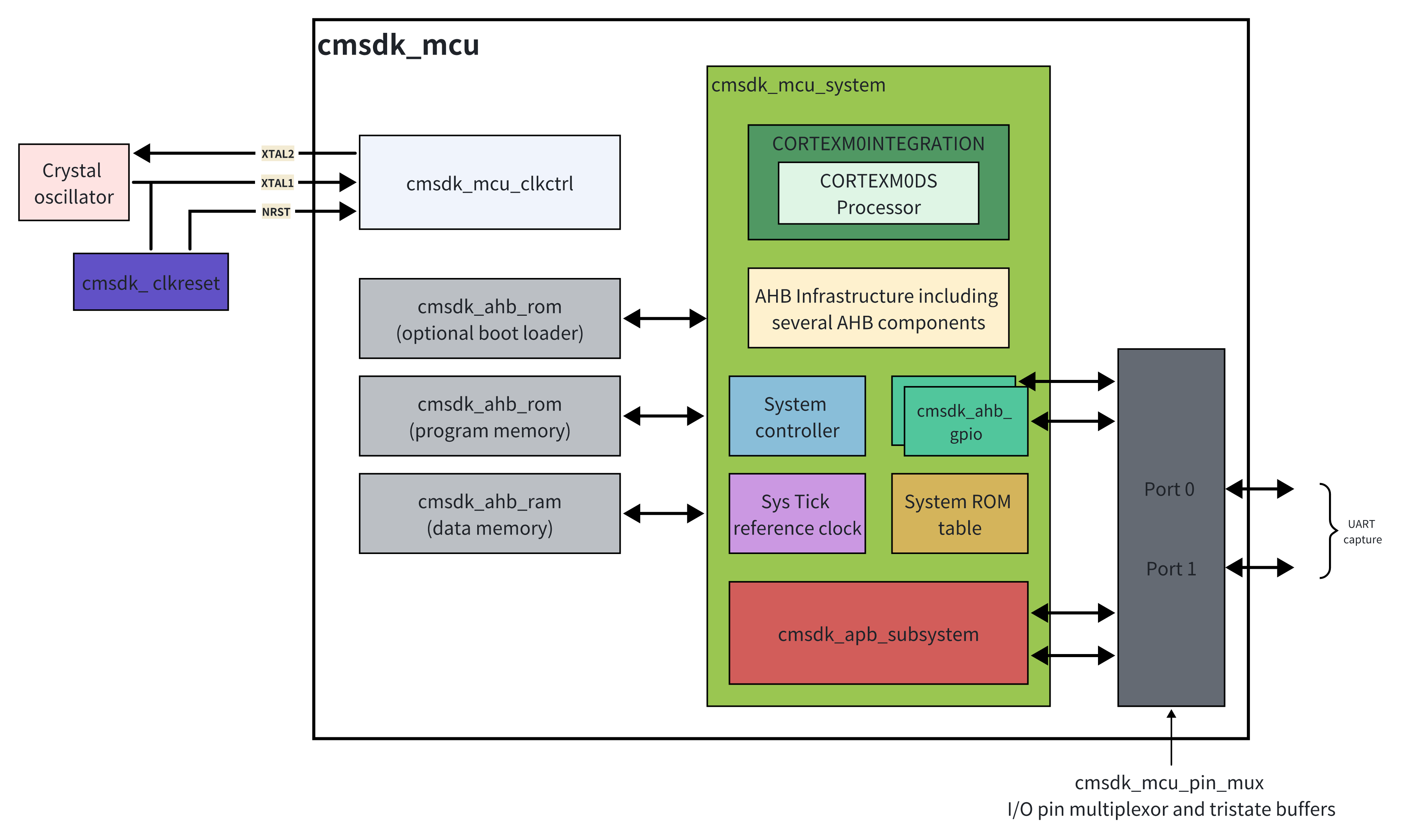

Figure1 给出了该 MCU 的顶层结构框图。Table1 给出了各模块的简要描述以便理解系统构成。

Item

Description

cmsdk_ahb_rom

A memory wrapper for the ROM to test the behavior of different implementations of memory. You can modify the Verilog parameters to change the implementation.

2.2 Cortex-M0 example system

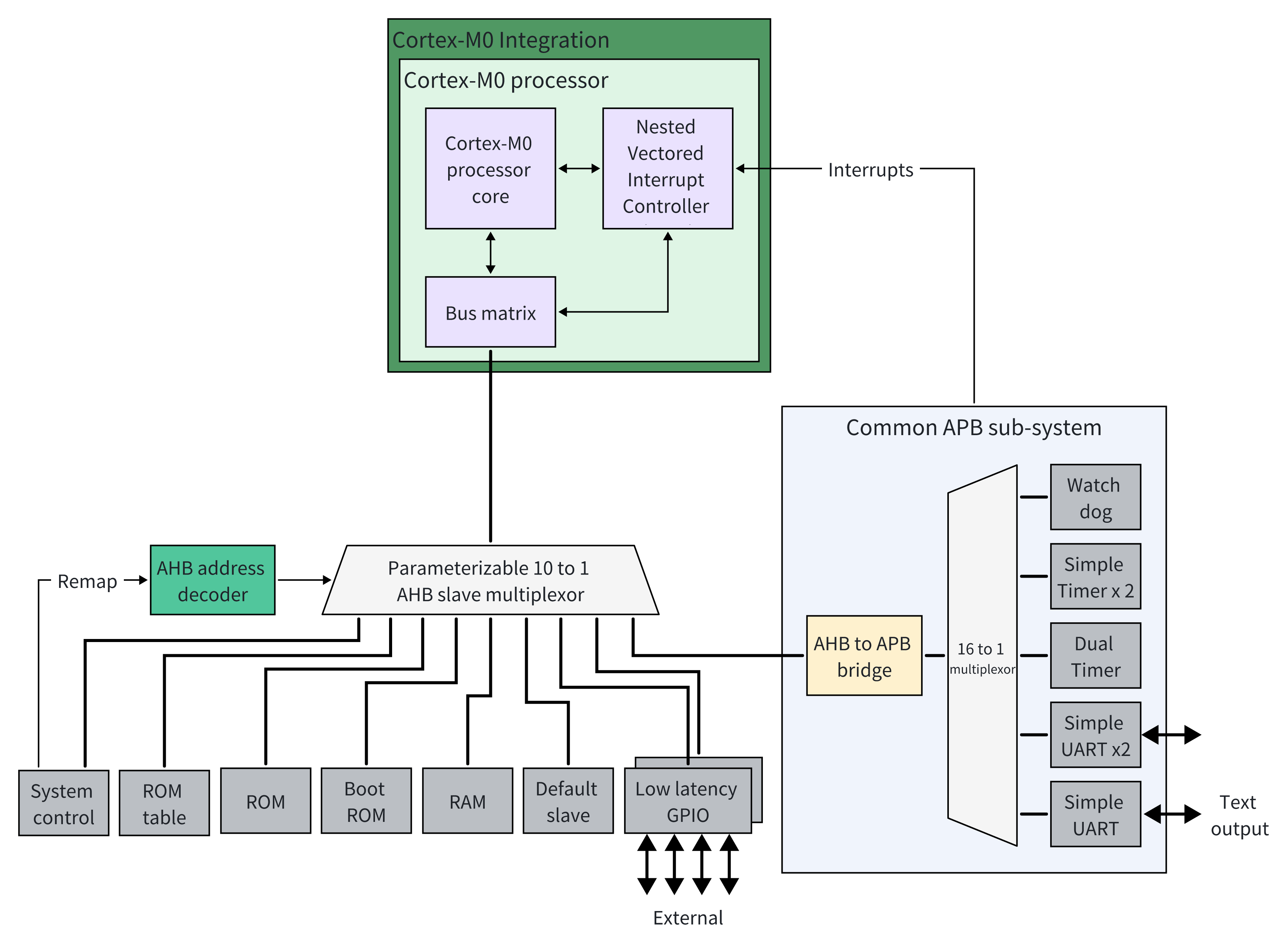

Figure 2 给出了基于 Cortex-M0 的一个系统例子。Table2 给出了组件的解释说明,便于理解。

用户可以通过多种不同的方式来配置系统。 该 Cortex-M0 处理器通过 AHB Lite 接口与系统的其他部分进行连接。

Item

Description

AHB slave (default)

3. 学习思路

首先从系统层面看,该 MCU 系统已经算是较为完整了,有 cpu 核,有各种外设(包含 AHB 和 APB Peripheral),呈现 CPU - AHB - APB 的结构,不尽人意的是没有更高速的 AXI 总线。应该是因为该处理器核是 AHB 的接口,所以是这样的结构。其实在实际芯片设计时,都是可以挂在 Subsys Noc 上的,所以学习价值还是有的;

其次,组件中除处理器核外还包含各类外设 IP,虽然是简单的行为级 IP,但对于 IP 的功能/行为逻辑的学习理解也是有价值的;

最后,后续将会以数字芯片设计的流程从 处理器核、外设IP、系统集成等方面展开学习总结,包含各 IP 和 系统级的 RTL 理解 ——> 编译 ——> 仿真验证 ——> Spyglass ——> DC。