| 偏移量 |

寄存器名称 |

位宽 |

访问方式 |

复位值 |

功能解读 |

4h |

Interrupt Event Register (EIR) |

32 |

RW |

0000_0000h |

中断事件的硬件状态映射寄存器,每一位对应特定中断源的触发标识。需通过软件读取并清零(写1清0),用于中断服务程序中快速定位触发源,优化中断响应效率。 |

8h |

Interrupt Mask Register (EIMR) |

32 |

RW |

0000_0000h |

中断使能掩码寄存器,与EIR位域一一对应。置位允许对应中断触发,清零屏蔽。在嵌入式系统初始化时需根据实际需求配置,避免无关中断占用CPU资源。 |

10h |

Receive Descriptor Active Register - Ring 0 (RDAR) |

32 |

RW |

0000_0000h |

管理接收描述符环0的激活状态,记录当前已分配但未完成处理的描述符数量。硬件通过此寄存器跟踪描述符使用情况,软件需配合更新以实现无锁化 descriptors 管理。 |

14h |

Transmit Descriptor Active Register - Ring 0 (TDAR) |

32 |

RW |

0000_0000h |

控制发送描述符环0的激活状态,标识待发送队列中有效描述符的数量。用于硬件调度发送任务,软件需在填充描述符后更新此值,触发发送引擎工作。 |

24h |

Ethernet Control Register (ECR) |

32 |

RW |

7000_0000h |

MAC核心控制寄存器,包含复位、使能、工作模式(全双工/半双工)等关键配置位。复位值7000_0000h通常对应默认硬件配置,初始化时需根据PHY协商结果重新配置。 |

40h |

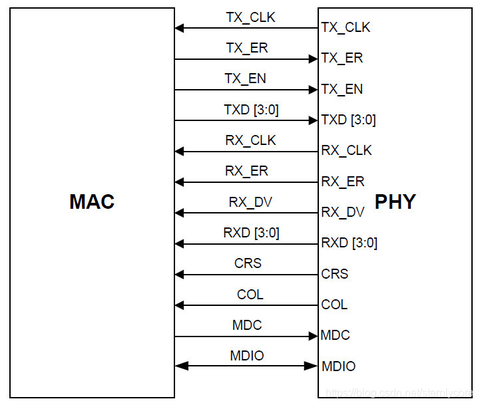

MII Management Frame Register (MMFR) |

32 |

RW |

0000_0000h |

MII总线管理接口的数据寄存器,用于PHY寄存器读写操作。需配合SMI时序,通过此寄存器传输PHY地址、寄存器地址及数据,实现链路状态配置与查询。 |

44h |

MII Speed Control Register (MSCR) |

32 |

RW |

0000_0000h |

配置MII接口的时钟频率及时序参数,支持10/100/1000Mbps速率适配。需根据PHY支持的速率等级配置,确保MAC与PHY之间的管理通信可靠。 |

64h |

MIB Control Register (MIBC) |

32 |

RW |

C000_0000h |

管理信息库(MIB)统计控制寄存器,用于使能/禁用各类流量统计计数器。复位值C000_0000h通常对应默认使能关键统计项,调试阶段可全开,量产时按需关闭以降低硬件开销。 |

84h |

Receive Control Register (RCR) |

32 |

RW |

05EE_0001h |

接收功能核心配置寄存器,包含过滤模式(单播/多播/广播)、帧长限制、校验使能等。复位值05EE_0001h对应默认接收配置,需根据应用场景(如是否需要接收所有帧)调整。 |

C4h |

Transmit Control Register (TCR) |

32 |

RW |

0000_0000h |

发送功能核心配置寄存器,控制发送使能、CRC生成、流量控制等。默认值0000_0000h为禁用状态,初始化时需置位使能位,并配置与接收端匹配的流量控制策略。 |

E4h |

Physical Address Lower Register (PALR) |

32 |

RW |

0000_0000h |

存储MAC物理地址的低32位(4字节),与PAUR共同构成6字节MAC地址。初始化时需写入唯一的硬件地址,用于接收帧的地址过滤,确保只接收目标为本机的帧。 |

E8h |

Physical Address Upper Register (PAUR) |

32 |

RW |

0000_8808h |

存储MAC物理地址的高16位(2字节),复位值0000_8808h为默认厂商地址片段,实际应用中需替换为分配的唯一地址。 |

ECh |

Opcode/Pause Duration Register (OPD) |

32 |

RW |

0001_0000h |

配置流量控制帧的操作码和暂停时长,用于全双工模式下的XON/XOFF帧生成。默认值0001_0000h对应标准暂停时长,需根据网络负载调整,避免过度暂停导致吞吐量下降。 |

F0h - F8h |

Transmit Interrupt Coalescing Register (TXIC0 - TXIC2) |

32 |

RW |

0000_0000h |

发送中断聚合配置寄存器,控制中断触发的帧计数阈值和时间阈值。通过设置合理的聚合参数(如累计N帧或超时T后触发一次中断),减少CPU中断响应次数,提升系统性能。 |

100h - 108h |

Receive Interrupt Coalescing Register (RXIC0 - RXIC2) |

32 |

RW |

0000_0000h |

接收中断聚合配置寄存器,功能类似TXIC,针对接收路径优化。在高流量场景下,适当增大聚合阈值可显著降低中断开销,但会增加接收延迟,需权衡配置。 |

118h |

Descriptor Individual Upper Address Register (IAUR) |

32 |

RW |

0000_0000h |

独立描述符的高32位地址寄存器,用于指定单个特殊描述符的内存位置。通常用于异常帧处理或优先级队列,需与IALR配合使用,指向连续的内存空间。 |

11Ch |

Descriptor Individual Lower Address Register (IALR) |

32 |

RW |

0000_0000h |

独立描述符的低32位地址寄存器,与IAUR组成32位或64位地址(取决于CPU架构),指向描述符在内存中的物理地址(需考虑MMU映射)。 |

120h |

Descriptor Group Upper Address Register (GAUR) |

32 |

RW |

0000_0000h |

描述符组的高32位起始地址,用于指定描述符环的基地址高位。描述符环需分配在连续物理内存中,且按缓存行对齐,以提高DMA访问效率。 |

124h |

Descriptor Group Lower Address Register (GALR) |

32 |

RW |

0000_0000h |

描述符组的低32位起始地址,与GAUR共同定义描述符环的基地址。初始化时需确保地址对齐正确,避免DMA访问未对齐地址导致的性能损失或错误。 |

144h |

Transmit FIFO Watermark Register (TFWR) |

32 |

RW |

0000_0000h |

设置发送FIFO的水印阈值,当FIFO中数据量低于此值时触发DMA请求,补充发送数据。需根据发送速率和CPU处理能力配置,避免FIFO空导致的发送中断。 |

160h |

Receive Descriptor Ring 1 Start Register (RDSR1) |

32 |

RW |

0000_0000h |

接收描述符环1的起始地址寄存器,用于多队列接收场景,实现不同类型帧的分类处理(如优先级队列)。需与RDSR0、RDSR2配合,分配独立的内存区域。 |

164h |

Transmit Buffer Descriptor Ring 1 Start Register (TDSR1) |

32 |

RW |

0000_0000h |

发送描述符环1的起始地址寄存器,支持多队列发送,可用于QoS(服务质量)实现,按优先级调度不同队列的帧发送。 |

168h |

Maximum Receive Buffer Size Register - Ring 1 (MRBR1) |

32 |

RW |

0000_0000h |

限制接收描述符环1的最大缓冲区大小,防止超大帧占用过多内存。需根据应用中预期接收的最大帧长配置,通常不超过MTU(如1500字节)。 |

16Ch |

Receive Descriptor Ring 2 Start Register (RDSR2) |

32 |

RW |

0000_0000h |

接收描述符环2的起始地址寄存器,功能同RDSR1,用于扩展多队列接收能力,适应复杂场景下的帧分类需求。 |

170h |

Transmit Buffer Descriptor Ring 2 Start Register (TDSR2) |

32 |

RW |

0000_0000h |

发送描述符环2的起始地址寄存器,扩展多队列发送能力,支持更精细的QoS控制。 |

174h |

Maximum Receive Buffer Size Register - Ring 2 (MRBR2) |

32 |

RW |

0000_0000h |

接收描述符环2的最大缓冲区大小限制,配置原则同MRBR1,根据环2处理的帧类型设置合适值。 |

180h |

Receive Descriptor Ring 0 Start Register (RDSR) |

32 |

RW |

0000_0000h |

接收描述符环0的起始地址寄存器,默认接收队列,通常用于处理常规流量,需优先配置以保证基本通信功能。 |

184h |

Transmit Buffer Descriptor Ring 0 Start Register (TDSR) |

32 |

RW |

0000_0000h |

发送描述符环0的起始地址寄存器,默认发送队列,用于常规数据发送,初始化时需首先配置此寄存器。 |

188h |

Maximum Receive Buffer Size Register - Ring 0 (MRBR) |

32 |

RW |

0000_0000h |

接收描述符环0的最大缓冲区大小,通常设置为MTU值 |

190h |

Receive FIFO Section Full Threshold (RSFL) |

32 |

RW |

0000_0000h |

接收FIFO分区满阈值,当对应分区数据量达到阈值时触发状态指示。用于FIFO分区管理,实现精细化的流量控制。 |

194h |

Receive FIFO Section Empty Threshold (RSEM) |

32 |

RW |

0000_0000h |

接收FIFO分区空阈值,当对应分区数据量低于阈值时触发状态指示,用于触发数据读取操作。 |

198h |

Receive FIFO Almost Empty Threshold (RAEM) |

32 |

RW |

0000_0004h |

接收FIFO近空阈值,默认值4字节,用于提前预警FIFO数据量过低,便于CPU及时准备接收新数据。 |

19Ch |

Receive FIFO Almost Full Threshold (RAFL) |

32 |

RW |

0000_0004h |

接收FIFO近满阈值,默认值4字节,用于提前预警FIFO数据量过高,触发CPU及时读取数据,避免FIFO溢出。 |

1A0h |

Transmit FIFO Section Empty Threshold (TSEM) |

32 |

RW |

0000_0000h |

发送FIFO分区空阈值,当对应分区数据量低于阈值时触发状态指示,用于触发数据填充操作。 |

1A4h |

Transmit FIFO Almost Empty Threshold (TAEM) |

32 |

RW |

0000_0004h |

发送FIFO近空阈值,默认值4字节,用于提前预警发送数据不足,触发CPU及时填充数据,避免发送中断。 |

1A8h |

Transmit FIFO Almost Full Threshold (TAFL) |

32 |

RW |

0000_0008h |

发送FIFO近满阈值寄存器,默认8字节。当数据量达到此值时触发状态指示,用于限制FIFO填充深度,预留缓冲空间应对突发流量,防止FIFO溢出导致的数据丢失。 |

1ACh |

Transmit Inter-Packet Gap (TIPG) |

32 |

RW |

0000_000Ch |

发送帧间隔寄存器,默认12字节。配置以太网帧之间的最小发送间隔,需符合IEEE 802.3标准(100Mbps对应96bit时间),确保接收方有足够处理时间,避免帧冲突。 |

1B0h |

Frame Truncation Length (FTRL) |

32 |

RW |

0000_07FFh |

帧截断长度寄存器,默认2047字节。超过此值的发送帧将被截断,适用于特殊场景下的帧大小限制,需注意截断可能导致接收方CRC校验失败。 |

1C0h |

Transmit Accelerator Function Configuration (TACC) |

32 |

RW |

0000_0000h |

发送加速器配置寄存器,控制硬件加速功能(如校验和生成、TCP分段)。默认禁用,高吞吐量场景下开启可显著降低CPU负载,但需确保与协议栈适配。 |

1C4h |

Receive Accelerator Function Configuration (RACC) |

32 |

RW |

0000_0000h |

接收加速器配置寄存器,控制接收硬件加速(如校验和验证、VLAN剥离)。默认禁用,开启后由硬件完成部分协议处理,减少中断响应时间,提升接收性能。 |

1C8h - 1CCh |

Receive Classification Match Register for Class n (RCMR1 - RCMR2) |

32 |

RW |

0000_0000h |

接收分类匹配寄存器,定义多队列接收的帧分类规则(如MAC地址、IP优先级)。通过掩码与模式匹配,实现帧到不同接收队列的定向分发,支持精细化流量管理。 |

1D8h - 1DCh |

DMA Class Based Configuration (DMA1CFG - DMA2CFG) |

32 |

RW |

0000_0000h |

DMA分类配置寄存器,为不同流量类别配置独立DMA参数(优先级、缓存策略)。支持基于业务的DMA资源调度,确保高优先级流量的传输时延,适用于QoS场景。 |

1E0h |

Receive Descriptor Active Register - Ring 1 (RDAR1) |

32 |

RW |

0000_0000h |

接收描述符环1激活寄存器,管理环1中已分配未处理的描述符数量。与RDAR(环0)功能一致,用于多队列接收的独立管理,需确保与软件描述符管理逻辑同步。 |

1E4h |

Transmit Descriptor Active Register - Ring 1 (TDAR1) |

32 |

RW |

0000_0000h |

发送描述符环1激活寄存器,标识环1中待发送的有效描述符数量。硬件发送完成后自动递减,软件填充后需更新此值触发发送,实现多队列发送的并行调度。 |

1E8h |

Receive Descriptor Active Register - Ring 2 (RDAR2) |

32 |

RW |

0000_0000h |

接收描述符环2激活寄存器,扩展多队列接收能力,适用于三队列以上的复杂流量分类场景,配置原则同RDAR1。 |

1ECh |

Transmit Descriptor Active Register - Ring 2 (TDAR2) |

32 |

RW |

0000_0000h |

发送描述符环2激活寄存器,扩展多队列发送能力,支持更精细的QoS分级,需与调度算法配合实现优先级抢占。 |

1F0h |

QOS Scheme (QOS) |

32 |

RW |

0000_0000h |

服务质量策略寄存器,配置优先级映射规则(如DSCP到硬件队列)。支持802.1p等优先级机制,确保关键业务的传输质量,需与网络拓扑中的QoS策略一致。 |

204h |

Tx Packet Count Statistic Register (RMON_T_PACKETS) |

32 |

R |

0000_0000h |

发送数据包计数寄存器(RMON标准),累计发送的总帧数(含错误帧)。只读,需软件定期读取清零,用于网络流量监控与带宽计算,支持SNMP等管理协议。 |

208h |

Tx Broadcast Packets Statistic Register (RMON_T_BC_PKT) |

32 |

R |

0000_0000h |

发送广播帧计数寄存器,累计发送的广播帧数。异常增长可能导致广播风暴,需在管理软件中设置阈值告警,避免网络拥塞。 |

20Ch |

Tx Multicast Packets Statistic Register (RMON_T_MC_PKT) |

32 |

R |

0000_0000h |

发送多播帧计数寄存器,累计发送的多播帧数。用于评估多播业务的流量占比,优化组播路由配置。 |

210h |

Tx Packets with CRC/Align Error Statistic Register (RMON_T_CRC_ALIGN) |

32 |

R |

0000_0000h |

发送CRC/对齐错误帧计数寄存器,累计发送时出现CRC错误或帧对齐错误的帧数。非零值通常指示硬件故障(如PHY连接问题),需及时诊断。 |

214h |

Tx Packets Less Than 64 Bytes and Good CRC Statistic Register (RMON_T_UNDERSIZE) |

32 |

R |

0000_0000h |

发送小于64字节且CRC正确帧计数寄存器,累计短有效帧。过多短帧可能影响传输效率,需检查应用层是否存在不合理的小数据包发送。 |

218h |

Tx Packets GT MAX_FL bytes and Good CRC Statistic Register (RMON_T_OVERSIZE) |

32 |

R |

0000_0000h |

发送超长有效帧计数寄存器,累计超过最大帧长(MAX_FL)且CRC正确的帧。通常对应巨型帧(Jumbo Frame),需确保接收端支持,否则会被丢弃。 |

21Ch |

Tx Packets Less Than 64 Bytes and Bad CRC Statistic Register (RMON_T_FRAG) |

32 |

R |

0000_0000h |

发送小于64字节且CRC错误帧计数寄存器,累计短错误帧(碰撞碎片)。半双工模式下常见,过多则指示信道竞争激烈,需考虑升级为全双工。 |

220h |

Tx Packets Greater Than MAX_FL bytes and Bad CRC Statistic Register (RMON_T_JAB) |

32 |

R |

0000_0000h |

发送超长错误帧计数寄存器,累计超过MAX_FL且CRC错误的帧(Jabber帧)。通常由硬件故障导致,需检查PHY与MAC的时钟同步。 |

224h |

Tx Collision Count Statistic Register (RMON_T_COL) |

32 |

R |

0000_0000h |

发送碰撞计数寄存器,累计发送过程中的碰撞次数。仅半双工模式有效,碰撞率过高(如超过5%)需优化网络拓扑。 |

228h |

Tx 64-Byte Packets Statistic Register (RMON_T_P64) |

32 |

R |

0000_0000h |

发送64字节帧计数寄存器,按帧长分布统计流量特征。用于分析应用层数据包大小分布,优化MTU配置。 |

22Ch |

Tx 65- to 127-byte Packets Statistic Register (RMON_T_P65TO127) |

32 |

R |

0000_0000h |

发送65-127字节帧计数寄存器,属于帧长分布统计的一部分,用于网络流量模型分析。 |

230h |

Tx 128- to 255-byte Packets Statistic Register (RMON_T_P128TO255) |

32 |

R |

0000_0000h |

发送128-255字节帧计数寄存器,帧长分布统计,帮助评估网络承载的业务类型(如控制报文、数据报文)。 |

234h |

Tx 256- to 511-byte Packets Statistic Register (RMON_T_P256TO511) |

32 |

R |

0000_0000h |

发送256-511字节帧计数寄存器,帧长分布统计,用于流量特征分析与带宽规划。 |

238h |

Tx 512- to 1023-byte Packets Statistic Register (RMON_T_P512TO1023) |

32 |

R |

0000_0000h |

发送512-1023字节帧计数寄存器,帧长分布统计,反映中等大小数据包的占比。 |

23Ch |

Tx 1024- to 2047-byte Packets Statistic Register (RMON_T_P1024TO2047) |

32 |

R |

0000_0000h |

发送1024-2047字节帧计数寄存器,帧长分布统计,常用于评估大数据包传输比例。 |

240h |

Tx Packets Greater Than 2048 Bytes Statistic Register (RMON_T_P_GTE2048) |

32 |

R |

0000_0000h |

发送大于2048字节帧计数寄存器,累计巨型帧发送量。需确保整个网络路径支持巨型帧,否则会导致分片或丢弃。 |

244h |

Tx Octets Statistic Register (RMON_T_OCTETS) |

32 |

R |

0000_0000h |

发送字节计数寄存器,累计发送的总字节数(含帧头)。用于计算发送带宽利用率(字节数/时间),评估网络负载。 |

24Ch |

Frames Transmitted OK Statistic Register (IEEE_T_FRAME_OK) |

32 |

R |

0000_0000h |

发送成功帧计数寄存器(IEEE标准),累计所有成功发送的有效帧(不含错误帧)。用于评估发送链路的有效性和数据传输成功率。 |

250h |

Frames Transmitted with Single Collision Statistic Register (IEEE_T_1COL) |

32 |

R |

0000_0000h |

单次碰撞后发送成功帧计数寄存器,累计经历一次碰撞后成功发送的帧数。反映半双工模式下信道竞争程度,数值过高表明网络负载较重。 |

254h |

Frames Transmitted with Multiple Collisions Statistic Register (IEEE_T_MCOL) |

32 |

R |

0000_0000h |

多次碰撞后发送成功帧计数寄存器,累计经历多次碰撞后成功发送的帧数。该值与总发送帧数的比例可用于评估网络冲突严重性。 |

258h |

Frames Transmitted after Deferral Delay Statistic Register (IEEE_T_DEF) |

32 |

R |

0000_0000h |

延迟发送帧计数寄存器,累计因检测到信道忙而延迟发送的帧数。半双工模式下正常存在,比例过高表明网络拥堵。 |

25Ch |

Frames Transmitted with Late Collision Statistic Register (IEEE_T_LCOL) |

32 |

R |

0000_0000h |

晚期碰撞帧计数寄存器,累计发送过程中发生晚期碰撞(超过64字节后)的帧数。通常因线缆过长或硬件故障导致,需检查物理层连接。 |

260h |

Frames Transmitted with Excessive Collisions Statistic Register (IEEE_T_EXCOL) |

32 |

R |

0000_0000h |

过多碰撞丢弃帧计数寄存器,累计因碰撞次数超过16次上限而丢弃的帧数。表明网络严重拥堵或存在故障,需优化网络拓扑。 |

264h |

Frames Transmitted with Tx FIFO Underrun Statistic Register (IEEE_T_MACERR) |

32 |

R |

0000_0000h |

发送FIFO下溢错误帧计数寄存器,累计因FIFO数据不足导致发送失败的帧数。需调整TAEM阈值或优化CPU填充速度,避免传输中断。 |

268h |

Frames Transmitted with Carrier Sense Error Statistic Register (IEEE_T_CSERR) |

32 |

R |

0000_0000h |

载波检测错误帧计数寄存器,累计发送时载波检测异常的帧数。通常指示PHY故障或链路质量问题,需进行硬件诊断。 |

26Ch |

Reserved Statistic Register (IEEE_T_SQE) |

32 |

R |

0000_0000h |

预留统计寄存器,原用于SQE(信号质量错误)测试,现代以太网控制器中通常未使用,值恒为0。 |

270h |

Flow Control Pause Frames Transmitted Statistic Register (IEEE_T_FDXFC) |

32 |

R |

0000_0000h |

发送流量控制暂停帧计数寄存器,累计发送的802.3x PAUSE帧数量。用于评估流量控制机制的活跃度,反映接收端的负载状态。 |

274h |

Octet Count for Frames Transmitted w/o Error Statistic Register (IEEE_T_OCTETS_OK) |

32 |

R |

0000_0000h |

发送无错字节计数寄存器,累计成功发送的有效字节数(不含错误帧)。用于计算实际有效带宽利用率,评估传输效率。 |

284h |

Rx Packet Count Statistic Register (RMON_R_PACKETS) |

32 |

R |

0000_0000h |

接收数据包计数寄存器(RMON标准),累计接收的总帧数(含错误帧)。只读,需定期读取清零,用于接收流量监控与带宽计算。 |

288h |

Rx Broadcast Packets Statistic Register (RMON_R_BC_PKT) |

32 |

R |

0000_0000h |

接收广播帧计数寄存器,累计接收的广播帧数。异常增长可能预示广播风暴,需配置适当的广播过滤策略。 |

28Ch |

Rx Multicast Packets Statistic Register (RMON_R_MC_PKT) |

32 |

R |

0000_0000h |

接收多播帧计数寄存器,累计接收的多播帧数。用于评估多播组加入情况和组播流量占比,优化组播过滤配置。 |

290h |

Rx Packets with CRC/Align Error Statistic Register (RMON_R_CRC_ALIGN) |

32 |

R |

0000_0000h |

接收CRC/对齐错误帧计数寄存器,累计接收时出现CRC错误或帧对齐错误的帧数。高数值表明链路质量差或存在物理层故障。 |

294h |

Rx Packets with Less Than 64 Bytes and Good CRC Statistic Register (RMON_R_UNDERSIZE) |

32 |

R |

0000_0000h |

接收小于64字节且CRC正确帧计数寄存器,累计短有效帧。过多可能表明存在异常流量或配置错误(如MTU设置过小)。 |

298h |

Rx Packets Greater Than MAX_FL and Good CRC Statistic Register (RMON_R_OVERSIZE) |

32 |

R |

0000_0000h |

接收超长有效帧计数寄存器,累计超过最大帧长且CRC正确的帧。需确认本地控制器是否启用巨型帧支持,否则会被丢弃。 |

29Ch |

Rx Packets Less Than 64 Bytes and Bad CRC Statistic Register (RMON_R_FRAG) |

32 |

R |

0000_0000h |

接收小于64字节且CRC错误帧计数寄存器,累计短错误帧(碰撞碎片)。主要来自半双工网络,反映网络冲突情况。 |

2A0h |

Rx Packets Greater Than MAX_FL Bytes and Bad CRC Statistic Register (RMON_R_JAB) |

32 |

R |

0000_0000h |

接收超长错误帧计数寄存器,累计超过最大帧长且CRC错误的帧(Jabber帧)。通常由故障设备发送,需定位并排除故障节点。 |

2A8h |

Rx 64-Byte Packets Statistic Register (RMON_R_P64) |

32 |

R |

0000_0000h |

接收64字节帧计数寄存器,按帧长分布统计接收流量特征。用于分析应用层数据包大小模式,优化接收缓冲区配置。 |

2ACh |

Rx 65- to 127-Byte Packets Statistic Register (RMON_R_P65TO127) |

32 |

R |

0000_0000h |

接收65-127字节帧计数寄存器,帧长分布统计的一部分,帮助分析网络中控制报文与数据报文的比例。 |

2B0h |

Rx 128- to 255-Byte Packets Statistic Register (RMON_R_P128TO255) |

32 |

R |

0000_0000h |

接收128-255字节帧计数寄存器,反映中等偏小数据包的接收比例,用于优化接收FIFO和缓冲区大小。 |

2B4h |

Rx 256- to 511-Byte Packets Statistic Register (RMON_R_P256TO511) |

32 |

R |

0000_0000h |

接收256-511字节帧计数寄存器,帧长分布统计,用于评估中等大小数据的传输需求。 |

2B8h |

Rx 512- to 1023-Byte Packets Statistic Register (RMON_R_P512TO1023) |

32 |

R |

0000_0000h |

接收512-1023字节帧计数寄存器,反映中等大小数据包的接收占比,用于缓冲区资源分配优化。 |

2BCh |

Rx 1024- to 2047-Byte Packets Statistic Register (RMON_R_P1024TO2047) |

32 |

R |

0000_0000h |

接收1024-2047字节帧计数寄存器,累计较大数据包的接收量,用于评估大数据传输需求。 |

2C0h |

Rx Packets Greater than 2048 Bytes Statistic Register (RMON_R_P_GTE2048) |

32 |

R |

0000_0000h |

接收大于2048字节帧计数寄存器,累计接收的巨型帧数量。需确保本地MAC已启用巨型帧支持,否则这些帧会被丢弃。 |

2C4h |

Rx Octets Statistic Register (RMON_R_OCTETS) |

32 |

R |

0000_0000h |

接收字节计数寄存器,累计接收的总字节数(含帧头和错误帧)。用于计算接收带宽利用率,评估网络接收负载。 |

2C8h |

Frames not Counted Correctly Statistic Register (IEEE_R_DROP) |

32 |

R |

0000_0000h |

计数错误丢弃帧寄存器,累计因内部错误未被正确计数的帧数。非零值通常指示硬件故障或严重的资源竞争,需诊断。 |

2CCh |

Frames Received OK Statistic Register (IEEE_R_FRAME_OK) |

32 |

R |

0000_0000h |

接收成功帧计数寄存器(IEEE标准),累计所有正确接收的有效帧。用于评估接收链路的有效性和数据接收成功率。 |

2D0h |

Frames Received with CRC Error Statistic Register (IEEE_R_CRC) |

32 |

R |

0000_0000h |

接收CRC错误帧计数寄存器,累计CRC校验失败的接收帧。高数值表明链路质量差、存在干扰或物理层故障。 |

2D4h |

Frames Received with Alignment Error Statistic Register (IEEE_R_ALIGN) |

32 |

R |

0000_0000h |

接收对齐错误帧计数寄存器,累计帧长度不是整数个字节的错误帧。通常由物理层同步问题或干扰导致。 |

2D8h |

Receive FIFO Overflow Count Statistic Register (IEEE_R_MACERR) |

32 |

R |

0000_0000h |

接收FIFO溢出计数寄存器,累计因FIFO满导致丢失的帧数。需调整接收FIFO阈值或优化CPU/DMA读取速度,避免数据丢失。 |

2DCh |

Flow Control Pause Frames Received Statistic Register (IEEE_R_FDXFC) |

32 |

R |

0000_0000h |

接收流量控制暂停帧计数寄存器,累计接收的802.3x PAUSE帧数量。用于评估远程节点的流量控制需求,反映网络负载状况。 |

2E0h |

Octet Count for Frames Received without Error Statistic Register (IEEE_R_OCTETS_OK) |

32 |

R |

0000_0000h |

接收无错字节计数寄存器,累计成功接收的有效字节数(不含错误帧)。用于计算实际有效接收带宽,评估接收链路效率。 |

400h |

Adjustable Timer Control Register (ATCR) |

32 |

RW |

0000_0000h |

可调定时器控制寄存器,配置定时器的工作模式(自由运行/周期性)、中断使能等。默认禁用状态,需根据时间戳或定时需求配置。 |

404h |

Timer Value Register (ATVR) |

32 |

RW |

0000_0000h |

定时器当前值寄存器,可读可写。读取返回当前计数值,写入可直接设置定时器值,用于同步或校准操作。 |

408h |

Timer Offset Register (ATOFF) |

32 |

RW |

0000_0000h |

定时器偏移寄存器,用于设置时间戳的偏移量。可用于网络时钟同步,校准本地时间与网络时间的偏差。 |

40Ch |

Timer Period Register (ATPER) |

32 |

RW |

3B9A_CA00h |

定时器周期寄存器,默认值对应1秒(3B9ACA00h = 1,000,000,000)。配置周期性定时器的溢出周期,用于产生固定间隔的定时中断。 |

410h |

Timer Correction Register (ATCOR) |

32 |

RW |

0000_0000h |

定时器校正寄存器,用于微调定时器频率。可补偿硬件时钟偏差,提高时间戳精度,适用于精确时间同步场景。 |

414h |

Time-Stamping Clock Period Register (ATINC) |

32 |

RW |

0000_0000h |

时间戳时钟周期寄存器,配置时间戳计数器的增量值。根据系统时钟频率设置,确保时间戳单位准确(通常为纳秒)。 |

418h |

Timestamp of Last Transmitted Frame (ATSTMP) |

32 |

R |

0000_0000h |

最后发送帧时间戳寄存器,记录最近一次帧发送完成的时间戳。用于计算传输时延、RTT等网络性能指标。 |

604h |

Timer Global Status Register (TGSR) |

32 |

RW |

0000_0000h |

定时器全局状态寄存器,汇总所有定时器的状态标志(如溢出、比较匹配)。支持全局中断状态查询与清除,简化中断处理逻辑。 |

608h |

Timer Control Status Register (TCSR0) |

32 |

RW |

0000_0000h |

定时器0控制状态寄存器,配置定时器0的工作模式、中断使能,并反映其当前状态。独立控制第一路定时器资源。 |

60Ch |

Timer Compare Capture Register (TCCR0) |

32 |

RW |

0000_0000h |

定时器0比较捕获寄存器,设置比较匹配值或捕获当前计数值。用于产生精确的时间间隔中断或记录外部事件发生时间。 |

610h |

Timer Control Status Register (TCSR1) |

32 |

RW |

0000_0000h |

定时器1控制状态寄存器,功能同TCSR0,独立控制第二路定时器资源,可实现与定时器0不同的定时需求。 |

614h |

Timer Compare Capture Register (TCCR1) |

32 |

RW |

0000_0000h |

定时器1比较捕获寄存器,功能同TCCR0,与TCSR1配合使用,实现第二路定时器的比较或捕获功能。 |

618h |

Timer Control Status Register (TCSR2) |

32 |

RW |

0000_0000h |

定时器2控制状态寄存器,第三路独立定时器的控制接口,可用于实现多种定时功能的并行处理。 |

61Ch |

Timer Compare Capture Register (TCCR2) |

32 |

RW |

0000_0000h |

定时器2比较捕获寄存器,与TCSR2配合,提供第三路定时器的比较匹配或事件捕获能力。 |

620h |

Timer Control Status Register (TCSR3) |

32 |

RW |

0000_0000h |

定时器3控制状态寄存器,第四路独立定时器的控制接口,满足复杂系统中多任务定时需求。 |

624h |

Timer Compare Capture Register (TCCR3) |

32 |

RW |

0000_0000h |

定时器3比较捕获寄存器,与TCSR3配合,提供第四路定时器的比较匹配或事件捕获功能。 |