FPGA开发之封装一个属于自己的高级私人IP(一)_fpga自定义封装ip

如何封装一个属于自己的高级私人IP?作者手把手教你如何封装一个属于自己的个性化IP。

关于封装自己的个性化IP,这里作者将会分为两篇来详细讲述一下!

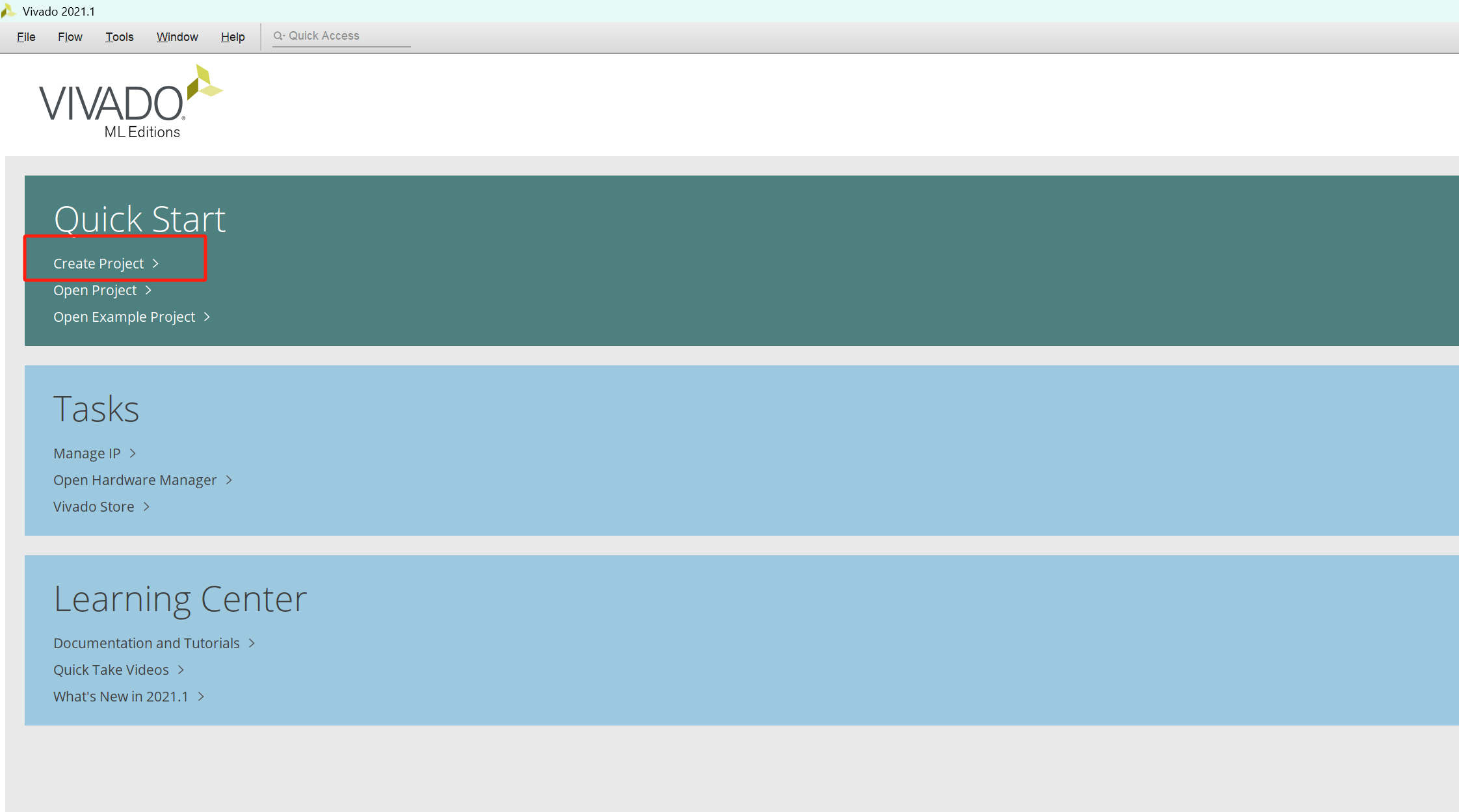

话不多说,直接上步骤,这里采用的是vivado2021.1版本,

创建工程

一.首先,我们需要创建一个单独的工程。

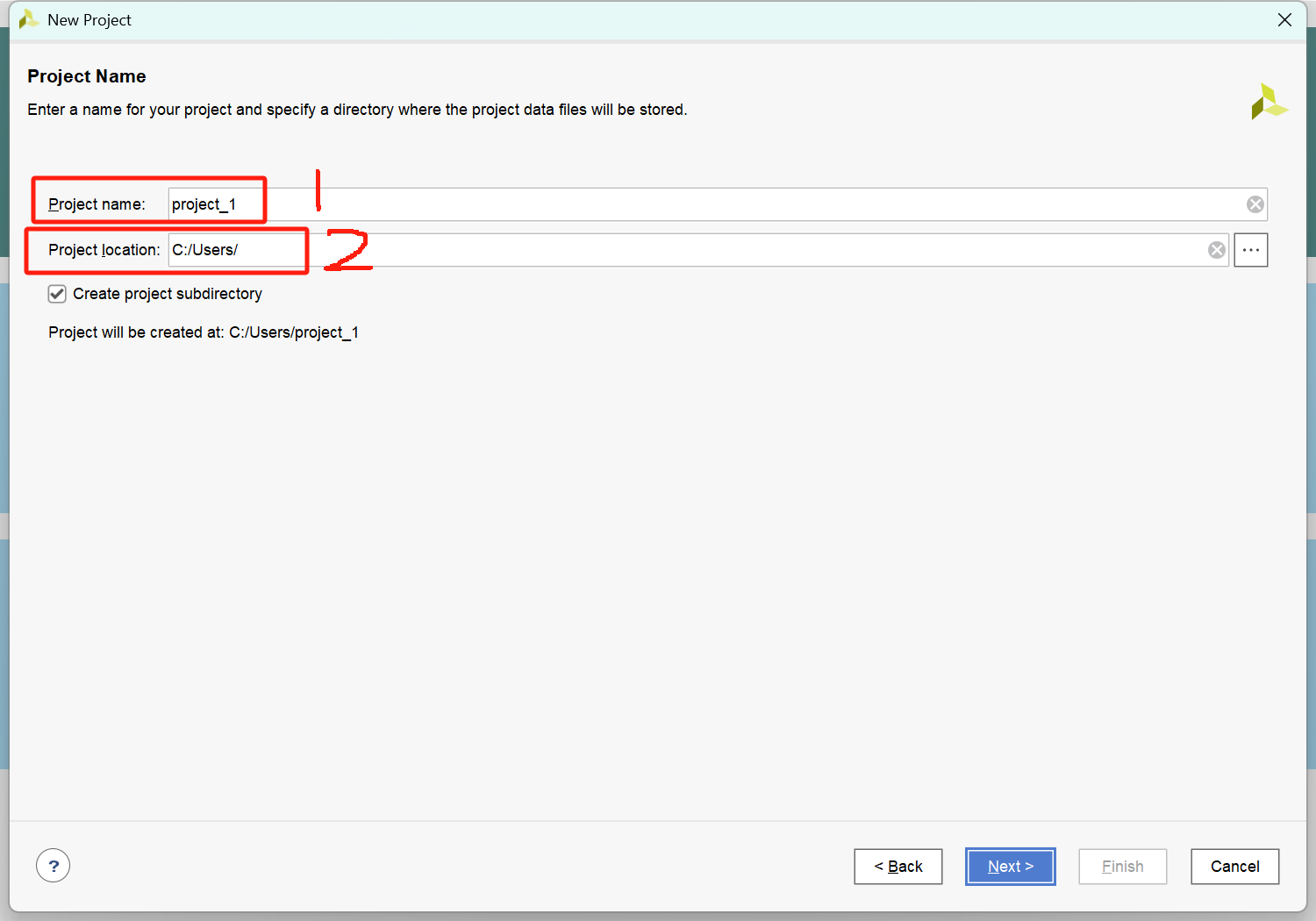

二.为工程取名和选取地址

1.为自己的工程取名。

2.为自己要创建的工程选取地址

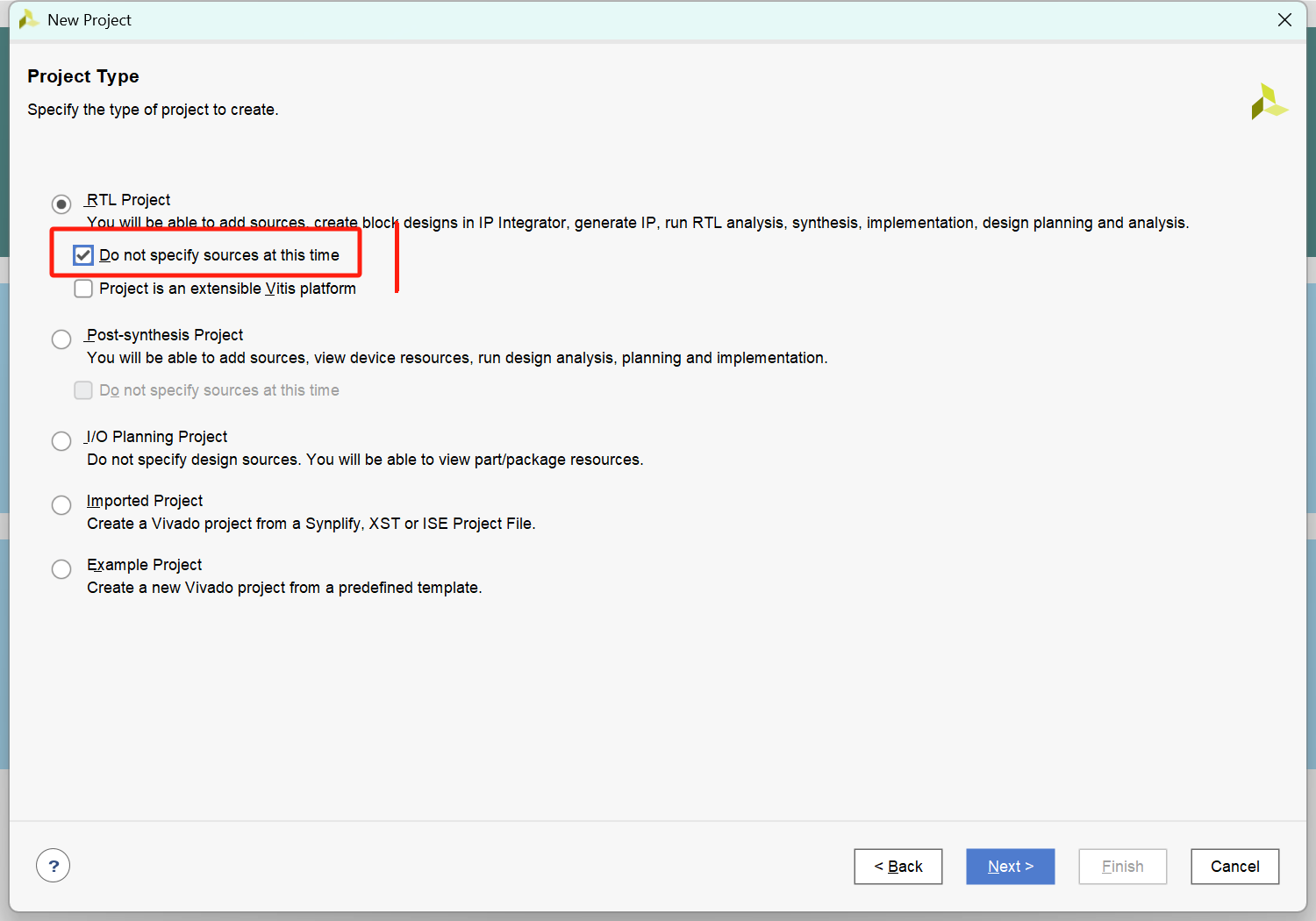

三.文件创建选择

1.这里作者选择的是不定义任何源文件,其实就是创建一个空工程的意思,其他的设计文件,仿真文件什么的,都在后面自己手动添加。

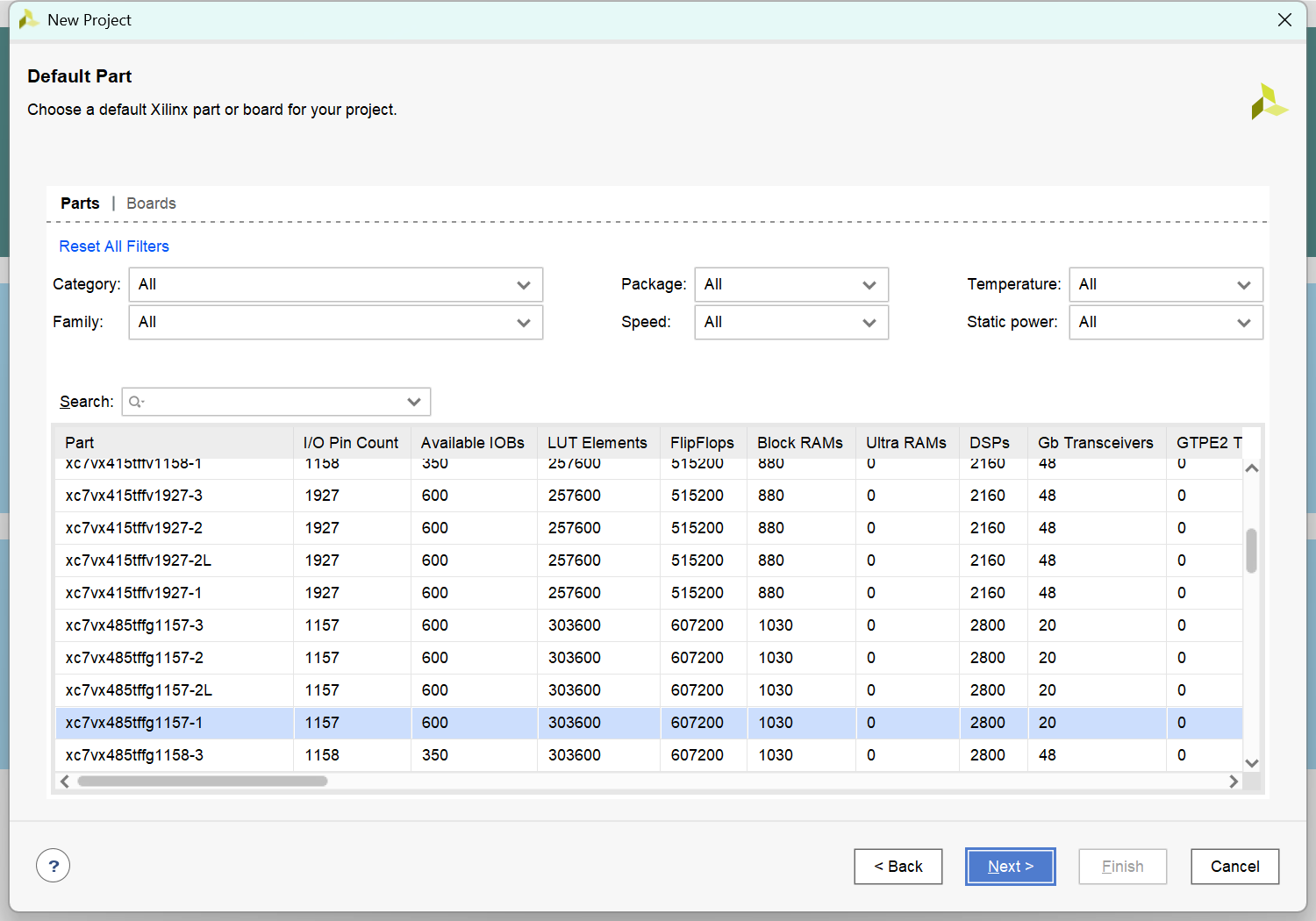

四.芯片选型

这里主要就是选择芯片的名称,也就是你开发板的芯片名称,可以看看买的时候商家给你的硬件手册。

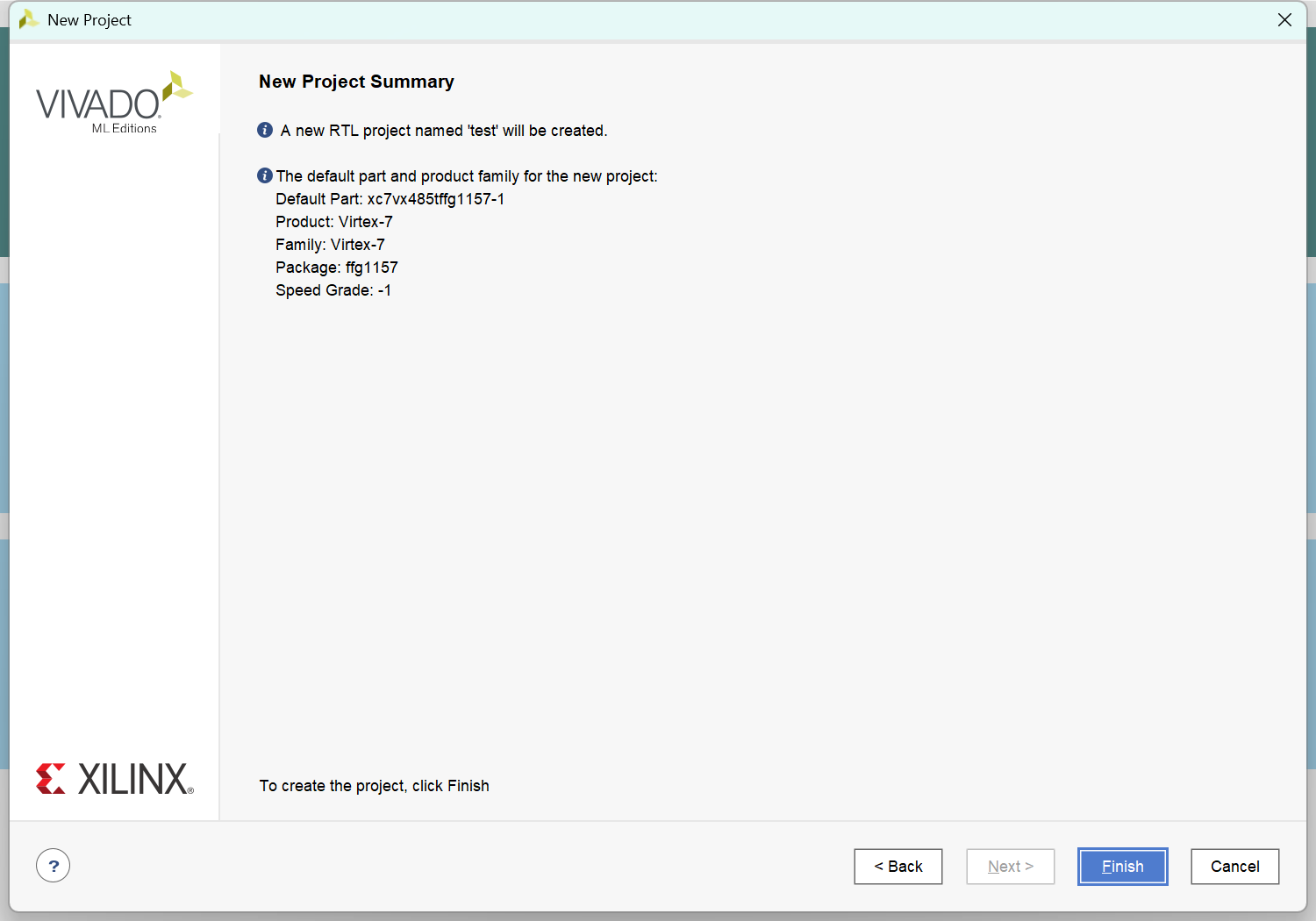

五.完成

这里直接点Finish即可,这就代表创建工程成功了。

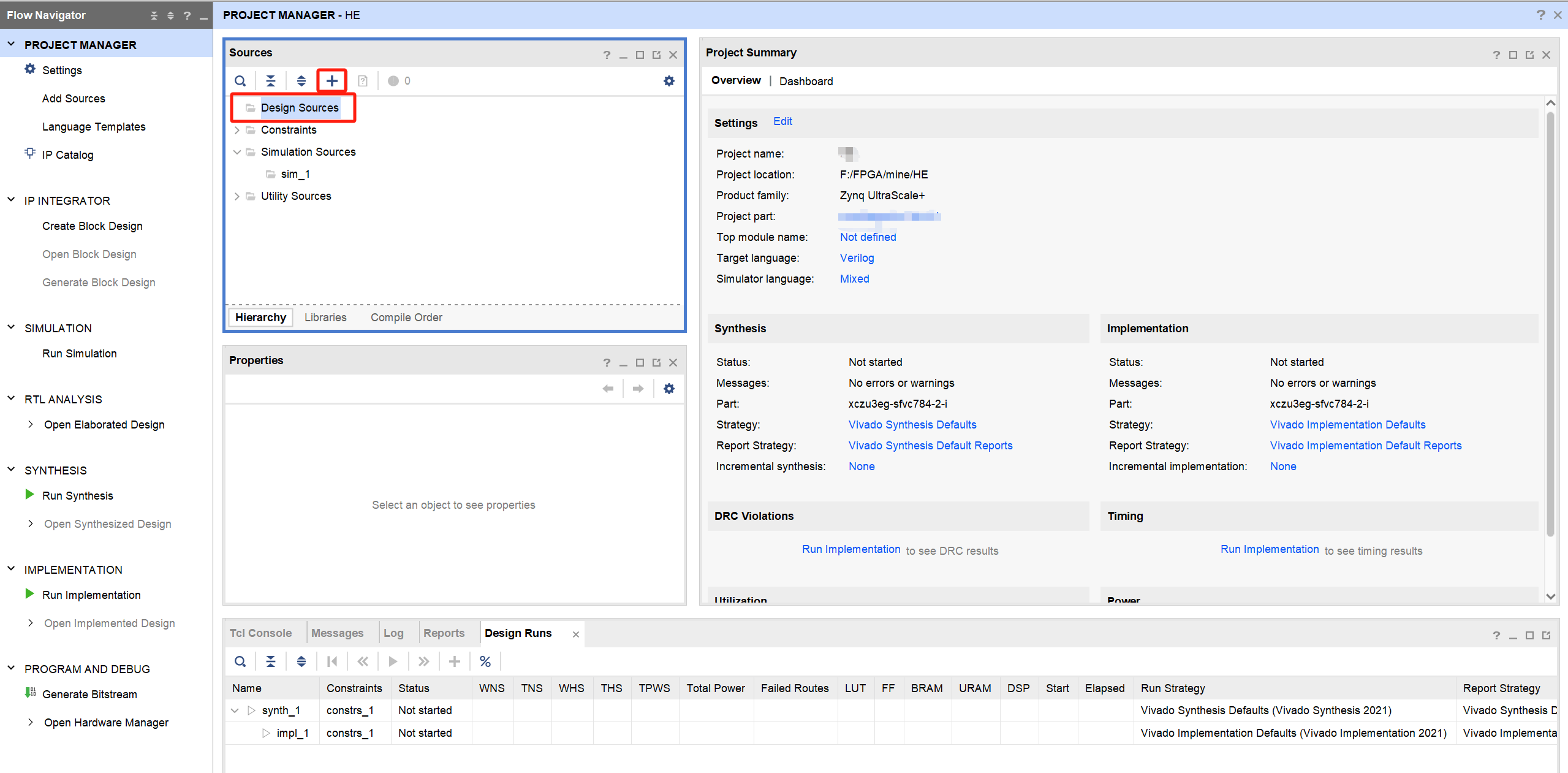

加入设计文件

可以看见图中红框标记的Design Sources,是没有东西的,我们点击图中标记的加号。

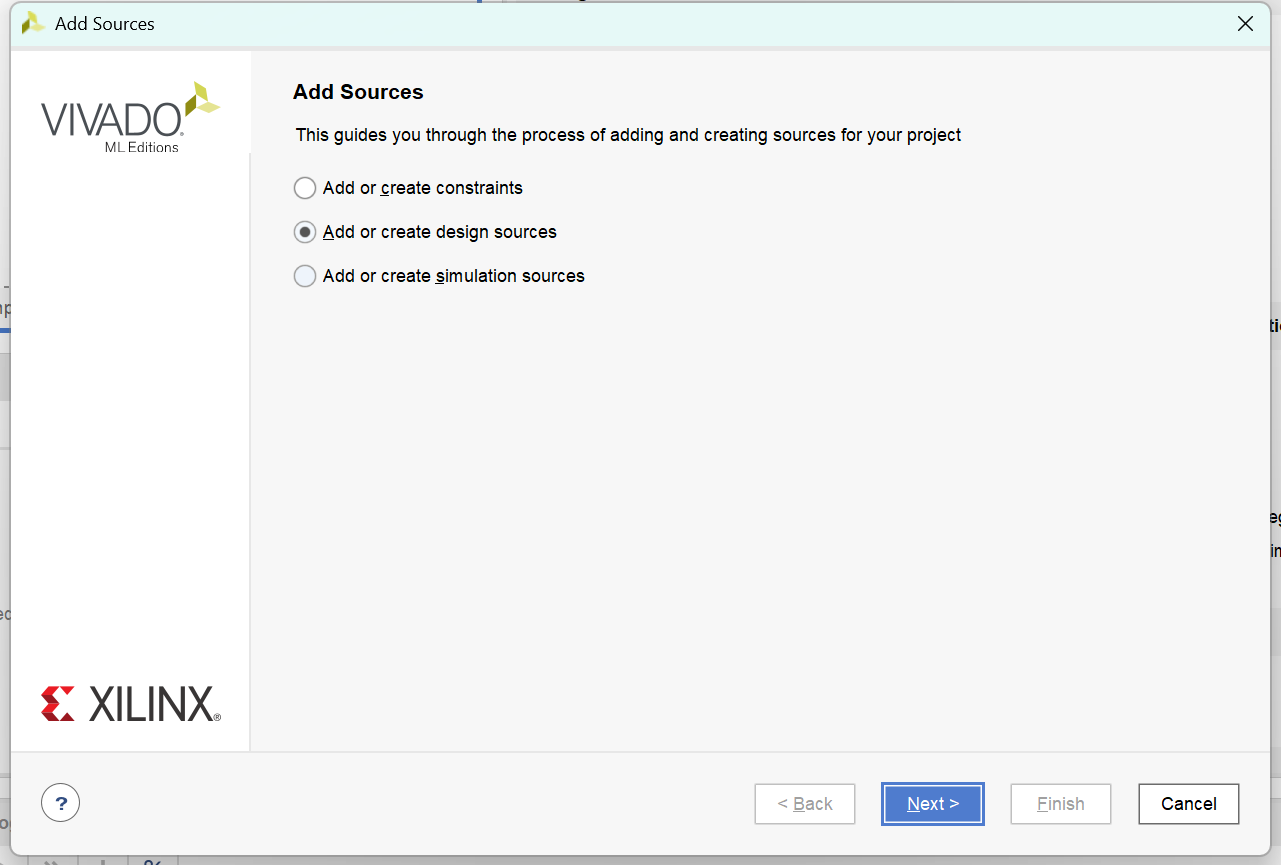

这里我们选择第二个选项,添加设计文件,我讲讲这三个选项分别是干嘛的吧。

第一个是添加约束文件,比如引脚约束

第二个是添加设计文件,就是你写的设计代码

第三个是添加仿真文件,上面写的是simulation,也就是我们常说的tb文件呢。

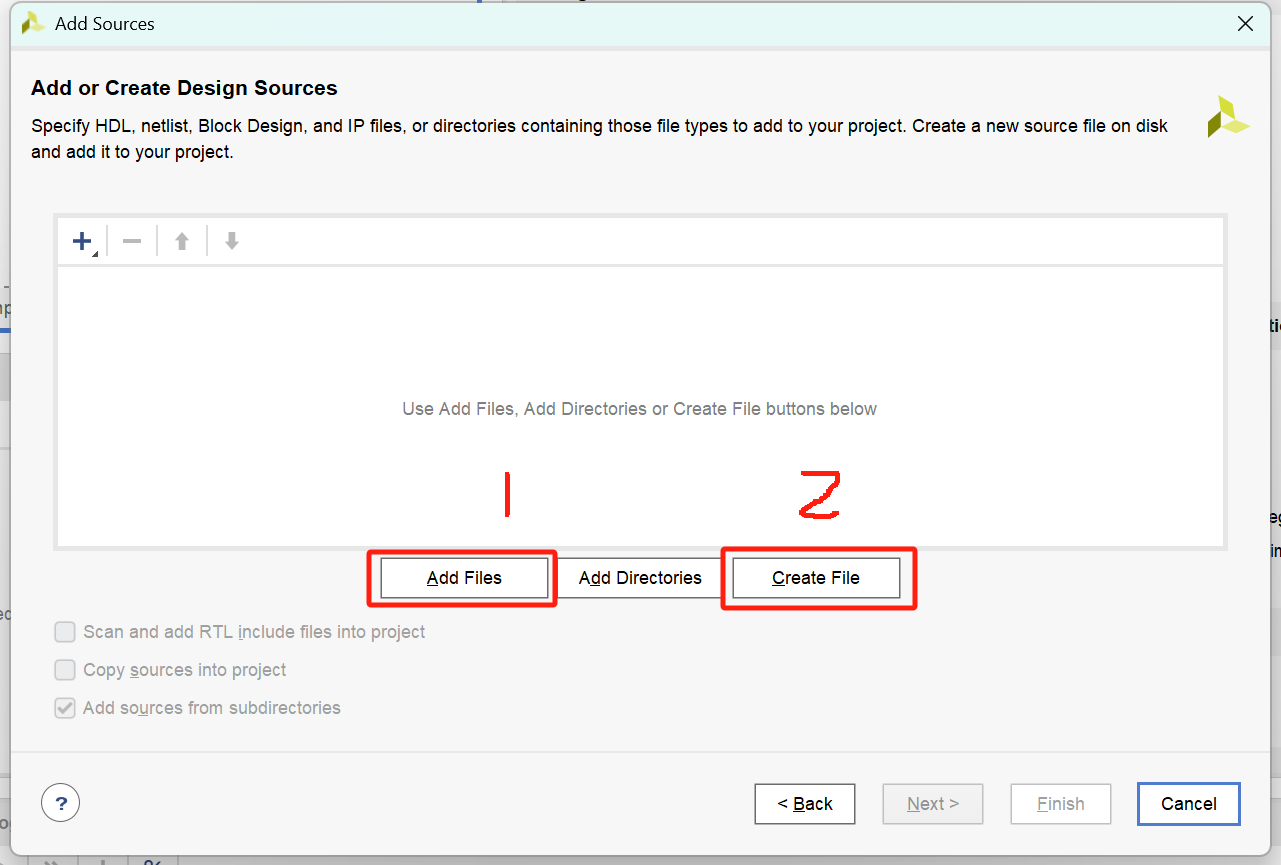

1.Add Files 这个相当于你直接去你的文件夹里面索引你所写的设计文件。

2.Create Files 这个是直接现场创建一个文件,点开之后取个文件名就行了,记得是.v文件哈,比如test.v

没有代码的话,这里作者提供一下自己的代码,作者也是用这个代码来进行IP设置的。

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: // Engineer: // // Create Date: 2025/05/26 23:13:33// Design Name: // Module Name: vtc// Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// ////////////////////////////////////////////////////////////////////////////////////----------------------------------------------------------------------------// Video Timing Controller (VTC) Core//----------------------------------------------------------------------------// 功能:生成标准视频时序信号(同步脉冲、数据有效等),可配置多种视频格式// 特性:// - 完全参数化水平/垂直时序// - 支持正向/负向同步脉冲极性// - 同步输出使能控制// - 实时行列计数器输出//----------------------------------------------------------------------------module vtc #( //------------------------------ // 视频时序参数 //------------------------------ parameter H_DISPLAY = 1920, // 水平有效像素数 parameter H_FP = 88, // 水平前沿(Horizontal Front Porch) parameter H_SYNC = 44, // 水平同步脉冲宽度 parameter H_BP = 148, // 水平后沿(Horizontal Back Porch) parameter H_POLARITY = 1\'b0, // 水平同步极性(0:负极性,1:正极性) parameter V_DISPLAY = 1080, // 垂直有效行数 parameter V_FP = 4, // 垂直前沿(Vertical Front Porch) parameter V_SYNC = 5, // 垂直同步脉冲宽度 parameter V_BP = 36, // 垂直后沿(Vertical Back Porch) parameter V_POLARITY = 1\'b0, // 垂直同步极性(0:负极性,1:正极性) parameter PIXEL_WIDTH = 24 // 像素数据位宽(可选))( //--------