【超详细的易灵思FPGA开发教程】第一章 点亮一颗LED

【超详细的易灵思FPGA开发教程】 第一章 点亮一颗LED

-

- 前言及开发环境介绍

- 新建工程

- 添加源文件

- 代码介绍

- interface designer工具的使用

- 编写顶层模块

- 时序约束

- 编译生成bitstream

- 烧入bit文件

-

- 实验现象

- 实验总结

前言及开发环境介绍

Efinity :2024.2

FPGA : Ti60F100S3F2

该系列后续会增加LVDS MIPI DSI CSI HDMI的实验开发流程

新建工程

软件界面

创建工程

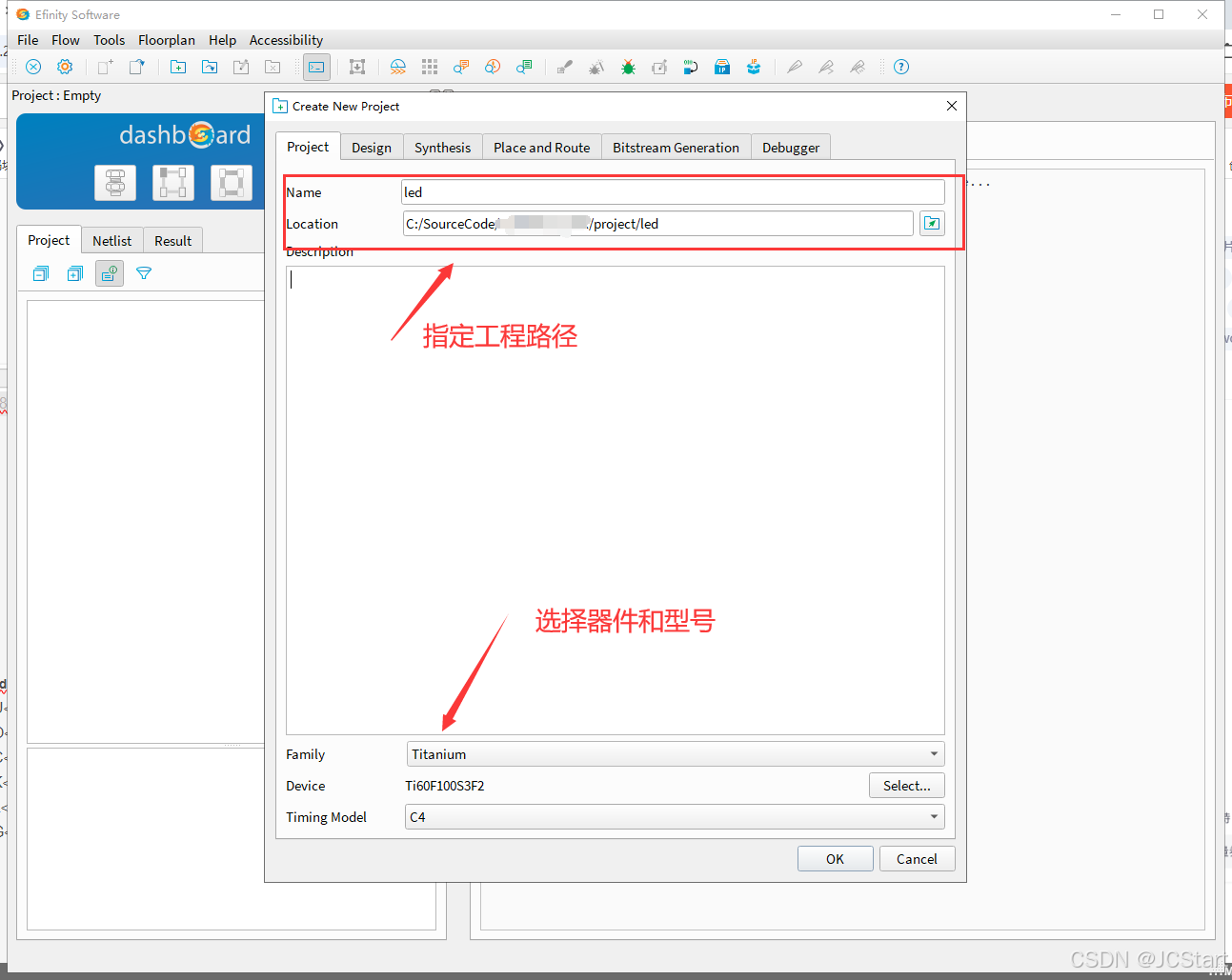

步骤1: File --> Create Project

步骤2: 在Project Editor中选择路径并输入工程名

步骤3: 选择器件(家族) 及速率等级

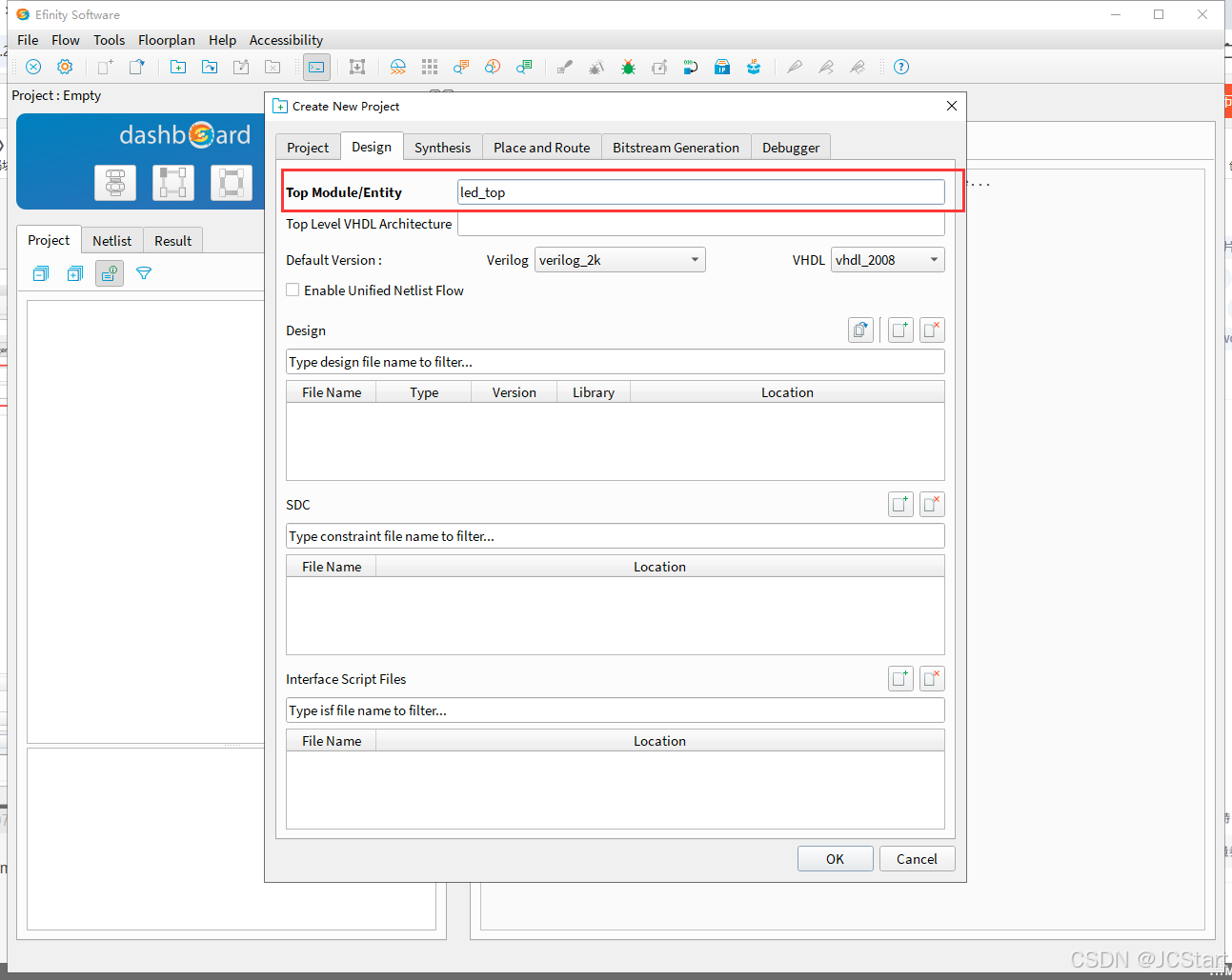

定义好顶层模块(如果没有输入top module名, 软件会自己选择top module,编辑结

果不正确),可以写定义一个名字 后面不合适可以再改动。

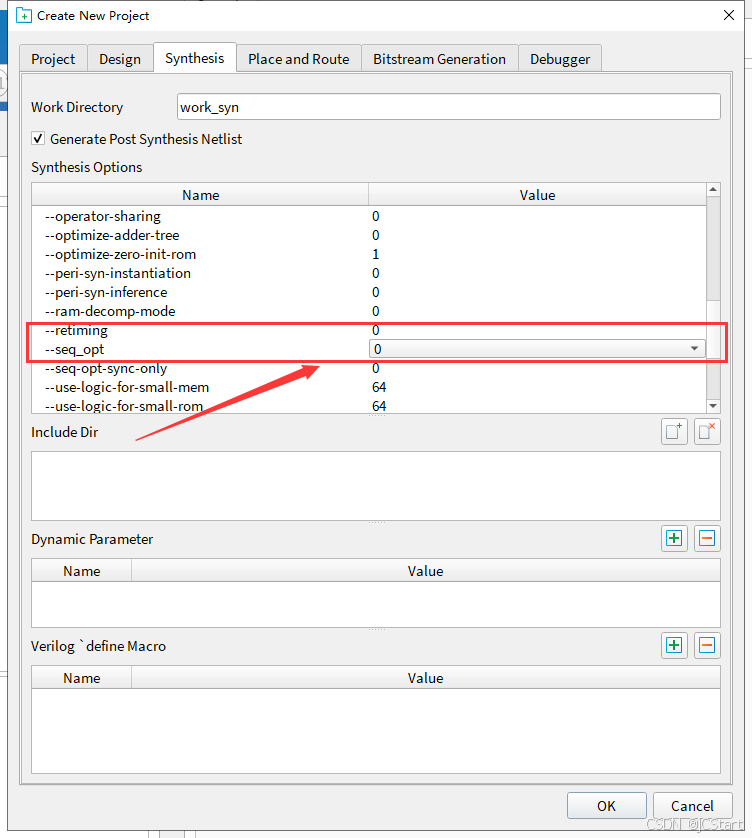

把retiming和seq_opt设置为0

目前打开这两个选项可能导致编译结果有差异

点击ok, 新建工程完成。

添加源文件

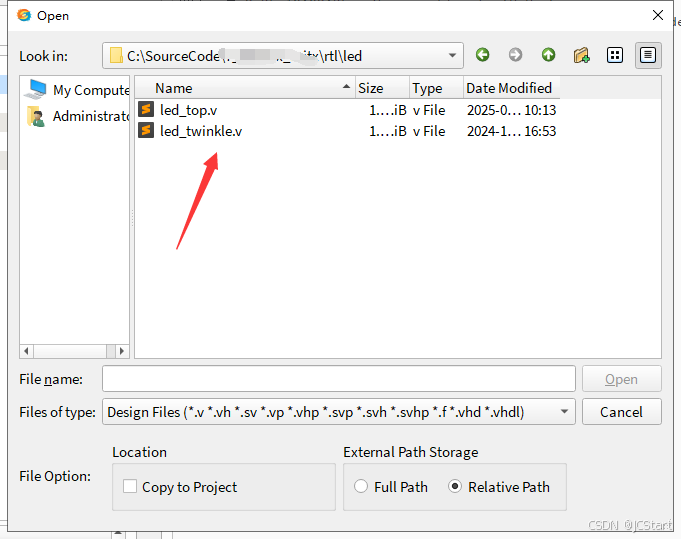

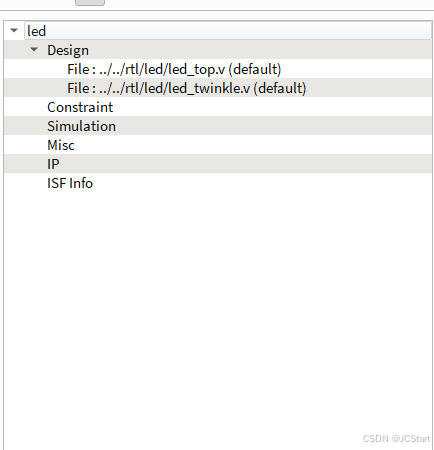

步骤1: 选择Design右击, 点击Add

步骤2:选择文件

添加成功

代码介绍

module led_twinkle ( input wire clk , // Clock input wire rst , output wire [1:0] led);localparam DELAY_CNT = 10_000_000;reg [25:0] cnt = 0;reg led_r = 0;always @(posedge clk) begin if(rst) begin led_r <= 1\'b0; cnt <= 26\'d0; end else if (cnt == DELAY_CNT - 1\'b1)begin led_r <= ~led_r; cnt <= 26\'d0; end else cnt <= cnt + 1\'b1;endassign led[0] = led_r;assign led[1] = ~led_r;endmoduleinterface designer工具的使用

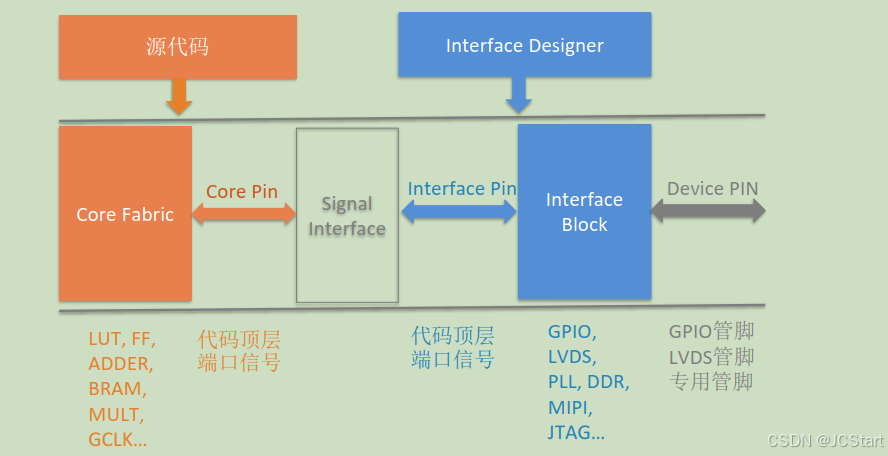

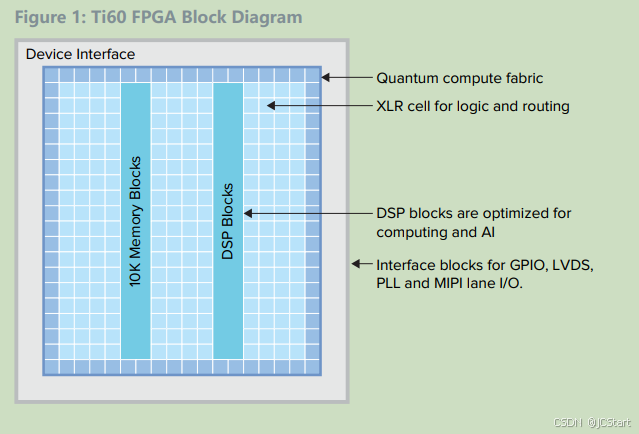

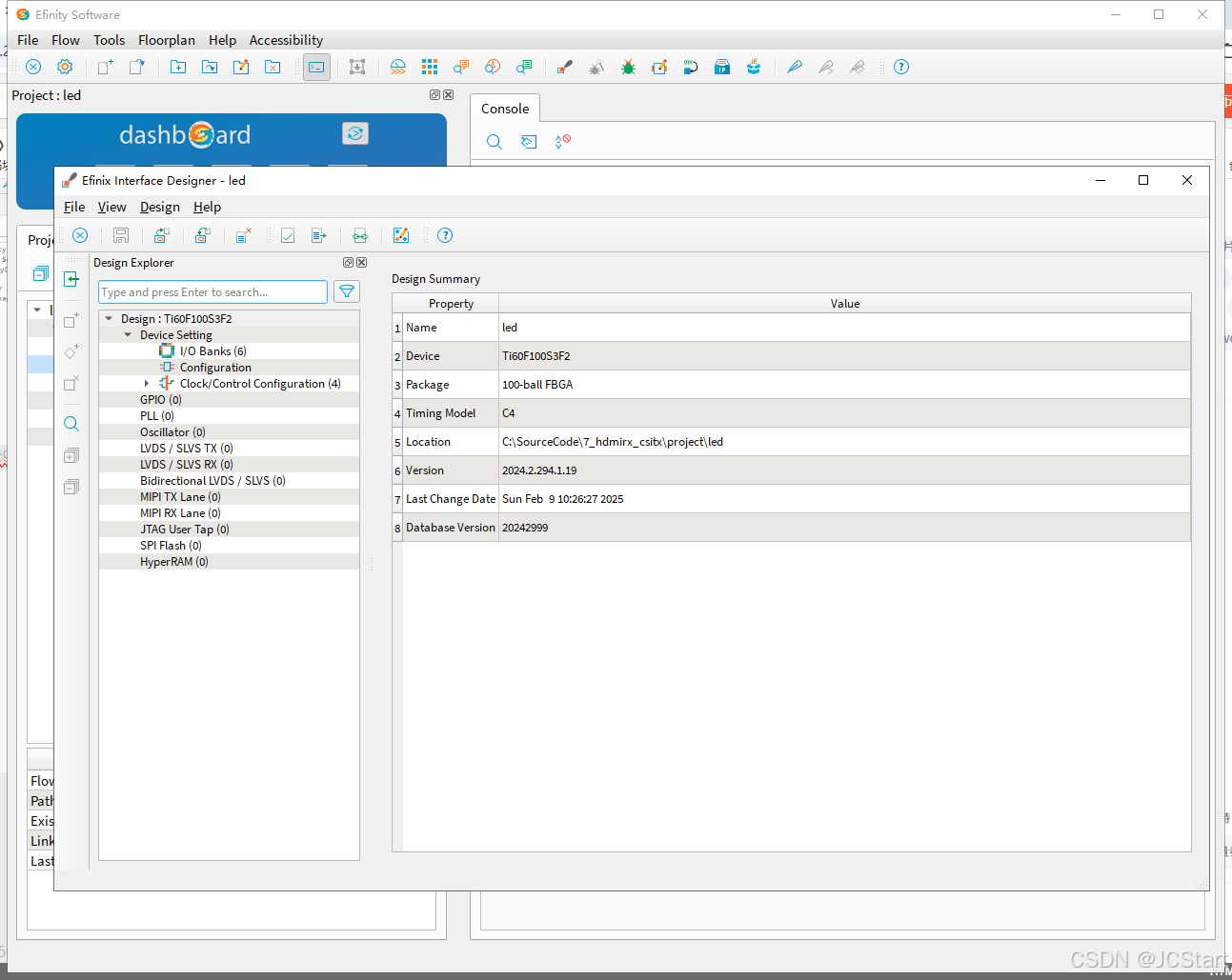

Efinty是通过interface designer工具来设置IO等和外设相关的接口及电气属性的。采用的把逻辑资源和硬核资源分开的架构,代码部分只针对逻辑资源,也就是图中的10K Memory Blocks,而IO及其他硬核部分的配置在interface Designer工具中,也就是图中的Interface blocks for GPIO, LVDS,

PLL and MIPI lane I/O.

下图是interface与Core的关系,它们之间通过被称作 Siganl Interface的连线资源实现互联 。

简单点理解就是单片机外设的概念,FPGA调用外设进行编程。

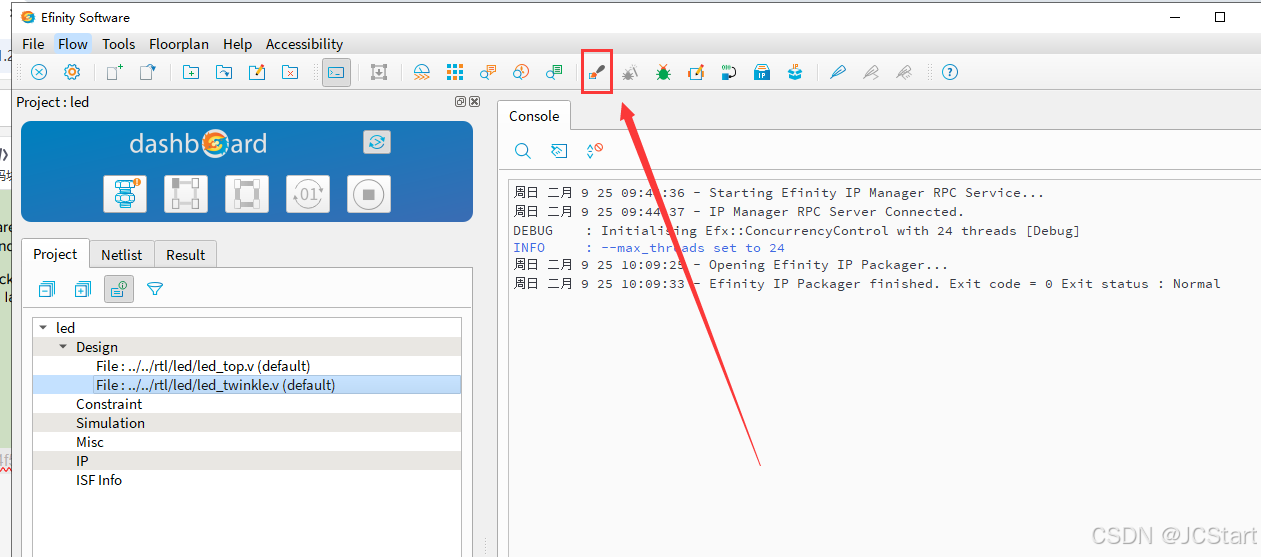

Interface designer操作界面的打开通过下面的Open Interface

Desinger来实现。

这一过程也可以理解为Zynq的Block design 设置,使能各种外设

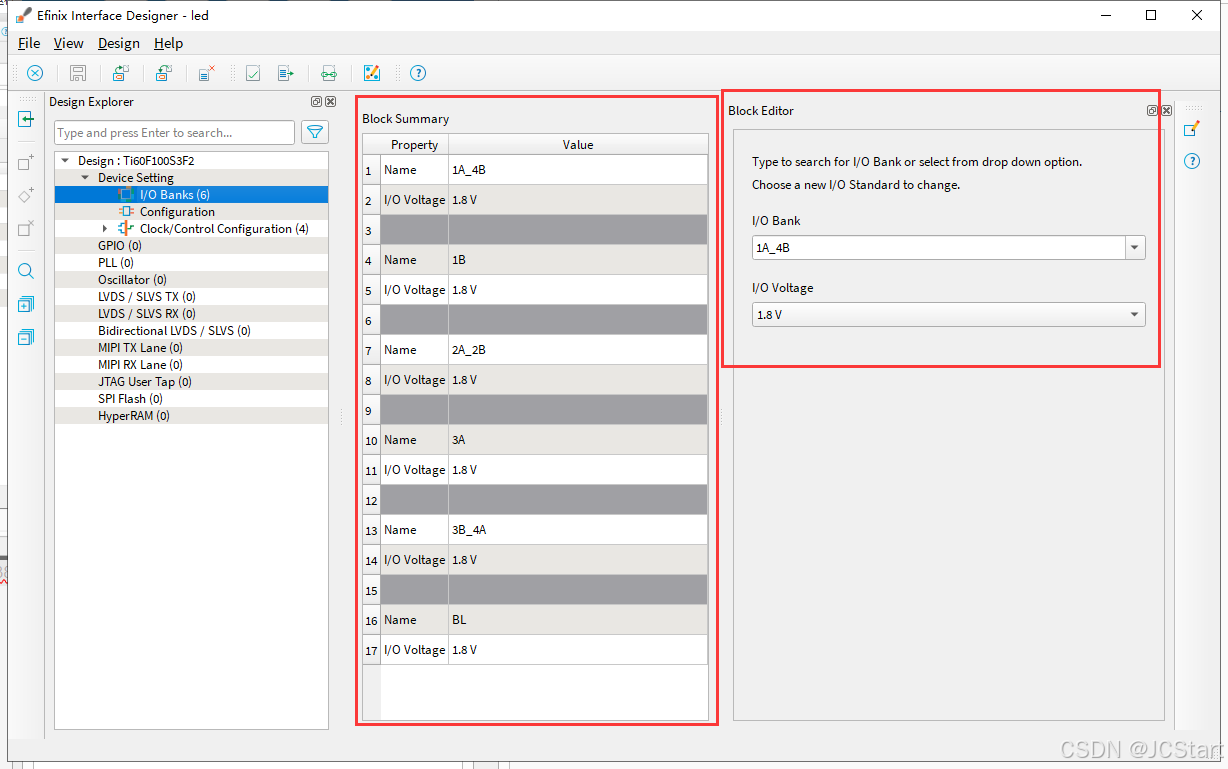

第一步 :Bank电压的设置

硬件电路的bank电压要和interface中的一致, 如果电压设置不一致可能存在长时间运行致使芯片失效。根据原理图设置。

设置位置在Device Setting -->I/O Banks

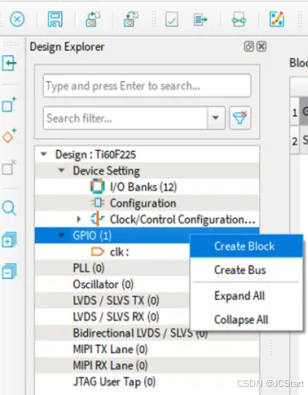

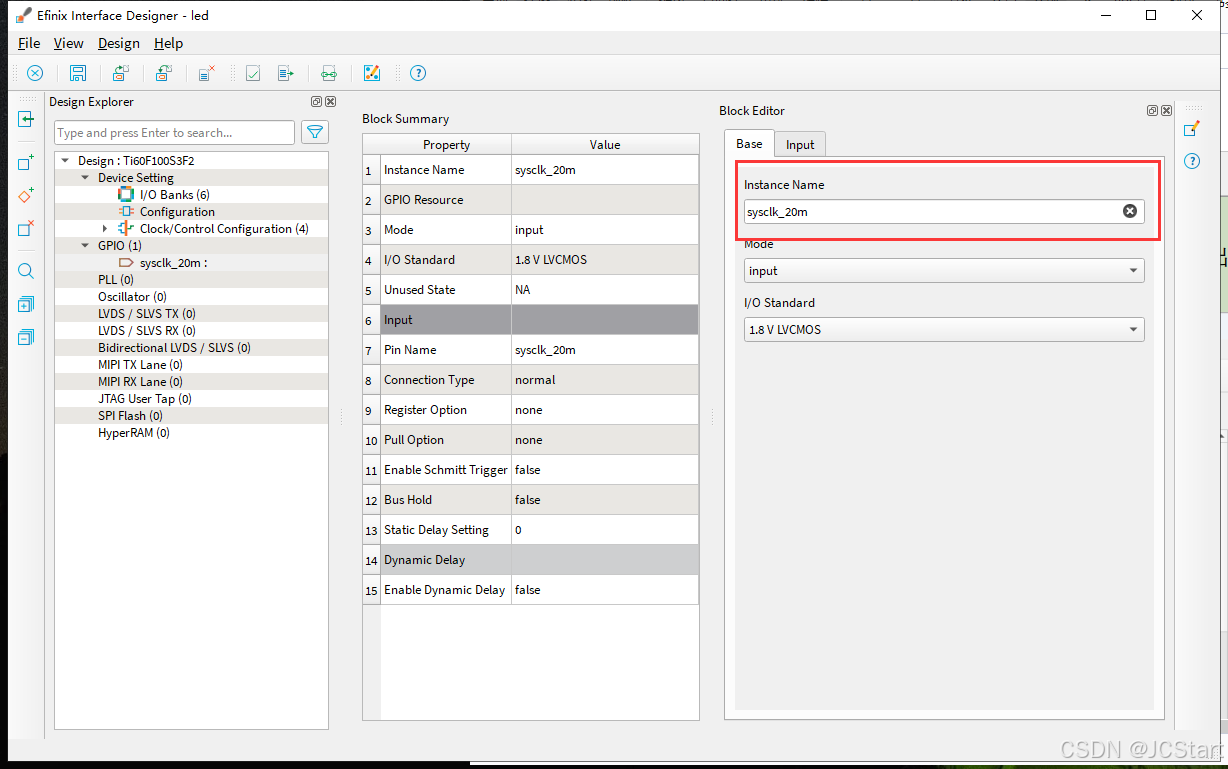

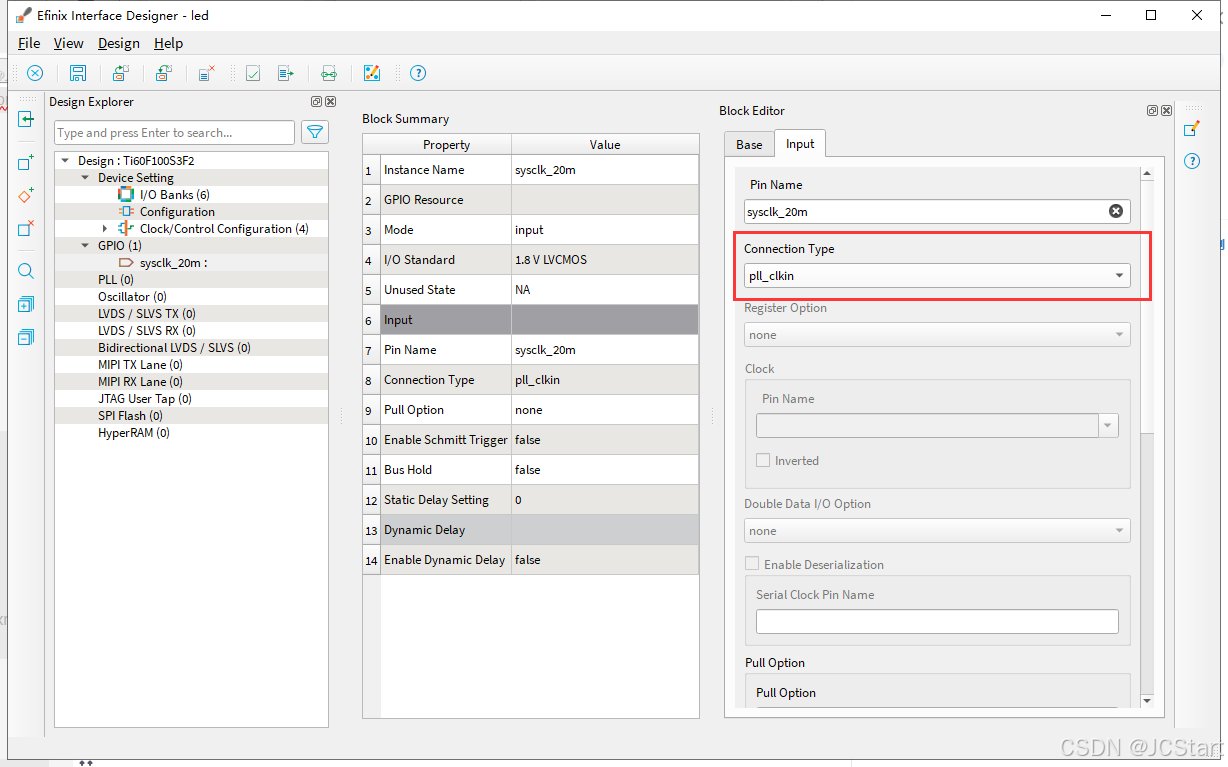

第二步 :添加时钟GPIO

例化名称:sysclk_20m 表示外部晶振时钟为20Mhz

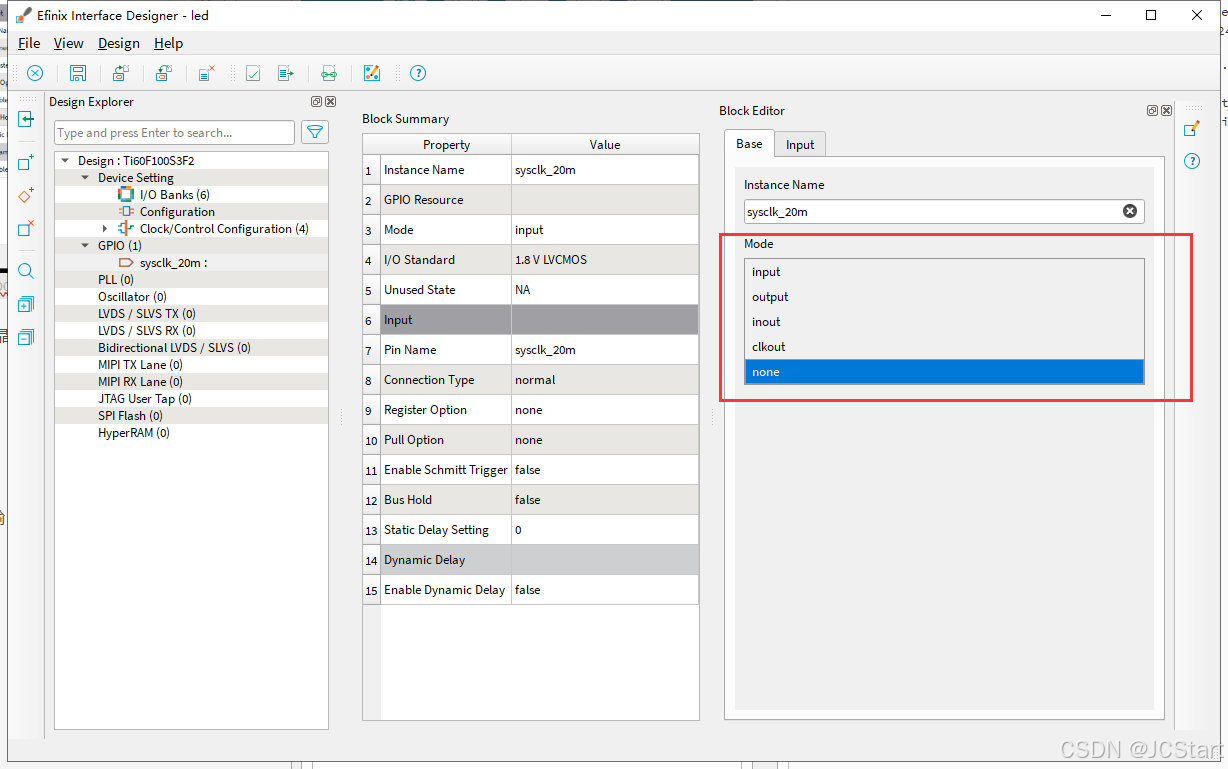

这里有四种选择

Input:把FPGA管脚设置为输入;

Output: 把 FPGA 管 脚 设 置 为 输出;

Inout:把FPGA管脚设置为双向管脚;

Clkout:把FPGA管脚设置为时钟输出;

这里我们选择模式:Input输入

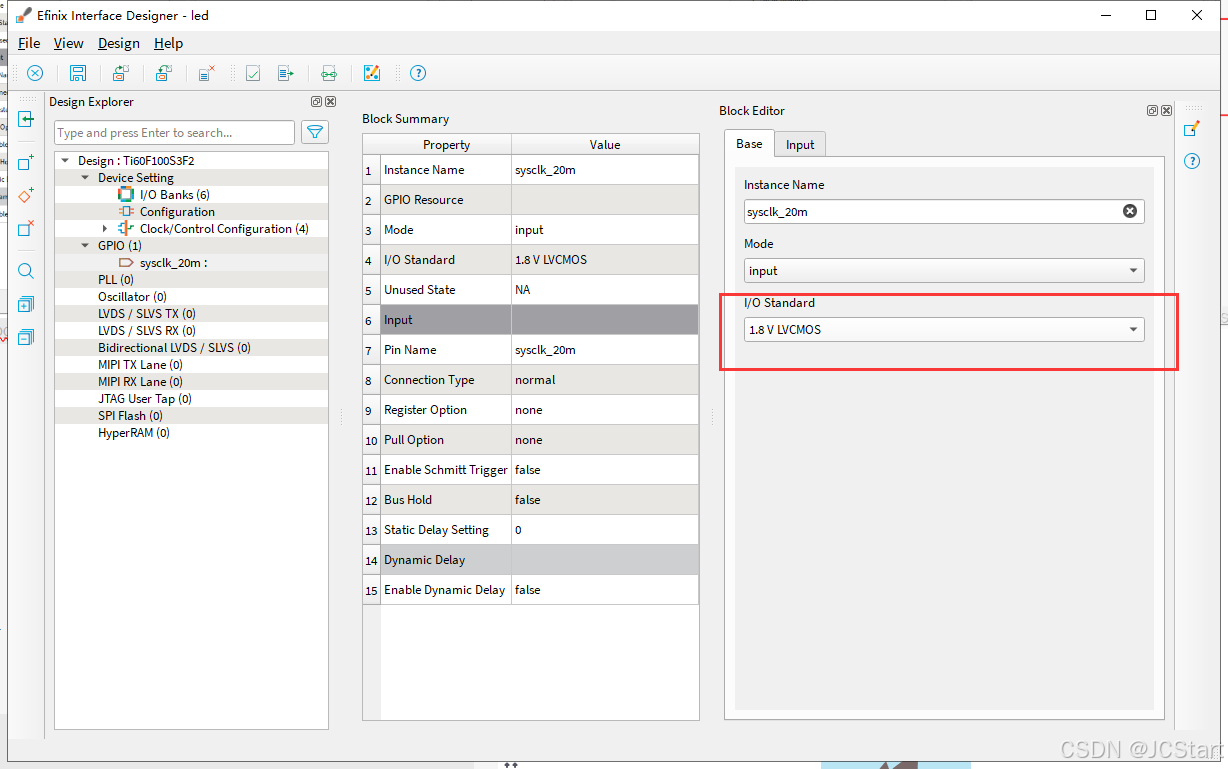

设置IO电平

电平选择:1.8V LVCMOS

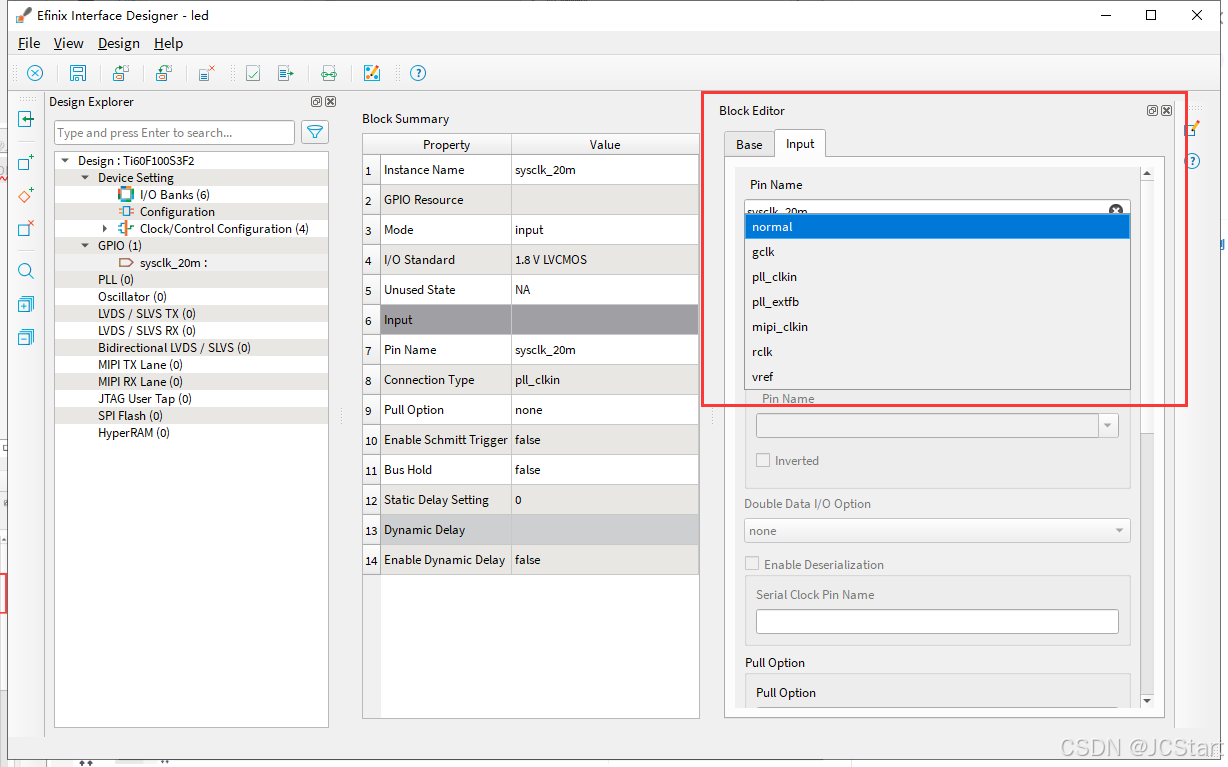

输入类型选择

gclk走全局时钟网线, 可以驱动PLL也可以直接驱动内部逻辑用于普通的GPIO;

PLL_CLKIN表示这个IO是用于驱动PLL的;

我们选择pll_clkin

我们选择pll_clkin

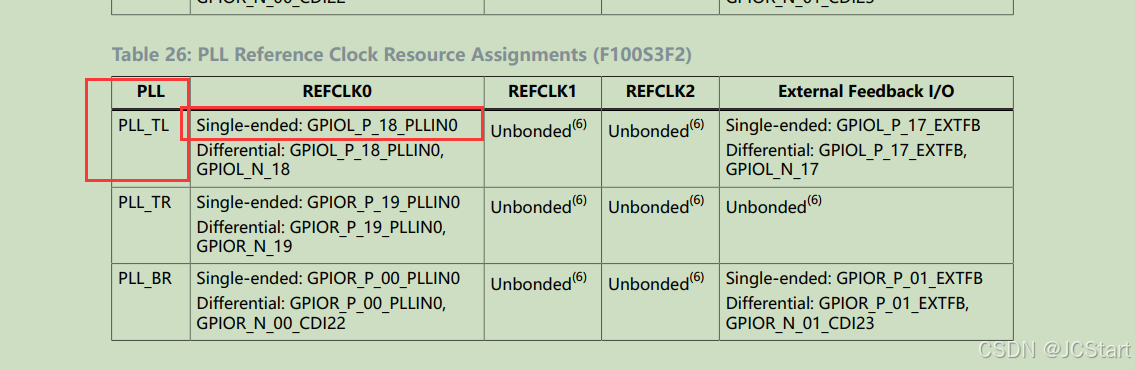

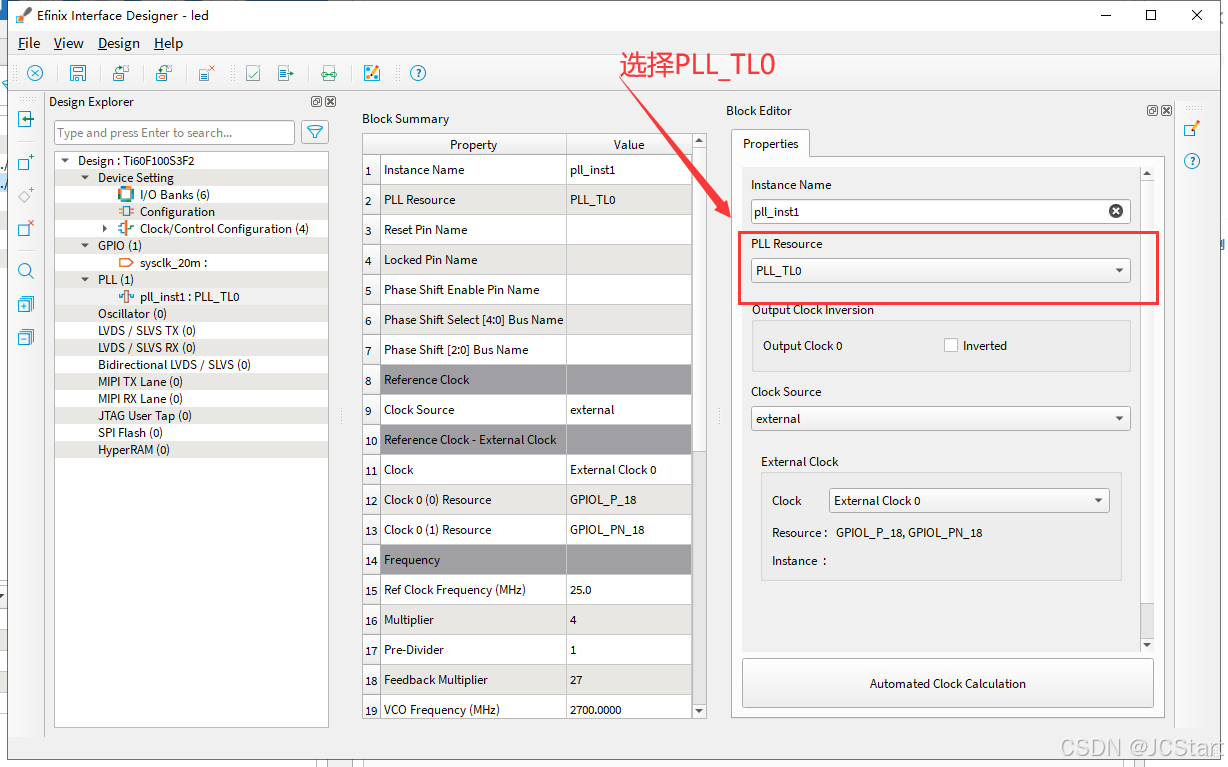

第三步 :锁相环的设置

原理图上Pllin的输入管脚是B3(GPIOL_P_18),参考Ti60datasheet-v2 手册中,所驱动的PLL应该选择TL

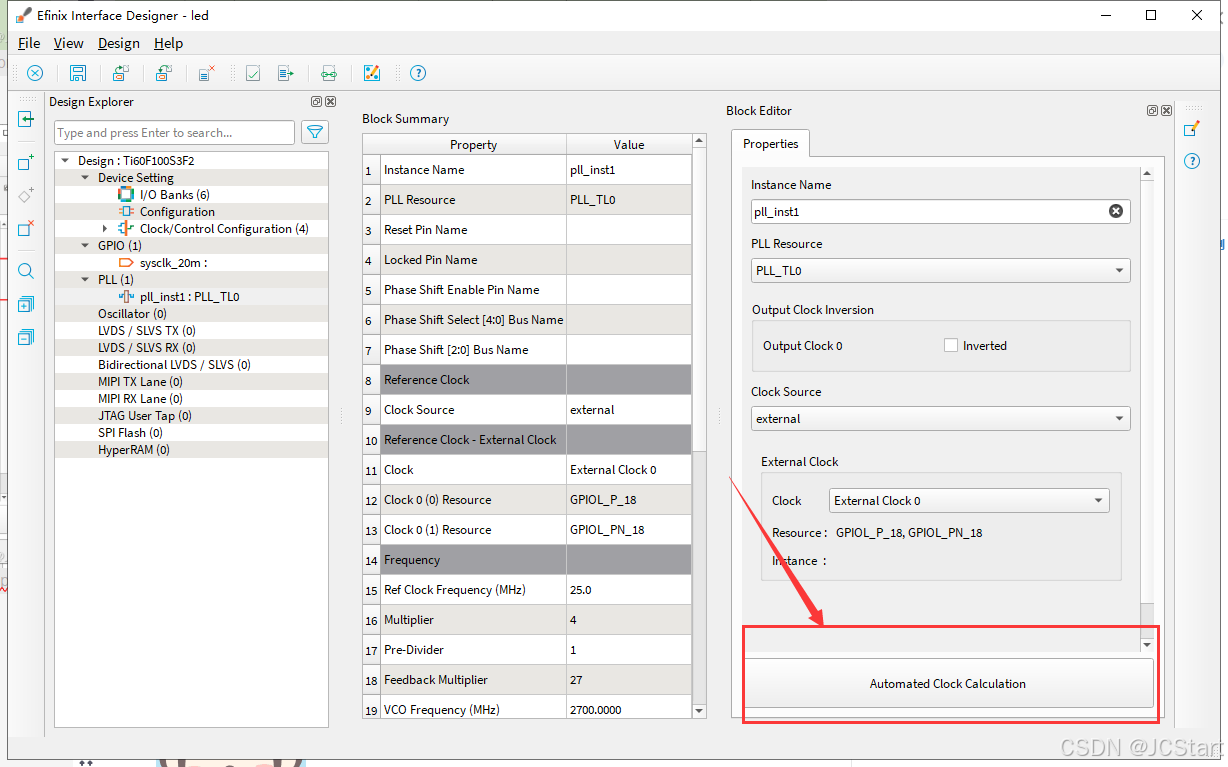

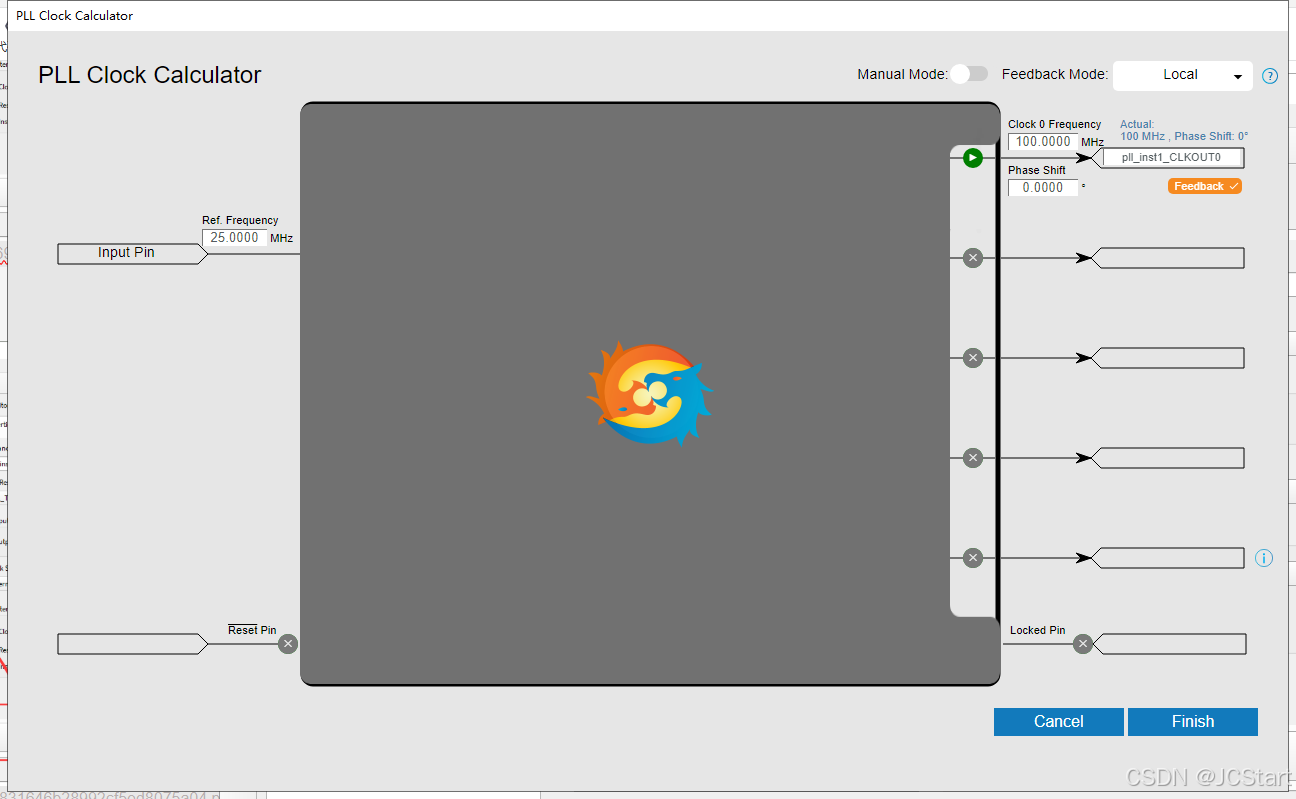

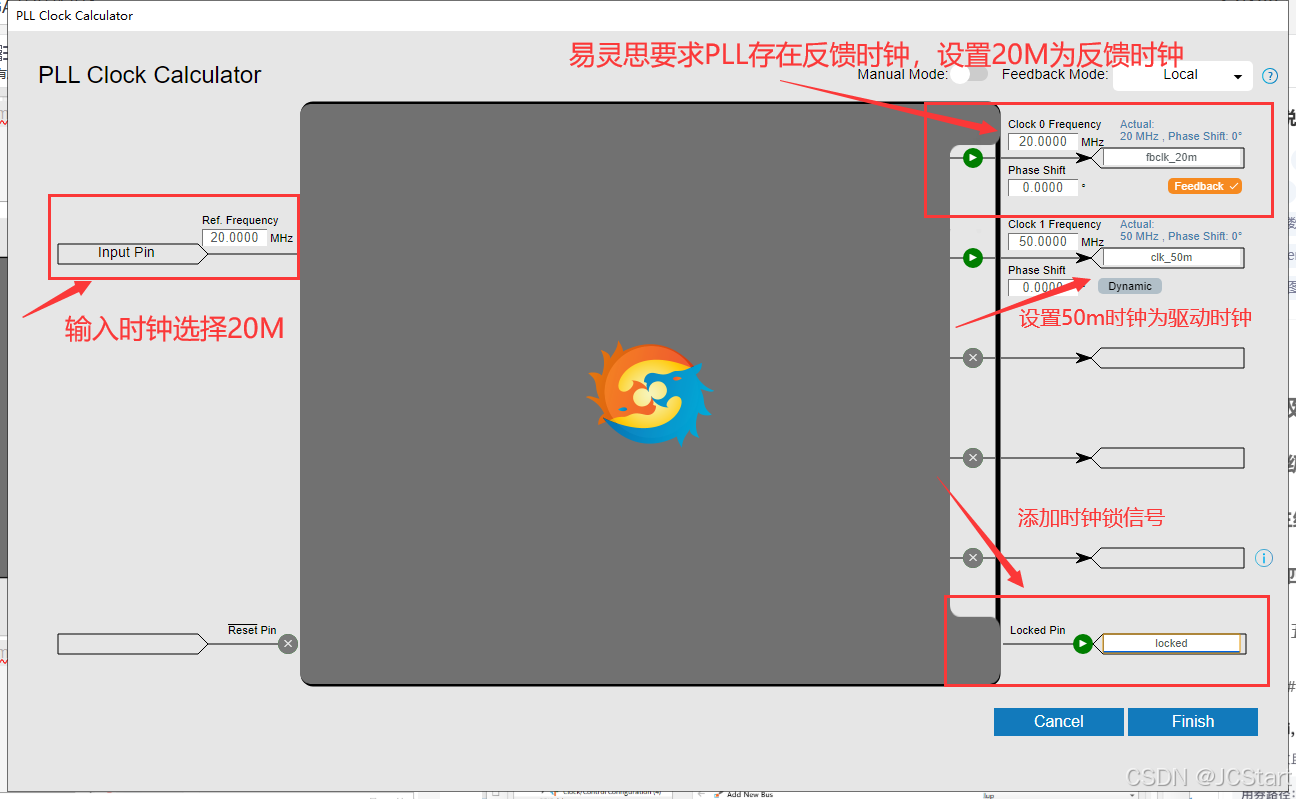

点击Automated Clock Calculation

PLL时钟配置界面

输入时钟按照原理图上选择20M,设置20M为反馈时钟,50M为驱动时钟,添加锁信号,为之后编写同步复位模块使用。

点击Finish完成。

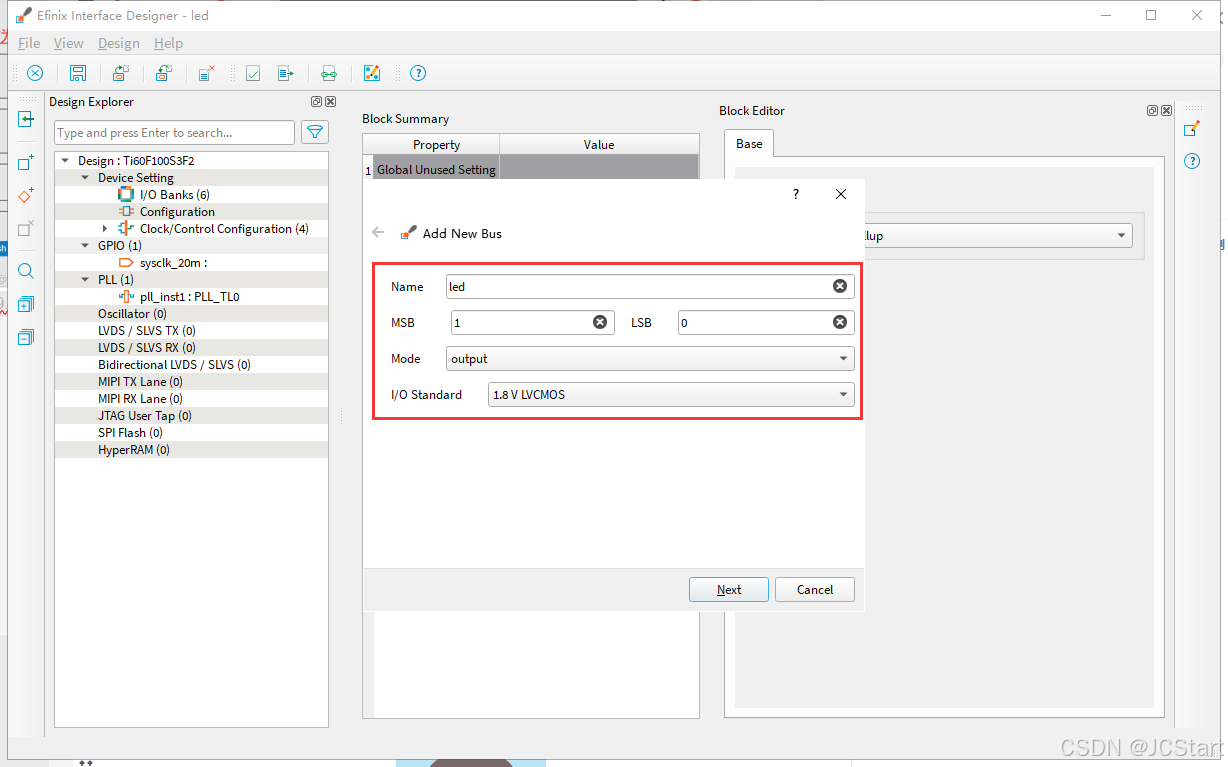

第四步 :添加GPIO外设

GPIO->Create Bus

总线命名为led,为[1:0] 共两位

模式选择output 输出

电平选择1.8V

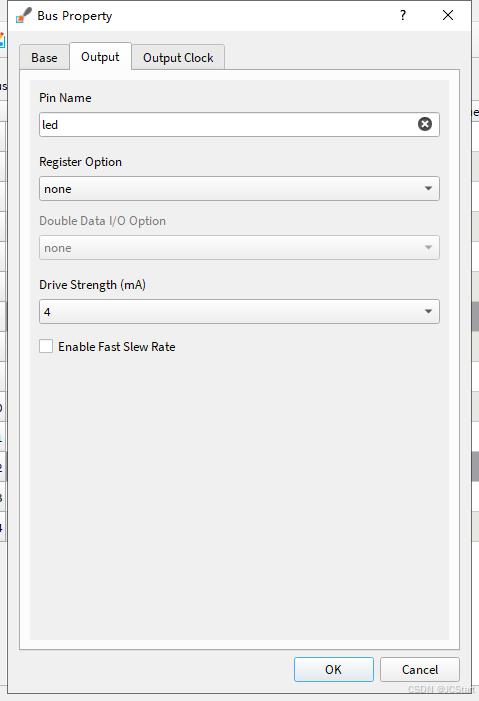

pin name 设置为led

register option:是否添加IO寄存器

Double Data I/O Option 是否设置IO为双延采样,这里选择none

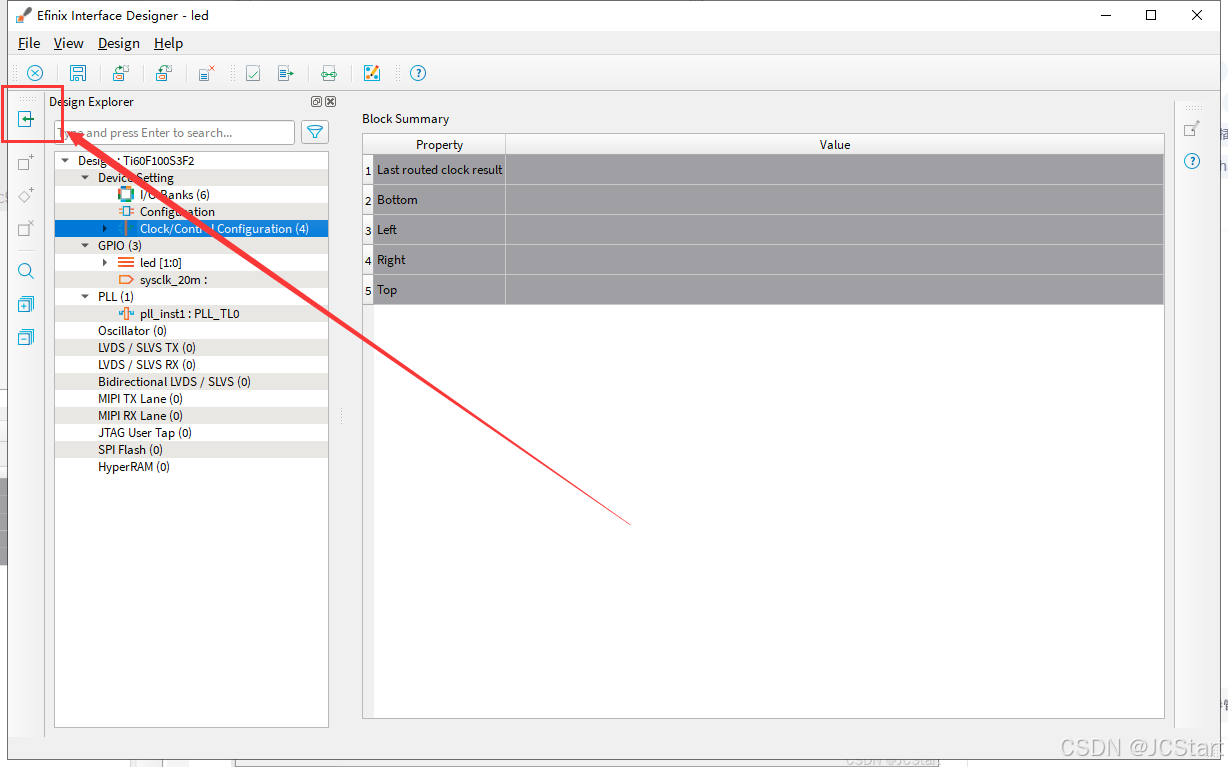

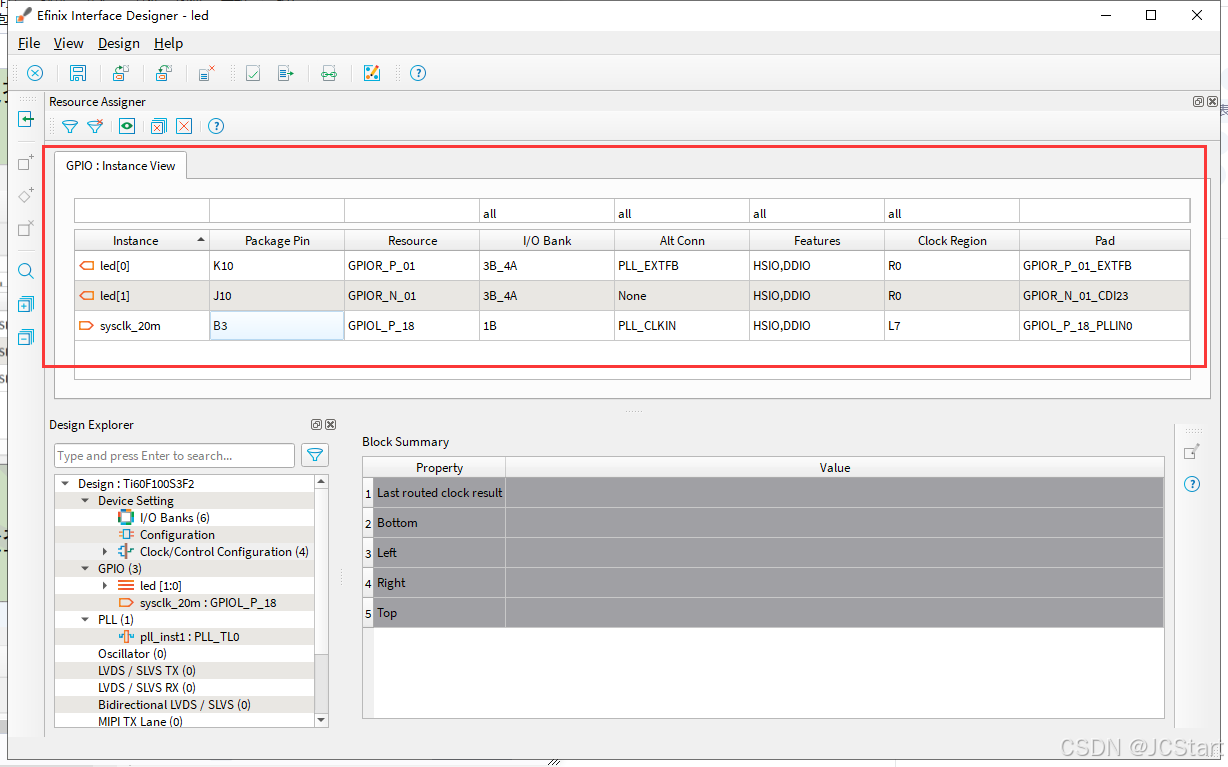

第五步 :IO分配

需要设置的有三个引脚 两个LED 一个20M时钟输入,根据原理图设置如下

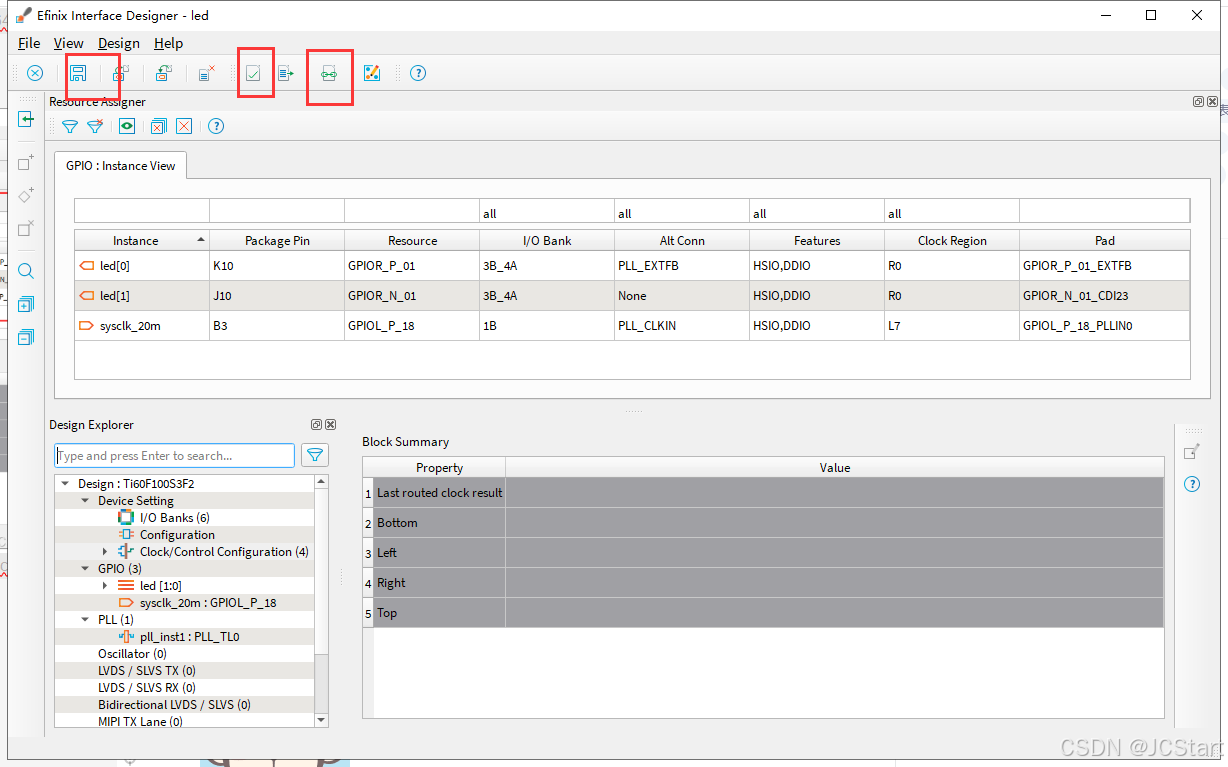

设置完成后,依次点击 保存-检查-连接 按钮 没有报错则约束成功:

链接的作用是产生 Efinity Constraint Files,这些文件再下一步编写顶层和约束中会用到

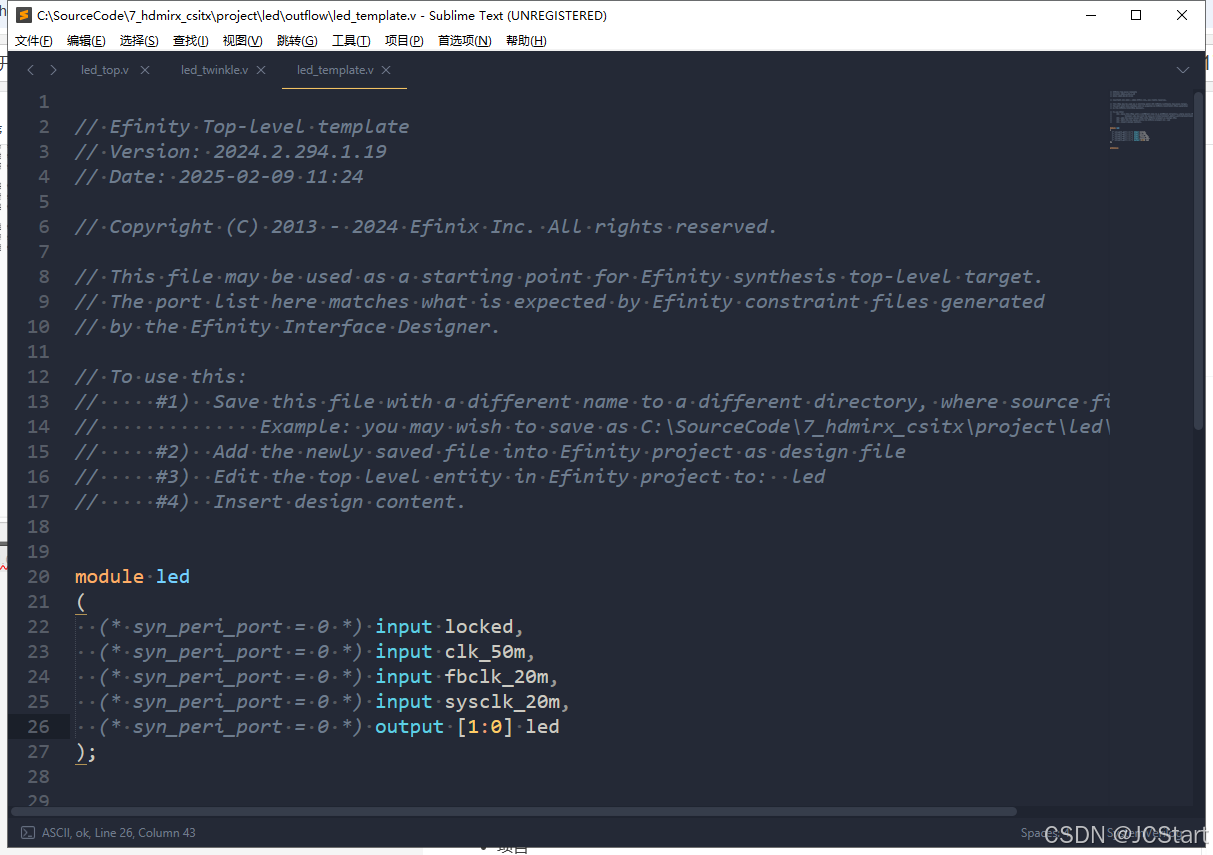

编写顶层模块

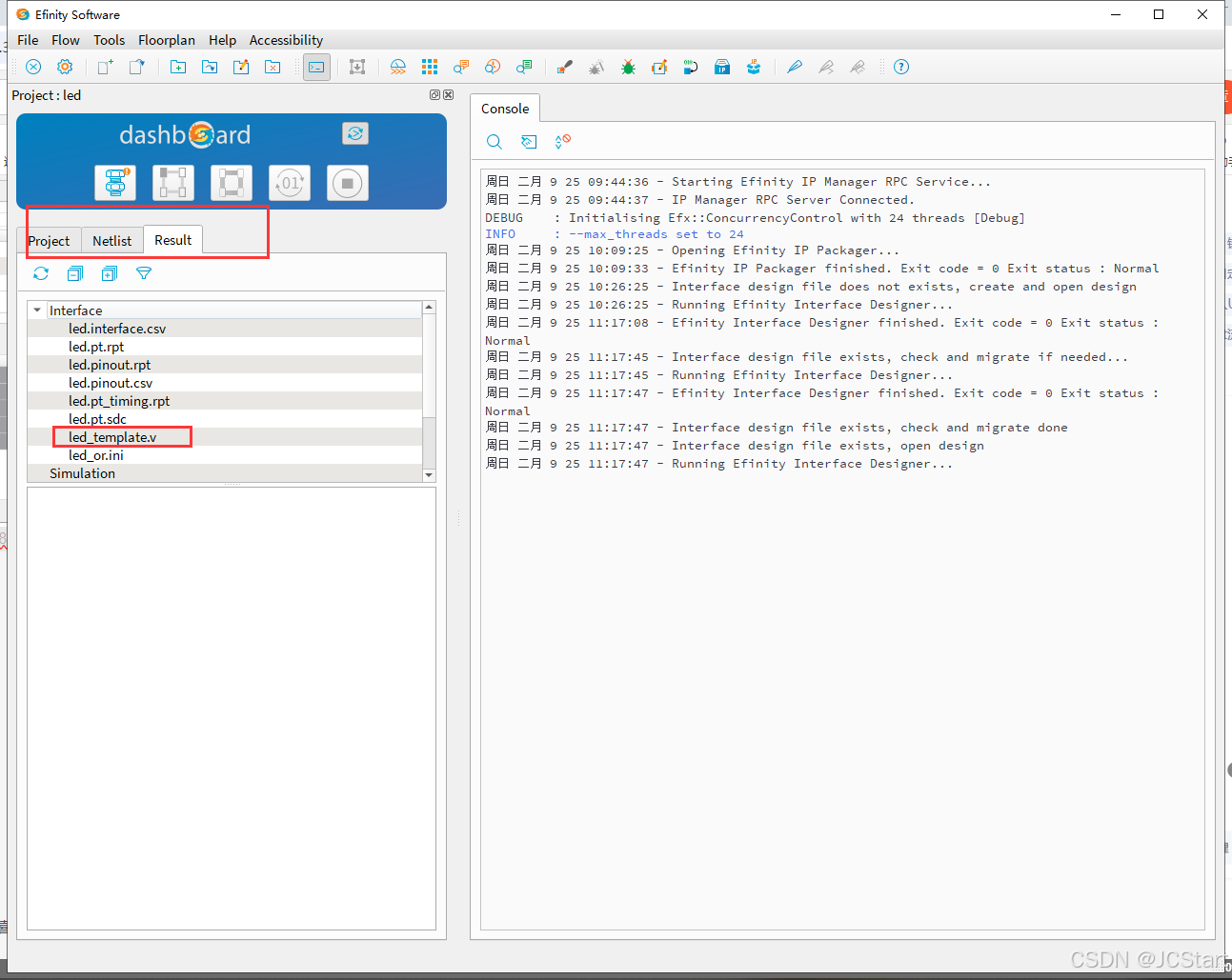

点击Result->led_template.v

可以看到易灵思帮我们定义好了顶层端口。复杂顶层端口到我们的top模块中

顶层模块编写

module led_top( input clk_50m , input locked , output [1:0] led );wire clk_50m_rst ;wire clk_50m_rst_n ;reset u_reset ( .clk_i (clk_50m ), .locked_i (locked ), .rstn_o (clk_50m_rst_n ), .rst_o (clk_50m_rst ));led_twinkle u_led_twinkle ( .clk (clk_50m ), .rst (clk_50m_rst ), .led (led ));复位模块编写 -目的是将locked信号延迟打拍 异步复位同步处理

module reset( input clk_i , input locked_i , output reg rstn_o , output reg rst_o); reg r_locked = 0;always @(posedge clk_i or negedge locked_i) begin if(~locked_i) r_locked <= 0; else r_locked <= 1; endreg [15:0] r_rstn_dly = 0; always @(posedge clk_i or negedge r_locked) begin if(~r_locked) begin rstn_o <= 0; rst_o <= 1; r_rstn_dly <= 0; end else begin r_rstn_dly <= {r_rstn_dly, 1\'b1}; rstn_o <= r_rstn_dly[15]; rst_o <= ~r_rstn_dly[15]; endend时序约束

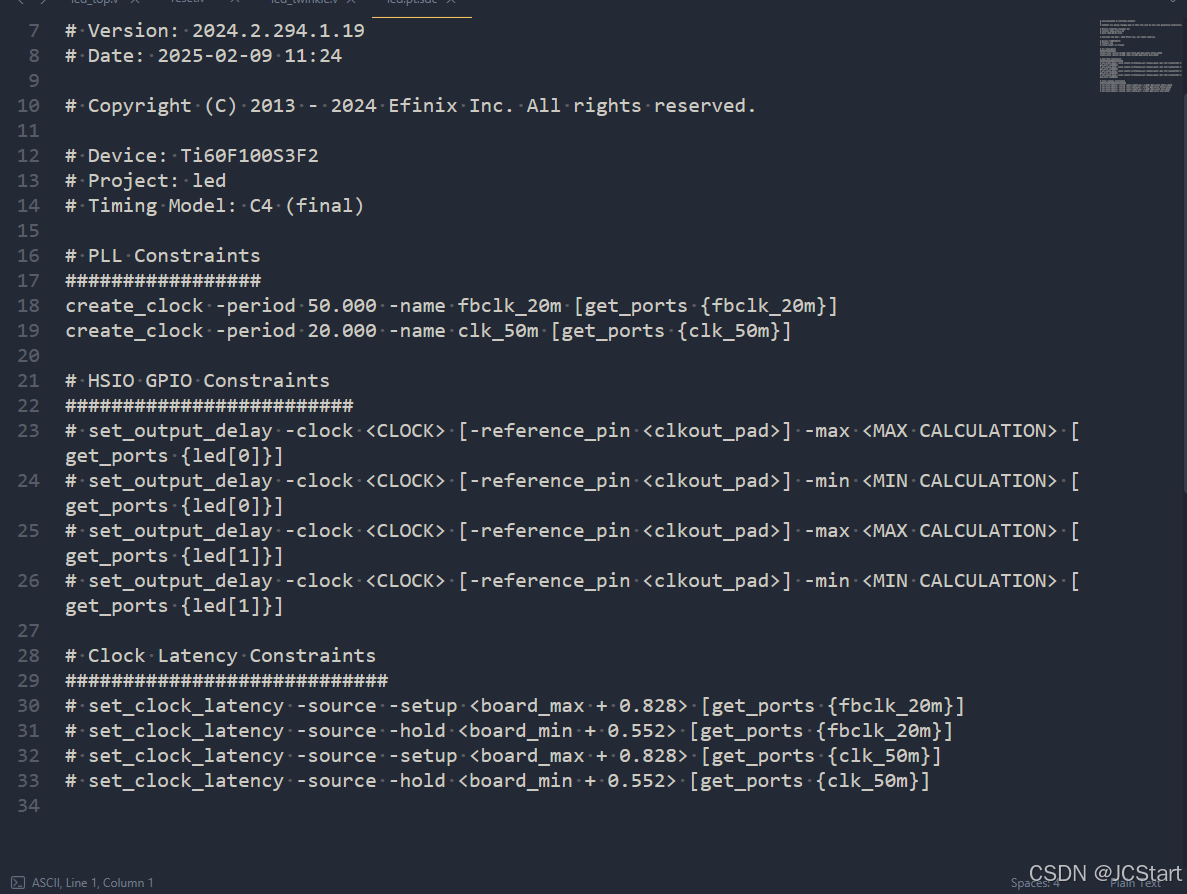

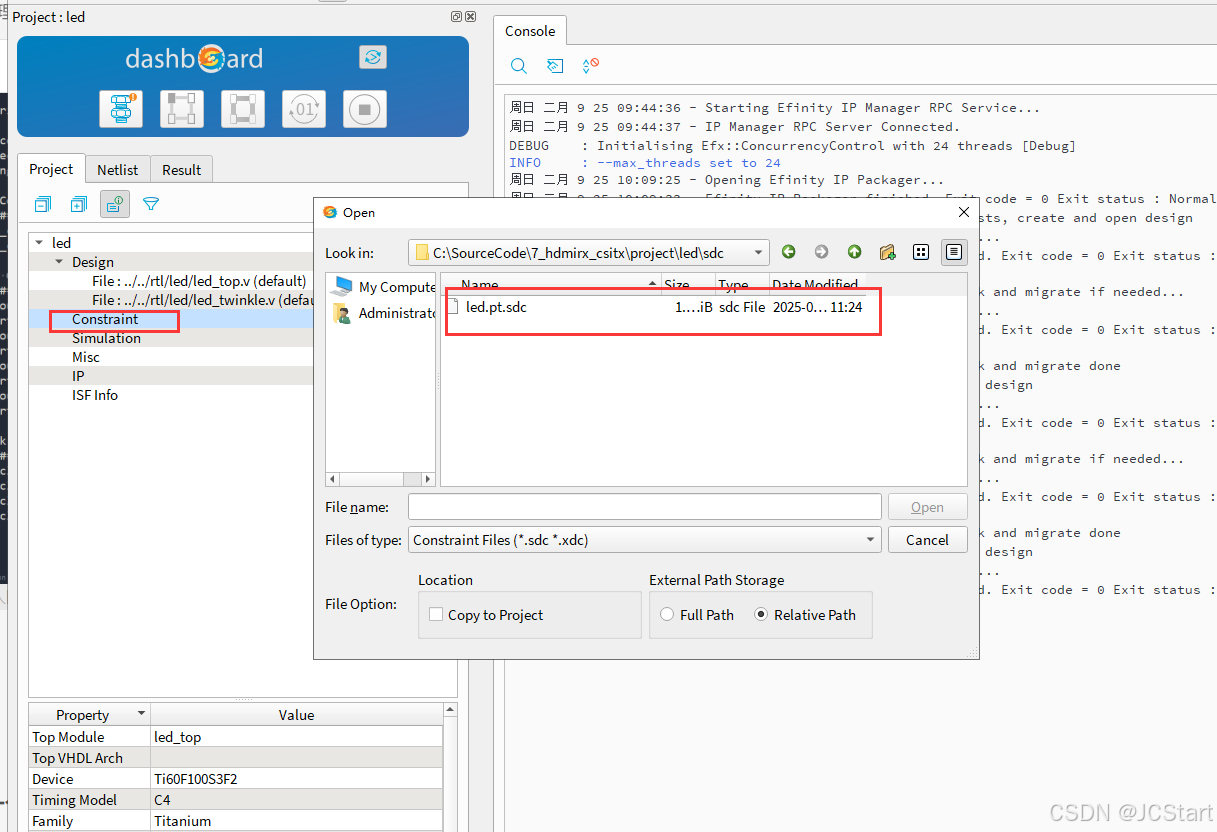

点击Result->led.pt.sdc

可以看到易灵思软件已经为我们编写好了时序约束,我们把这个文件添加进去

复制到工程目录下,创建文件夹sdc

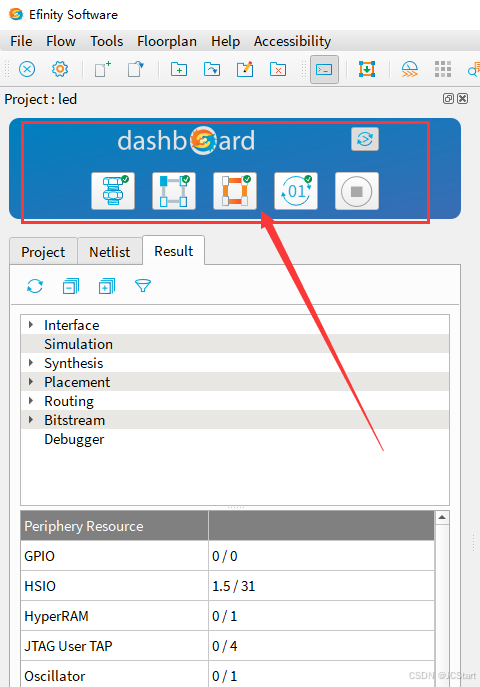

编译生成bitstream

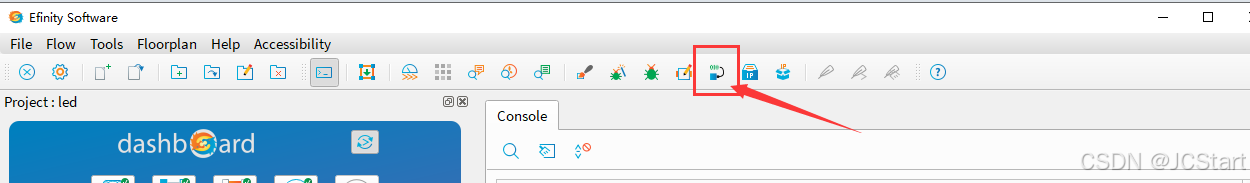

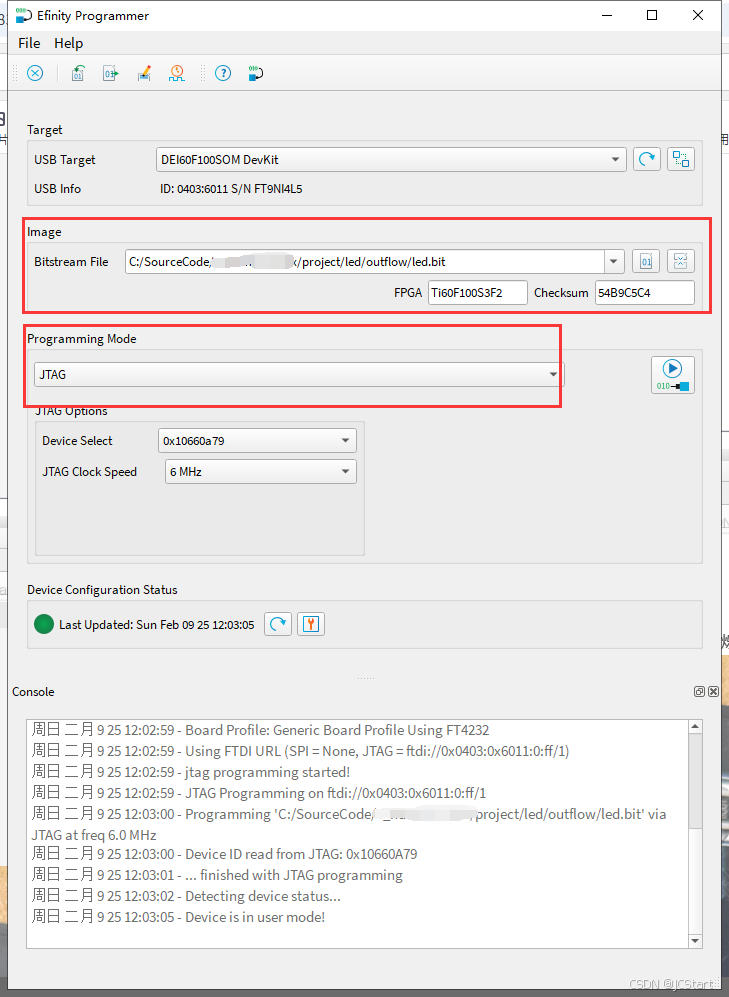

烧入bit文件

单击Open Programmer

选择bit文件和JTAG模式

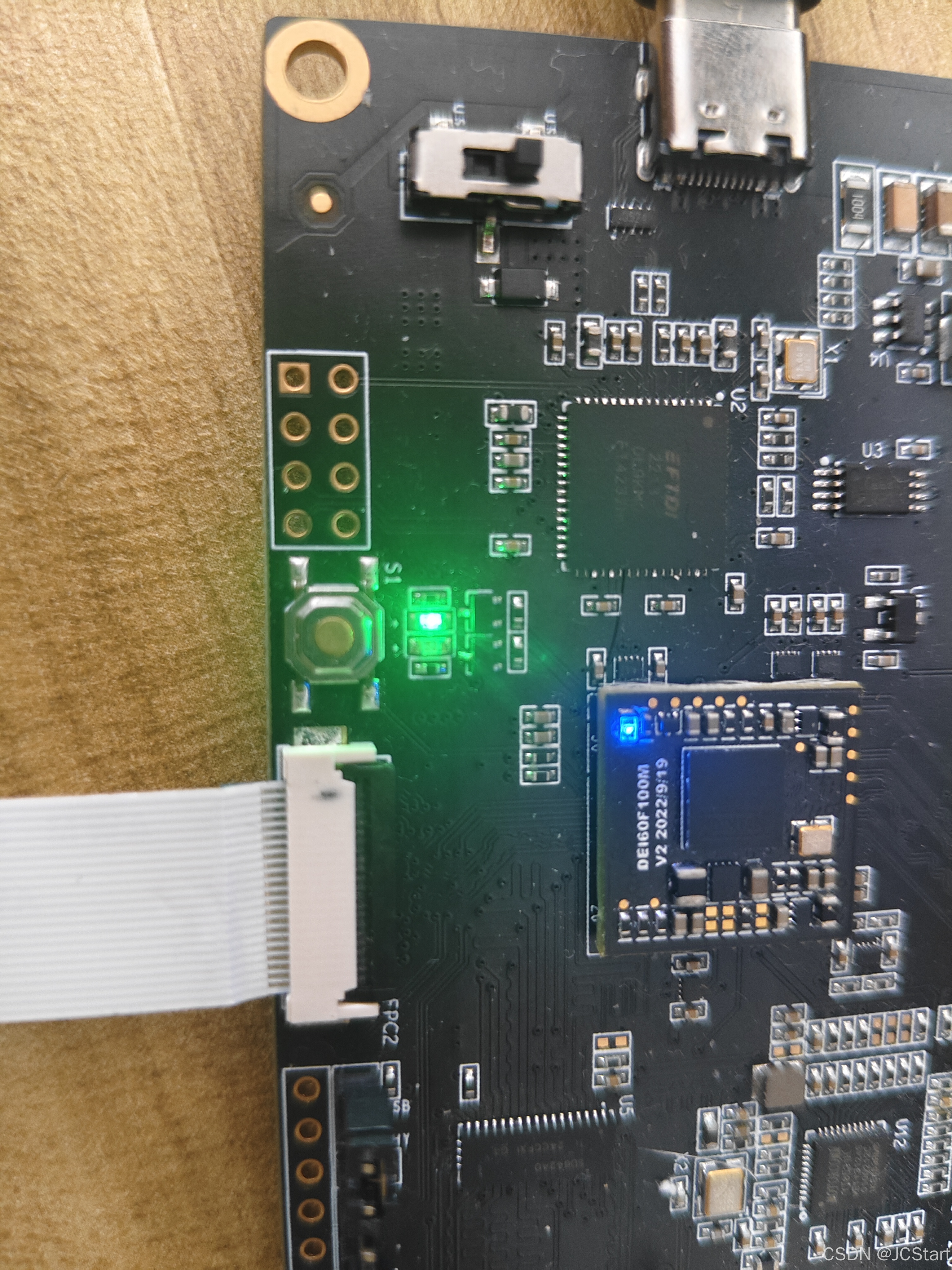

实验现象

此时我们可以看到位于底板上的两个 LED 呈现流水的效果,即两个 LED 灯在不断地交替闪烁,

实验总结

本章的内容主要是通过一个简单的“点灯”的例程,将 易灵思FPGA 开发的完整流程走一遍,

主要是学习 易灵思FPGA 规范的开发流程与开发软件的熟练操作,为后续 易灵思FPGA的开发打下坚实基础。

此外要深入理解易灵思的软件架构,采用的把逻辑资源和硬核资源分开的架构,代码部分只针对逻辑资源,也就是我们这里提到的Core,而IO及其他硬核部分的配置在interfaceDesigner工具中。下图是interface与Core的关系,它们之间通过被称作Siganl Interface的连线资源实现互联。

简单点就是 FPGA去驱动各类GPIO,LVDS MIPI JTAG外设,就像是51单片机去驱动定时器等外设一样。