STM32-外设引脚复用机制全解析_stm32引脚复用

一、外设复用的硬件基石 —— 复用器架构

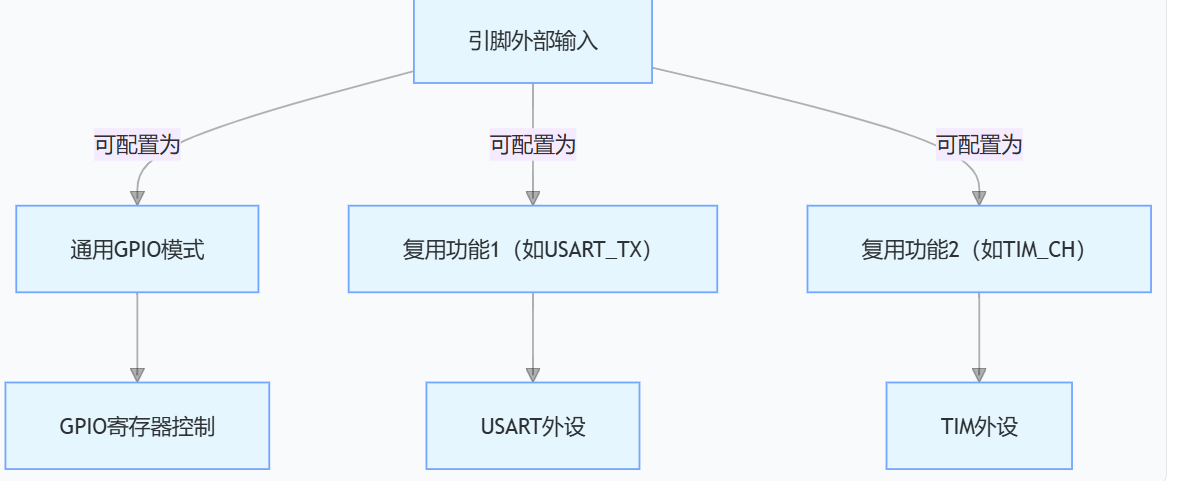

(一)引脚功能的 “多路选择” 本质

STM32 的 GPIO 引脚内部集成复用器(Multiplexer),可视为一个多输入选择开关,其核心结构:

- 物理层:每个引脚通过模拟开关矩阵连接到不同外设模块,开关状态由寄存器配置决定。

- 电气层:复用功能下,引脚的驱动能力、电平标准由所连接的外设决定(如 USART 的 TX 引脚需满足 RS232 电平时序)。

(二)复用功能的编码规则 ——AFx 映射

STM32 定义16 组复用功能(AF0-AF15),每组对应特定外设,编码规则:

- 寄存器实现:

GPIOx_AFRL(控制引脚 0-7)和GPIOx_AFRH(控制引脚 8-15),每个引脚占4 个 bit,用于存储 AFx 编码。

(三)冲突避免机制 —— 时钟与寄存器互锁

外设复用需满足时钟使能 + 寄存器配置双重条件:

- 时钟门控:未使能时钟的外设,即使引脚配置为其复用功能,也无法驱动引脚(如 USART1 时钟未开时,PA9 始终为普通 GPIO)。

- 寄存器独占:

AFRL/AFRH寄存器的每个引脚位域,同一时间只能配置一个 AFx 值,避免硬件冲突。

二、外设复用的完整配置流程(USART1 为例)

(一)步骤 1:时钟使能的三级联动

// 1. GPIO端口时钟(PA9/PA10所在的GPIOA)RCC->APB2ENR |= RCC_APB2ENR_IOPAEN; // 2. 外设时钟(USART1)RCC->APB2ENR |= RCC_APB2ENR_USART1EN; // 3. 复用功能时钟(AFIO,重映射时必开,基础复用可选)RCC->APB2ENR |= RCC_APB2ENR_AFIOEN;

- 原理:GPIO 时钟控制引脚硬件供电,外设时钟激活功能模块,AFIO 时钟用于重映射配置。

(二)步骤 2:引脚模式的精准配置

// PA9配置为复用推挽输出(USART1_TX)GPIOA->MODER &= ~(0x03 <MODER |= (0x02 <OTYPER &= ~(1 <OSPEEDR |= (0x03 <PUPDR |= (0x01 <MODER &= ~(0x03 <MODER |= (0x02 <PUPDR &= ~(0x03 << 20); // 浮空输入(0b00=浮空)

- 关键寄存器:

MODER:选择复用模式(0b10)而非通用 GPIO(0b00/0b01/0b11)。OTYPER:推挽输出适合主动驱动电平(如 USART_TX),开漏需外部上拉。

(三)步骤 3:AFx 映射的位操作

// PA9属于引脚9,对应AFRH寄存器的第1个半字(索引1,每个半字4bit)// USART1_TX对应AF7(编码0b0111)GPIOA->AFRH |= (0x07 << ( (9 - 8) * 4 ));

- 计算逻辑:引脚编号

n(0-15),若n<8则操作AFRL的n*4位,否则操作AFRH的(n-8)*4位。

(四)步骤 4:外设功能的最终激活

USART1->BRR = 0x341; // 波特率配置(72MHz→9600bps)USART1->CR1 |= USART_CR1_UE; // 使能USART1模块USART1->CR1 |= USART_CR1_TE | USART_CR1_RE; // 使能收发

- 验证方法:通过

USART1->SR寄存器的TXE位,检查发送是否使能。

三、深度案例:定时器 PWM 复用(TIM1_CH1 控制 LED)

(一)硬件特殊点 —— 高级定时器的主输出使能

// TIM1属于高级定时器,需额外使能主输出TIM_CtrlPWMOutputs(TIM1, ENABLE);

- 原因:高级定时器(TIM1/TIM8)的 PWM 输出受

MOE位(主输出使能)控制,防止误触发大功率外设(如电机驱动)。

(二)动态占空比调节的底层逻辑

// 改变CCR1寄存器值调整占空比TIM_SetCompare1(TIM1, 500); // 占空比=500/1000=50%

- 寄存器关联:

TIMx_CCR1的值与TIMx_ARR(自动重装载值)的比值决定占空比,硬件实时比较CNT与CCR的值输出 PWM。

(三)常见问题 —— 无 PWM 输出的排查路径

- 时钟链检查:

RCC_APB2ENR中 TIM1、GPIOA、AFIO 时钟是否使能。 - 模式配置:

GPIO_Mode_AF_PP是否正确设置,MODER寄存器值是否为 0b10。 - 定时器状态:

TIMx_CR1的CEN位是否置 1(定时器使能),TIMx_CCMR1的OC1M位是否为 PWM 模式(0b110 或 0b111)。

四、高级应用:重映射的硬件机制与实践

(一)重映射的本质 ——AFIO 寄存器的地址重定向

// USART1部分重映射到PB6/PB7AFIO->MAPR |= AFIO_MAPR_USART1_REMAP;

- 硬件实现:AFIO 模块通过

MAPR寄存器修改复用器的连接关系,将 USART1 的信号路径从 PA9/PA10 切换到 PB6/PB7。

(二)重映射的分类与资源占用

- 注意:重映射会占用 AFIO 的时钟资源,且部分重映射可能导致原引脚功能冲突(如 PA9 仍可作为 GPIO,但不能同时作为 USART1_TX)。

五、调试与优化的实战技巧

(一)寄存器级调试方法

- 直接读取验证:

// 检查AFRH配置是否正确uint32_t afrh = GPIOA->AFRH;// 检查USART1时钟是否使能uint32_t apb2enr = RCC->APB2ENR; - 位域解析工具:使用在线位域解析器(如STM32 Register Tool),输入寄存器值自动解析配置。

(二)示波器 / 逻辑分析仪的关键测量点

- 引脚电平:测量 PA9 是否有预期波形(如 USART 的 115200bps 信号应包含起始位、数据位、停止位)。

- 外设寄存器:通过 SWD 读取

USART1->DR(数据寄存器)、TIM1->CCR1(比较寄存器)的值,确认数据传输与 PWM 配置。

(三)性能优化 —— 直接寄存器操作

// 替代库函数的直接寄存器配置(更快更省空间)#define GPIOA_AFRH_USART1_TX (0x07 <AFRH = GPIOA_AFRH_USART1_TX;

- 优势:减少库函数的调用开销,适合对时序要求严格的场景(如高频 SPI 通信)。

六、外设复用的工程经验总结

- 引脚冲突处理:当多个外设复用同一引脚时,通过

RCC时钟使能控制激活的外设(如调试阶段仅使能 USART1,量产时切换为 TIM1)。 - 跨系列兼容性:不同 STM32 系列(如 F1/F4/H7)的 AFx 映射可能不同,需严格参考数据手册(RM)中的复用功能表。

- 电源管理:复用为低功耗外设(如 I2C)时,需配置引脚为开漏模式并使能上拉,降低待机电流。

通过掌握复用器硬件架构、AFx 编码规则、重映射机制,结合寄存器级调试与性能优化技巧,可高效解决 STM32 外设复用的各类问题,实现引脚资源的最大化利用。核心是理解 “硬件连接由寄存器配置决定,功能激活依赖时钟使能” 的本质,让每一个引脚都能精准服务于目标外设。