FPGA PLL深入实战:设计与锁相程序实现

本文还有配套的精品资源,点击获取

简介:本文实战训练聚焦于FPGA中的PLL(Phase-Locked Loop)实现与应用,详细讲解了PLL的基本原理以及在FPGA中如何通过IP核实现多时钟输出的锁相程序。介绍了PLL的内部结构、设计步骤、参数配置和硬件实现,通过具体案例教授如何配置Xilinx Vivado中的PLL IP核,并利用Verilog或VHDL代码进行集成,最后通过硬件工具验证时钟输出的正确性。掌握这些技能对于FPGA开发人员和硬件设计工程师来说至关重要。

1. FPGA与PLL基础

在数字系统设计中,FPGA(现场可编程门阵列)提供了一种高度灵活和可定制的硬件解决方案。利用其内部的可编程逻辑块和可配置的互连,FPGA可以实现各种复杂的功能。然而,为了实现高速的数据处理和精确的时序要求,FPGA设计往往需要集成精确的时钟管理解决方案。

1.1 FPGA的基础知识

FPGA是一种可以通过编程来配置的半导体设备,它包含数以千计的可编程逻辑单元,以及一个灵活的互连网络。FPGA可以根据设计需求来配置其逻辑单元和互连,以实现用户特定的功能。其灵活性和可重复编程特性使其在原型设计、产品开发和批量生产中都具有广泛的应用前景。

在深入探讨FPGA之前,有必要了解其核心构成要素:可编程逻辑块、可配置输入/输出单元以及可编程互连资源。这些元素共同工作,为FPGA提供了实现数字逻辑所需的硬件结构。

随着技术的发展,FPGA的性能和集成度不断提升,使得它们能够支持更复杂的设计,并且运行速度更快。FPGA中的时钟管理模块变得日益重要,因为它直接关系到整个系统的时序精度和性能表现。这正是PLL(Phase-Locked Loop,锁相环)发挥作用的地方。

1.2 PLL的作用与重要性

PLL是一种电子电路,用于产生与输入信号频率相锁定的输出信号。PLL在FPGA中扮演着至关重要的角色,因为它能够生成精确的时钟信号,供FPGA内部逻辑使用,或提供给外部设备。它能够稳定时钟频率、降低时钟偏差,并通过提供倍频、分频功能来适应不同的设计要求。

通过PLL,FPGA得以实现更复杂的时序控制,优化系统性能,并解决时钟同步的问题。在本文中,我们将探讨PLL的原理、在FPGA中的应用,并深入了解如何在现代FPGA开发环境中有效地配置和优化PLL,以便为我们的设计提供最佳的时钟管理解决方案。接下来的章节将更详细地介绍PLL的原理,以及如何在Vivado等设计环境中应用PLL IP核。

2. PLL原理与功能介绍

2.1 频率合成技术简介

2.1.1 频率合成技术的发展历程

频率合成技术自20世纪中叶以来,一直是通信和电子系统发展的驱动力。早期的频率合成技术依赖于机械和电子的调谐,例如可变电容器和振荡器。这些方法的稳定性和精确性有限,难以满足现代电子系统对频率稳定性的高要求。随着电子技术的进步,逐步发展到直接频率合成(Direct Frequency Synthesis,DFS),它使用振荡器、混频器、倍频器和分频器等电子元件实现精确的频率输出。后来,又出现了间接频率合成技术,也称为锁相环频率合成技术(Phase-Locked Loop Frequency Synthesis,PLL),它能够产生更精确、更稳定的频率输出,并且迅速成为了频率合成技术的主流。

2.1.2 频率合成技术的基本原理

频率合成技术的核心目标是根据需要生成稳定的频率信号。基本原理是通过一个或多个参考信号,使用一系列电子组件(如混频器、倍频器、分频器和滤波器)对原始信号进行处理,从而产生新的频率信号。在直接频率合成技术中,利用预设的频率组合直接产生所需频率;而在间接频率合成技术中,则依赖于反馈控制机制——锁相环(PLL)来调整本地振荡器的输出,以锁定到参考频率。PLL通过比较输入信号与输出信号的相位差异,自动调整振荡器的频率,直到二者同步。

2.2 锁相环(PLL)的工作原理

2.2.1 锁相环的基本结构

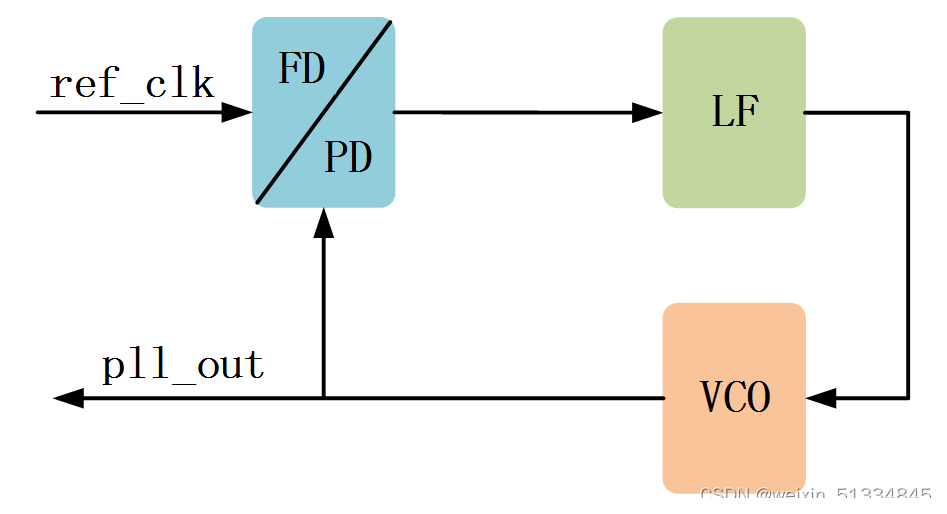

锁相环由几个关键组件组成,通常包括鉴相器(Phase Detector)、环路滤波器(Loop Filter)、压控振荡器(Voltage Controlled Oscillator, VCO)、分频器(Divider)等。其中鉴相器负责比较输入参考信号和反馈信号的相位差异;环路滤波器用来滤除鉴相器输出中的噪声和高频分量,以平滑控制电压;VCO输出频率随控制电压变化的信号;分频器则用来调整VCO输出信号的频率,使其与输入信号达到一定的比例关系。

2.2.2 锁相环的工作过程与关键组件

锁相环的工作过程可以分为三个主要步骤:捕获(Acquisition)、跟踪(Tracking)和锁定(Locking)。开始时,环路滤波器输出的控制电压会导致VCO的输出频率偏离所需频率,此时鉴相器输出的误差信号通过环路滤波器来调整VCO,使之逐渐接近输入信号的频率。一旦频率达到足够接近的程度,环路将进入跟踪阶段,此时VCO频率会受到连续的微调,以确保锁定。锁定阶段是环路稳定运行的状态,在此阶段,VCO输出的频率与输入参考频率的相位差异保持最小。

2.3 锁相环的主要功能与应用领域

2.3.1 锁相环在FPGA中的典型应用

在FPGA中,PLL通常被用来生成时钟信号,实现时钟管理功能。例如,可以利用PLL进行时钟分频、时钟倍频、时钟移相或去抖动等操作。FPGA内部集成的PLL模块,通过软件配置,可以灵活地满足不同应用场景对时钟信号的特殊要求。这对于设计高性能的数据处理系统、通信设备和测试设备是非常重要的。

2.3.2 锁相环在其他领域的应用案例分析

除了在FPGA中的应用之外,PLL在无线通信、音频处理、视频系统、数据通信等地方也有广泛应用。例如,在无线通信系统中,PLL用于生成载波信号和实现频率合成;在视频系统中,PLL可以用于行扫描频率的同步;在数据通信中,PLL确保数据的时钟域同步以及信号的正确恢复。不同的应用场合对PLL的性能参数有不同的要求,如频率稳定性、相位噪声性能、锁定时间等。

以上就是本章节所涵盖的PLL原理与功能介绍的主要内容。为了更深入地理解锁相环的工作原理和应用,我们将继续在接下来的小节中,详细介绍PLL在不同应用场景的具体实现方法和优化策略。

3. PLL IP核的应用与配置

在FPGA设计中,PLL IP核扮演着至关重要的角色,它能够通过内部反馈回路实现频率合成、时钟相移和时钟分频等功能。在本章节中,我们将深入探讨PLL IP核的应用与配置,包括其概述、参数配置和集成外部时钟源的策略与方法。

3.1 PLL IP核概述

3.1.1 IP核的定义与优势

IP核(Intellectual Property Core)是一种预先设计好的、具有特定功能的集成电路模块,可以在不同的设计中复用。IP核的优势在于它可以节省设计时间和成本,同时保证设计的质量和性能。在FPGA设计中,PLL IP核能够提供稳定的时钟信号,是提高系统性能的关键组件。

3.1.2 PLL IP核的分类与选择标准

PLL IP核可以根据其功能和复杂度被分类。基本的分类包括简单频率合成器、复杂时钟管理器等。选择合适的PLL IP核时,设计者应该考虑以下标准:

- 性能需求 :根据设计对频率范围、相位噪声、抖动等参数的要求。

- 资源消耗 :评估IP核对FPGA内部资源的占用情况。

- 兼容性 :确保所选IP核与FPGA型号兼容。

- 可配置性 :IP核是否支持灵活的配置,以适应不同的应用需求。

3.2 PLL IP核的参数配置

3.2.1 输入输出频率设置

PLL IP核的首要任务是提供正确的时钟频率。输入和输出频率的设置应满足设计要求。对于输入频率,通常取决于外部时钟源,而输出频率则根据系统需求进行设置。例如,如果需要将50MHz的输入频率倍频至100MHz,需要在IP核中进行相应的配置。

// 代码示例:Vivado PLL IP核配置clk_wiz_0: clk_wiz generic map ( CLKOUT1_REQUESTED_OUT_FREQ => 100.0, -- 设置输出频率为100MHz CLKOUT2_REQUESTED_OUT_FREQ => 50.0, -- 设置输出频率为50MHz,可选输出 CLKIN1_REQUESTED_IN_FREQ => 50.0, -- 设置输入频率为50MHz // 其他参数... ) port map ( // 端口映射... );3.2.2 相位噪声与抖动优化

相位噪声和抖动是评估时钟质量的重要指标。为了优化这些参数,需要合理设置PLL IP核中的滤波器带宽和环路带宽参数。

// 代码示例:优化相位噪声和抖动clk_wiz_0: clk_wiz generic map ( CLKFBOUT_MULT_F => 20.000, -- 反馈乘数,影响环路带宽 CLKOUT0_DIVIDE_F => 40.000, -- 输出分频器,影响滤波器带宽 // 其他参数... ) port map ( // 端口映射... );3.2.3 电源与温度管理参数配置

电源和温度对PLL的性能也有显著影响。为了确保在不同的工作条件下都能维持稳定的性能,应该在配置中考虑到电源噪声抑制和温度补偿。

// 代码示例:配置电源与温度管理参数clk_wiz_0: clk_wiz generic map ( BANDWIDTH => \"OPTIMIZED\", -- 优化带宽以减少电源噪声影响 REF_JITTER1 => 0.100, -- 输入参考抖动 // 其他参数... ) port map ( // 端口映射... );3.3 集成外部时钟源

3.3.1 外部时钟源的选择与接法

选择合适的外部时钟源对于整个系统来说至关重要。通常,外部时钟源可以是一个晶体振荡器、一个电压控制振荡器或者一个频率合成器。在接法上,需要考虑驱动能力、阻抗匹配等因素。

3.3.2 集成外部时钟源的设计考虑

集成外部时钟源时,需要确保时钟信号的质量不会因为线路损耗而降低。设计者应考虑使用差分信号传输以提高抗干扰能力,并使用适当的终端匹配技术以减少信号反射。

graph LRA[时钟源] --> B[差分驱动]B --> C[传输线]C --> D[终端匹配]D --> E[接收端]总结本章节的内容,我们可以看到PLL IP核在FPGA设计中的重要性。通过精心配置,可以充分利用其提供的稳定时钟信号。同时,选择并集成合适的外部时钟源对于保持系统时钟质量至关重要。下一章节将继续深入探讨在Vivado环境下的PLL IP核设置以及其在HDL代码中的应用和集成。

4. Vivado环境下的PLL IP核设置

Vivado作为Xilinx公司推出的先进FPGA设计套件,为设计师们提供了一个全面的设计环境,包括逻辑设计、综合、实现和验证等环节。本章节将深入探讨如何在Vivado环境下进行PLL IP核的设置,涵盖了从PLL IP核的生成、配置、实例化到仿真验证的全过程。

4.1 Vivado设计套件简介

4.1.1 Vivado设计流程概述

Vivado设计流程是一个高度集成和优化的流程,它将设计的各个阶段紧密地整合在一起,从设计输入到最终硬件实现。其核心特性包括模块化设计、高层次综合、实时逻辑优化、先进的时序分析和布局布线。设计流程主要分为几个步骤:设计输入、综合、实现、生成比特流以及硬件验证。

Vivado的模块化设计方法支持使用高层次的抽象化设计输入,比如使用HDL代码或者IP核。综合阶段将HDL代码或高级抽象转换成门级网表。实现阶段则负责将门级网表映射到目标FPGA架构上,进行布局和布线。最后,通过生成比特流来完成硬件配置文件的创建,并在实际硬件上进行验证。

4.1.2 Vivado与传统工具的对比分析

Vivado与Xilinx以前的ISE工具相比,提供了更为强大的设计处理能力。特别是在处理大型设计时,Vivado的性能提升尤为显著。它的设计流程更加灵活,优化算法更为先进,支持更多的设计优化层次,如时序优化、功耗优化和资源优化等。

Vivado引入了基于项目的设计管理和多核处理支持,加快了设计的迭代速度。此外,Vivado还加强了对HDL代码质量的分析能力,通过集成的代码覆盖率工具可以更好地对设计进行验证和调试。这些改进使得Vivado成为大规模复杂设计项目的理想选择。

4.2 Vivado中PLL IP核的生成与配置

4.2.1 创建与配置PLL IP核的步骤

在Vivado中生成和配置PLL IP核的步骤如下:

-

打开Vivado并创建项目 :首先启动Vivado并创建一个新的设计项目,输入项目名称并选择目标FPGA型号。

-

添加源文件或IP核 :在项目导航器中,右键点击”IP Catalog”并选择”Add IP”,在弹出的IP Catalog窗口中找到并双击”Clocking Wizard”来添加PLL IP核。

-

打开IP定制器 :添加PLL IP核后,双击该IP核在项目导航器中的条目来打开IP定制器。

-

进行PLL配置 :在IP定制器中,根据设计需求对PLL进行配置。可以通过修改预定义的参数来设置输出频率、相位偏移、占空比等属性。

-

生成输出产品 :配置完成后,点击”Generate”按钮生成IP核,Vivado会自动添加必要的约束文件,并将生成的IP核添加到项目中。

-

添加IP核到顶层模块 :将生成的PLL IP核通过拖拽的方式添加到顶层模块中。

4.2.2 IP核参数界面解析与高级设置

在IP核参数界面,可进行的高级设置包括:

-

时钟输入设置 :设置PLL的输入时钟频率,输入时钟源类型(差分或单端),以及输入时钟的引脚分配。

-

输出时钟设置 :定义输出时钟的数量,每个输出时钟的频率以及相位偏移。可以设置为差分输出或单端输出。

-

反馈路径设置 :根据需要选择反馈路径类型,可以是内部反馈或者外部反馈。

-

相位噪声与抖动优化 :可选择不同的抖动过滤模式,根据需要选择是否优化低频或高频相位噪声。

-

高级参数设置 :包括输出时钟去偏移功能,动态重配置功能以及锁定检测信号。

4.3 Vivado中PLL IP核的实例化与仿真

4.3.1 IP核的实例化过程

实例化过程是指在HDL代码中将PLL IP核嵌入到设计中的步骤。首先在顶层模块中引用PLL IP核生成的输出文件,包括PLL的模块封装文件和约束文件。然后在模块内部实例化PLL,并根据设计需求连接输入输出信号。需要注意的是,实例化时要确保时钟信号的正确性和同步性。

4.3.2 IP核仿真验证的方法与工具

仿真验证是用来检验PLL IP核功能正确性的关键步骤。在Vivado中,可以通过集成的仿真工具如Vivado Simulator进行仿真测试。

在进行仿真时,需要:

-

编写测试平台代码 :创建一个测试平台来模拟时钟输入和观察输出时钟,检测输出时钟是否符合预期的频率和相位偏移。

-

运行仿真 :使用仿真工具执行测试平台,观察仿真波形以确定输出时钟行为是否正确。

-

分析结果 :对仿真结果进行分析,检查关键信号是否按预期变化,是否存在时序问题或不合理的时钟边沿。

以下是一个示例代码块,演示如何在测试平台中实例化PLL IP核,并对其进行基本的仿真操作。

// 测试平台代码示例module tb_pll_example(); // 定义测试信号 reg clk_in; wire clk_out; // 实例化PLL IP核 clk_wiz_0 clk_wiz_inst ( .clk_in1(clk_in), // 输入时钟信号 .clk_out1(clk_out) // 输出时钟信号 ); // 时钟信号初始化和驱动 initial begin clk_in = 0; forever #5 clk_in = ~clk_in; // 生成100MHz的时钟信号 end // 观察输出信号 initial begin #1000; // 等待一段时间后结束仿真 $finish; endendmodule 在上述代码中,我们创建了一个测试平台,并实例化了一个名为 clk_wiz_0 的PLL IP核。 clk_in 作为输入信号,在 initial 块中被设置为一个周期为10ns的时钟。我们假设PLL配置为输出一个频率为100MHz的时钟信号。然后,我们观察输出时钟 clk_out 是否符合预期。这个简单的测试平台可以帮助我们快速验证PLL输出信号的基本功能。

5. HDL代码编写与集成

5.1 HDL编程基础

5.1.1 Verilog/VHDL语言特性介绍

在设计现代数字逻辑电路时,HDL(硬件描述语言)是不可或缺的工具。Verilog和VHDL是两种主流的HDL,它们用于描述电路的结构、行为和功能。Verilog语言易于掌握,语法简单,受到许多工程设计师的青睐。而VHDL作为一种更接近自然语言的描述方式,拥有更加严谨的数据类型和丰富的设计层次,常用于大型系统的描述。

Verilog 特点包括:

- 简单直观的语法。

- 强大的仿真能力。

- 支持模块化设计。

VHDL 特点包括:

- 严格的数据类型定义。

- 面向对象的设计方法。

- 支持更复杂的抽象层次。

5.1.2 代码风格与设计原则

编写HDL代码时,遵循一定的风格和设计原则可以提高代码的可读性和可维护性。以下是一些常见的HDL代码编写最佳实践:

- 保持代码简洁明了,避免复杂的嵌套结构。

- 使用模块化设计,将复杂问题分解为更小的、可管理的部分。

- 定义清晰的接口,使用端口声明以明确模块输入输出。

- 采用参数化设计,使模块能够适应不同的应用场景。

- 对于公共逻辑或数据路径,考虑使用宏和生成语句来提高代码复用性。

5.2 HDL代码中的PLL集成

5.2.1 编写PLL接口模块代码

PLL接口模块是将PLL IP核集成到HDL设计中的关键部分。在这一部分,我们需要定义PLL的输入输出端口以及内部信号,使得PLL IP核能与外部电路交互。

假设我们使用Verilog语言,一个简单的PLL接口模块可能包含如下部分:

module pll_interface ( input wire clk_in, // 输入时钟信号 input wire reset_n, // 异步复位信号,低电平有效 output wire clk_out, // 经PLL处理后的输出时钟信号 output wire locked // PLL锁定指示信号);// PLL IP核实例化// ...// 内部信号定义和处理// ...endmodule在实际的设计中,这将涉及到PLL的初始化参数配置和状态监控,以确保其正常工作。

5.2.2 HDL代码与PLL IP核的集成策略

集成PLL IP核到HDL设计中时,需要考虑以下集成策略:

- 实例化 :使用工具提供的IP核实例化方法将PLL模块加入到设计中。

- 配置 :根据应用需求设置PLL的参数,包括频率、相位偏移等。

- 接口对接 :确保PLL输出与下游电路的输入端口匹配,避免时序问题。

例如,在Vivado中,可以通过图形化界面配置PLL参数,并生成相应的HDL代码。之后,我们可以将生成的HDL代码嵌入到我们的设计中,完成整体设计的构建。

5.3 代码的测试与验证

5.3.1 单元测试与模块验证方法

代码的测试与验证是确保设计质量的关键步骤。单元测试用于验证每个独立模块的功能正确性。可以使用诸如ModelSim这样的仿真软件来进行单元测试。

单元测试通常包括:

- 测试PLL锁定功能。

- 验证输出时钟频率是否符合预期。

- 检查相位噪声和抖动是否在允许的范围内。

5.3.2 代码覆盖率分析与调试技巧

代码覆盖率分析用于度量测试充分性,它能够显示哪些代码段被执行了,哪些未被执行。在ModelSim或其他仿真环境中,可以利用覆盖率分析工具来提高代码测试的完备性。

调试时的技巧包括:

- 波形查看 :检查时钟信号以及其他关键信号的波形。

- 断点设置 :在仿真工具中设置断点,逐步执行代码,观察变量值的变化。

- 日志输出 :在代码中加入打印语句,输出关键变量的值,帮助定位问题。

通过综合运用这些测试和验证手段,可以确保HDL代码和PLL集成后能够稳定可靠地工作。

本文还有配套的精品资源,点击获取

简介:本文实战训练聚焦于FPGA中的PLL(Phase-Locked Loop)实现与应用,详细讲解了PLL的基本原理以及在FPGA中如何通过IP核实现多时钟输出的锁相程序。介绍了PLL的内部结构、设计步骤、参数配置和硬件实现,通过具体案例教授如何配置Xilinx Vivado中的PLL IP核,并利用Verilog或VHDL代码进行集成,最后通过硬件工具验证时钟输出的正确性。掌握这些技能对于FPGA开发人员和硬件设计工程师来说至关重要。

本文还有配套的精品资源,点击获取