vivado DDS ip核的使用_dds compiler ip核

有些时候,为了方便,我们就直接使用dds的ip核来生成波形,其配置还是有些需要注意的点。

以下是建立一个dds ip核的过程,并且使用testbench观察波形仿真。

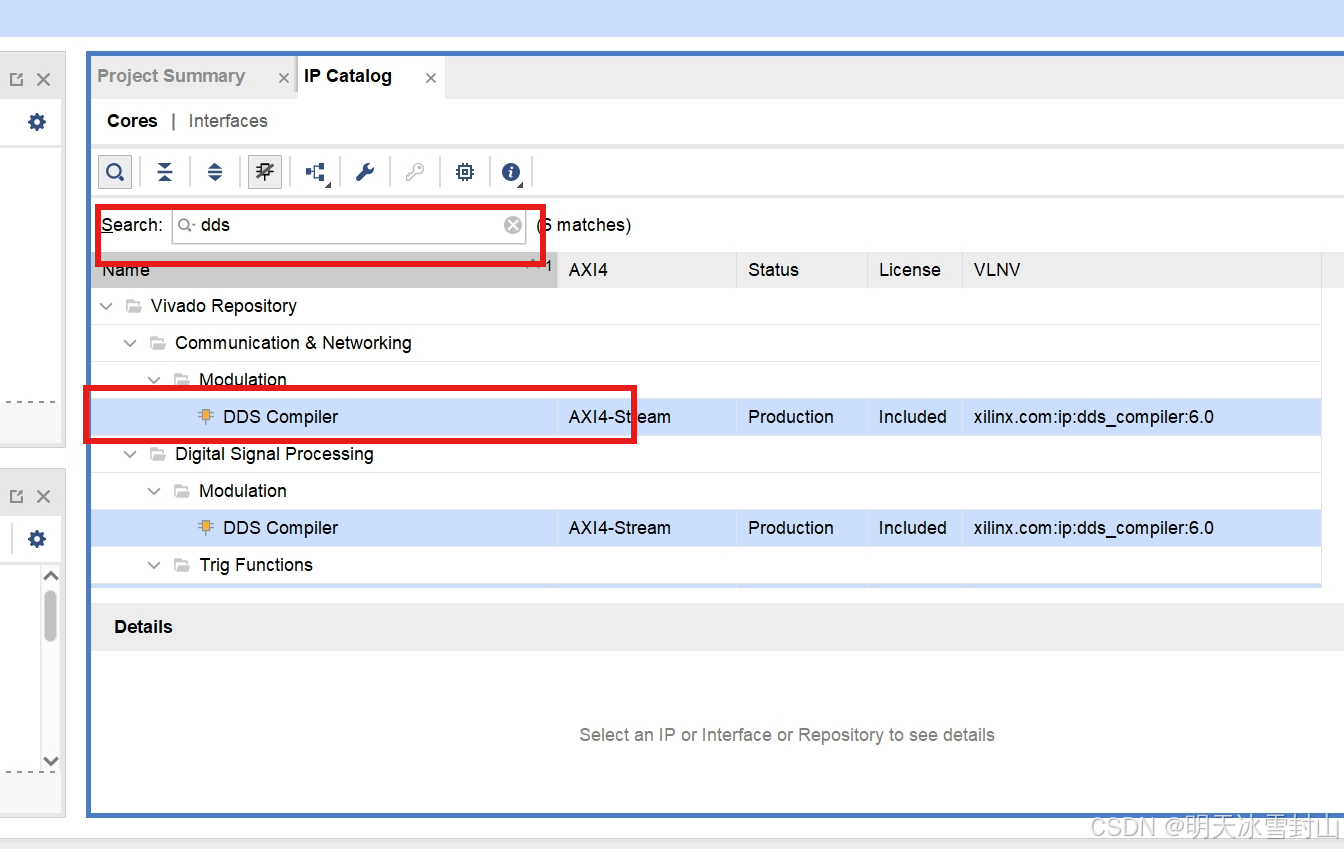

先在IP Catalog中找到DDS Compiler的IP核

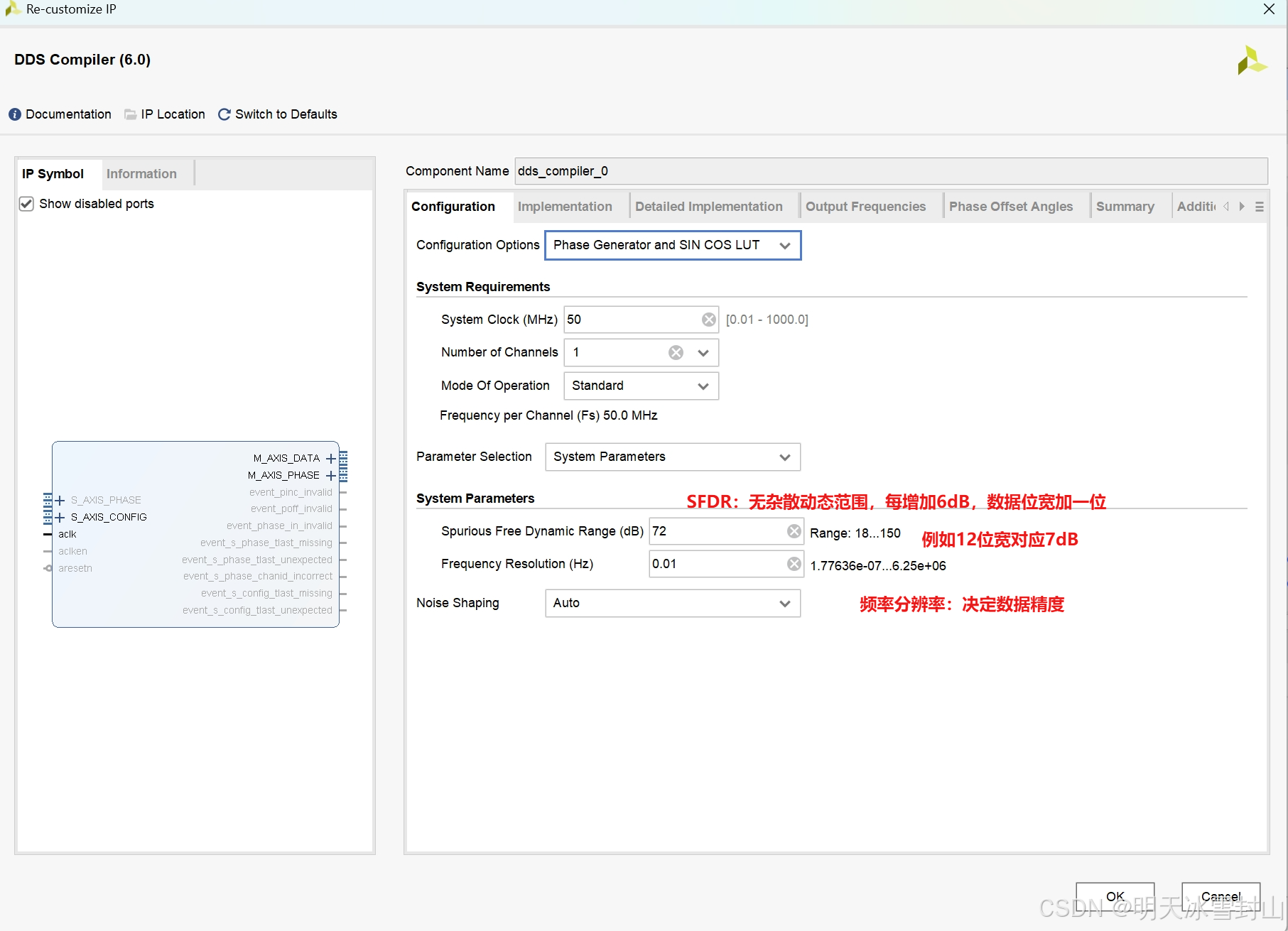

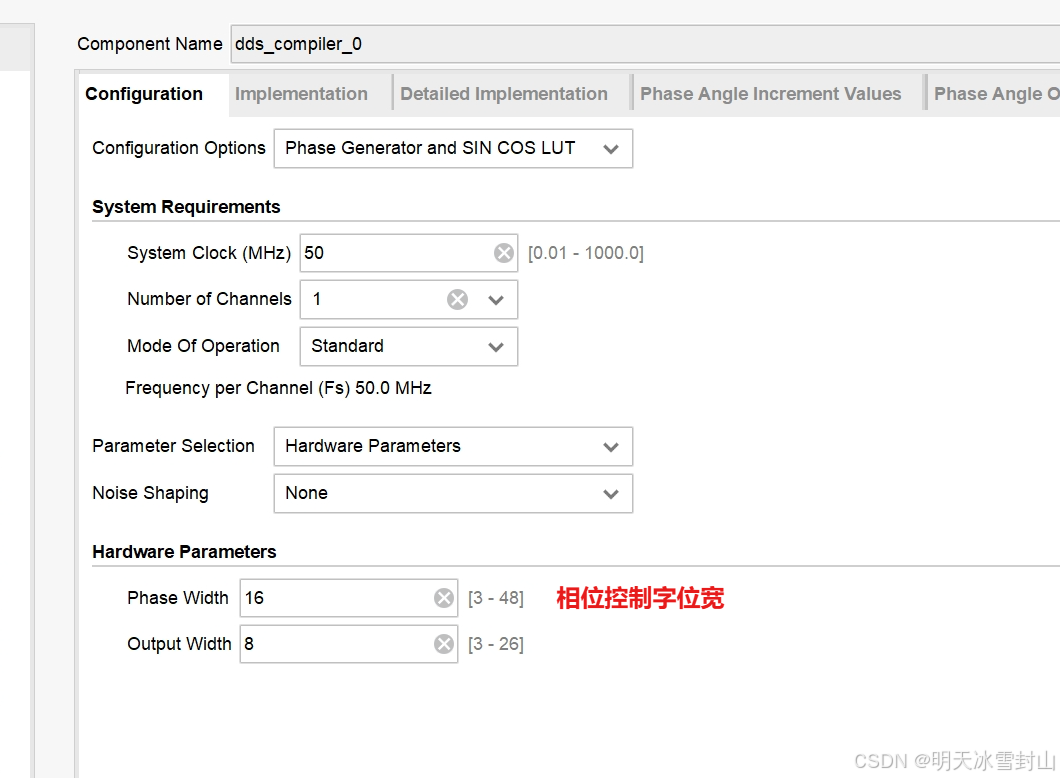

Configuration

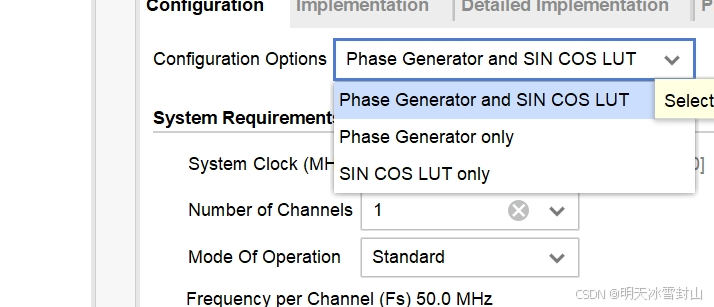

Phase Generator and SIN COS LUT :IP核产生sin、cos和相位数据

Phase Generator only :只输出相位

SIN COS LUT only :用来计算三角函数值,只输出sin、cos数据,需要外部不断输入累加的相位

所以,一般还是用第一个。

Noise Shaping:一般选None,这个Taylor Series Corrected(泰勒技术纠正)可以用来提高精度,我还没用过

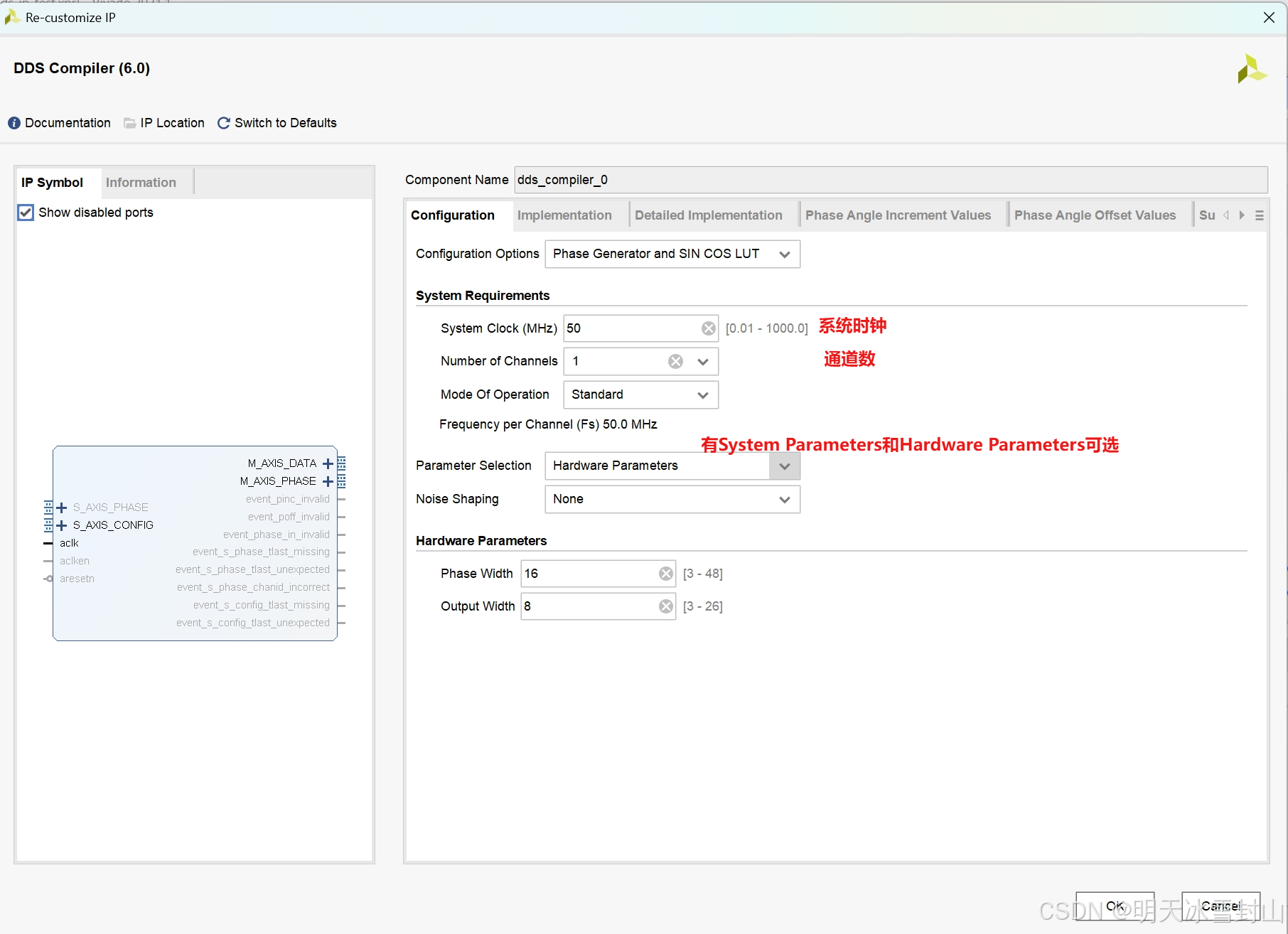

选择Hardware Parameters时

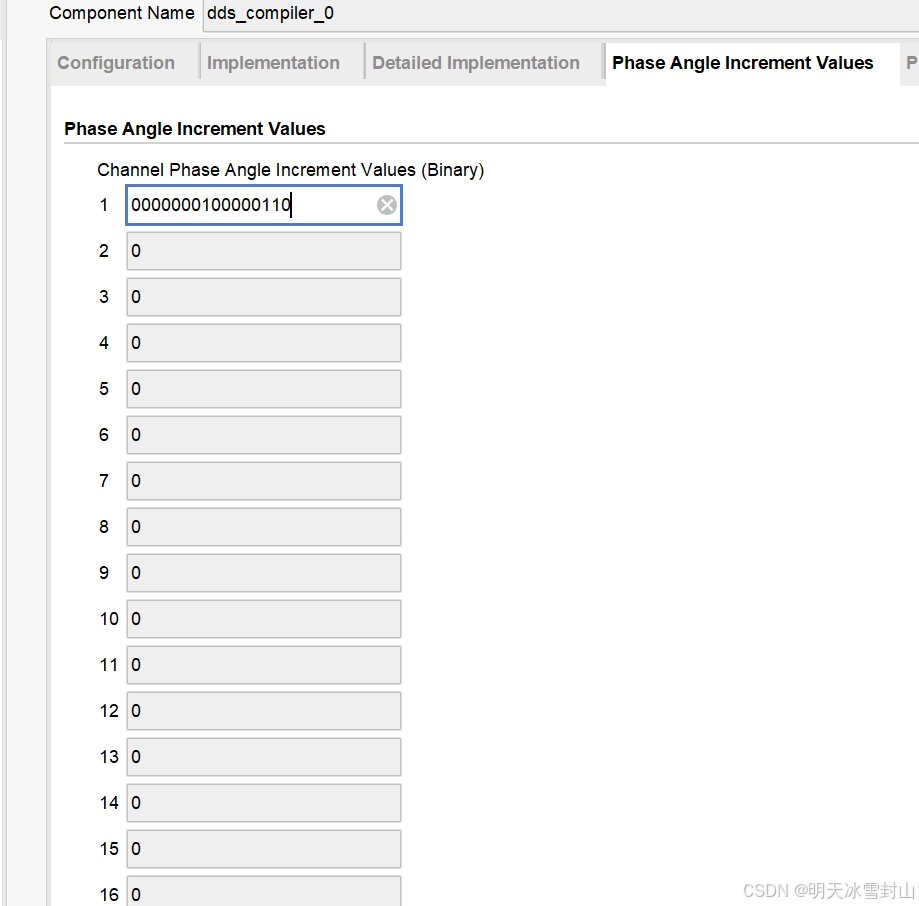

此时要再这里或者程序中输入频率控制字(注意这里是二进制)

K = (fout*2^N)/fclk

如果选的是System Parameters,可以在IP核里直接输入频率