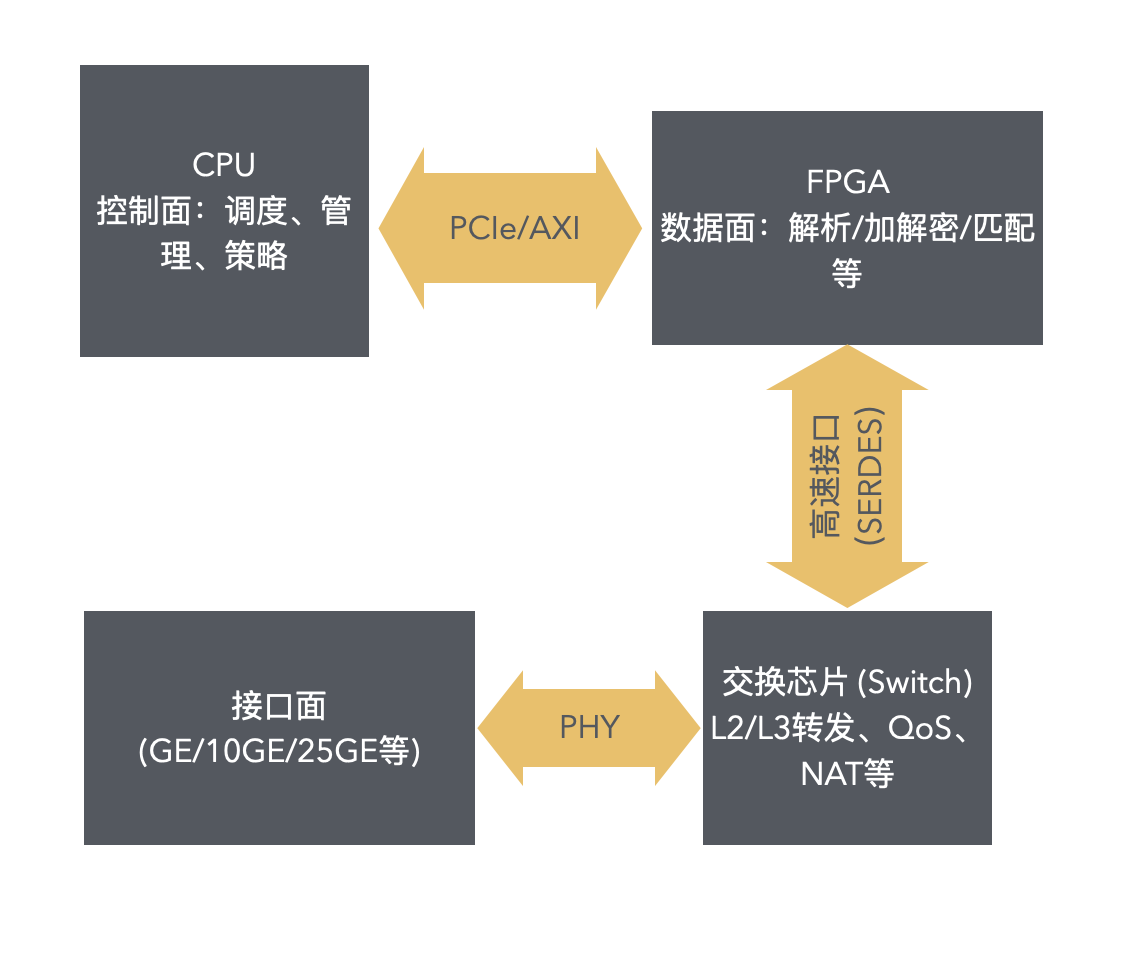

基于CPU+FPGA+交换芯片的异构计算硬件平台架构方案

基于CPU + FPGA + 交换芯片的异构计算硬件平台架构方案,适用于如边缘计算网关、智能交换设备、工业网络平台、安全处理器等高性能网络场景。

一、系统图示

二、功能分区说明

1. CPU(管理面)

-

运行嵌入式Linux系统;

-

处理管理配置、RESTful API、SNMP、Netconf等;

-

协调FPGA与交换芯片间的资源与策略;

-

可提供Docker容器平台支持边缘计算服务。

2. FPGA(数据处理面)

-

实现高速数据流处理与加速任务,例如:

-

DPI(深度包检测);

-

ACL(访问控制列表);

-

NAT(地址转换);

-

时间戳打标;

-

协议转换(如Modbus ↔ MQTT);

-

-

可通过动态加载bitstream灵活切换任务类型;

-

与CPU协同:CPU发规则,FPGA执行。

3. 交换芯片(转发面)

-

提供高吞吐、高速转发能力;

-

执行L2/L3路由转发;

-

支持QoS、VLAN、LACP、ACL等常规网络功能;

-

可通过FPGA/CPU加载TCAM规则,实现流表控制。

三、典型接口设计

模块

通信接口

描述

CPU ↔ FPGA

PCIe Gen3/Gen4 或 AXI over SoC

管理指令与规则下发

FPGA ↔ Switch

SerDes / XAUI / 10G Aurora

高速数据交互

CPU ↔ Switch

I²C / MDIO / SPI

芯片配置与状态读取

外部端口

SFP+/QSFP+/RJ45

可提供1G/10G/25G等物理链路

四、实际应用场景

✅ 场景一:工业级边缘网关

-

FPGA实时采集、解析现场设备数据;

-

CPU本地处理协议转换与云对接;

-

交换芯片实现本地L2网络组网;

-

应用:工厂车间、轨道交通、电力通讯。

✅ 场景二:高性能安全网关/防火墙

-

FPGA完成线速的DPI、黑名单匹配、加解密;

-

CPU进行日志分析与策略管理;

-

交换芯片保障转发性能;

-

应用:数据中心边界、政企专网安全。

✅ 场景三:智能交换设备(L2+)

-

CPU提供管理与远程运维;

-

FPGA定制网络策略,如镜像、时间戳、流量标记;

-

ASIC芯片进行常规L2/L3转发;

-

应用:工业园区、智慧楼宇、智能交通网络。

五、关键优势

特性

说明

高性能

FPGA并行处理+Switch线速转发,可达数十Gbps甚至百Gbps

灵活性

FPGA可重构;CPU软件可升级;适应复杂业务需求

可编程

各模块可通过软硬件接口配置规则

可扩展

支持未来加入AI加速单元、TSN时间同步等扩展模块

六、可选优化方向(进阶设计)

-

引入AI推理引擎(NPU)协助流量识别(如智能分类);

-

加入TSN(Time Sensitive Networking)模块用于工业实时性;

-

增设高可用双系统冗余设计(双CPU、双FPGA);

-

接入**SDN控制器接口(如OpenFlow、gRPC)**实现集中式策略编排。