基于实际工程的STA时序分析(FPGA)_fpga sta分析

近来发现新人对时序分析总是一知半解,但是这个是很重要的,也是FPGA能转行到IC相关的基础。首先要明确的是FPGA的运行流程是什么样子的?

一、FPGA的实现流程

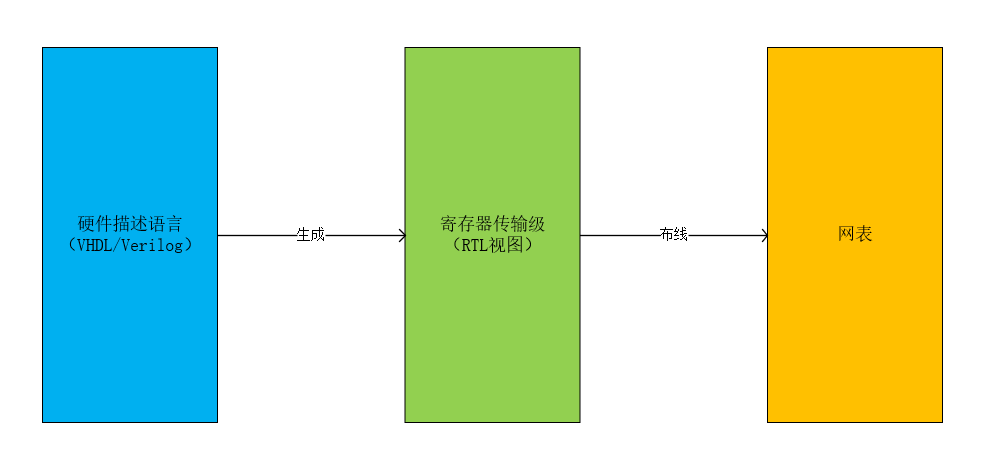

如图所示,硬件描述语言的本质目的是为了生成RTL,建立起寄存器间的连线关系,也就是第一步编译的过程,从RTL到网表就是根据你的RTL图来布线把各个资源连接到一起以实现功能,相比于ASIC,FPGA自由度更高,但是成本更高,顺便解析一下在布线的时候由于FPGA的资源分别呈现列阵的形式,早期的FPGA有大量的门电路所以就叫现场可编程(硬件描述现场生成电路)们列阵(布线过程)的原因。科学的描述如下所示:

硬件描述语言(HDL)的本质是通过抽象化建模实现数字电路的寄存器传输级(RTL)描述,其核心目标是定义寄存器间的数据传输逻辑与时序行为。RTL并非直接描述物理电路,而是以时钟驱动下的寄存器同步更新(如Verilog的always @(posedge clk))为核心,构建逻辑功能的抽象模型

。从RTL到网表的过程分为两个关键阶段:

- 逻辑综合:工具将RTL代码映射到目标器件的底层单元(如FPGA的查找表LUT或ASIC的标准单元),生成门级网表。例如,一个加法器可能被拆解为多个LUT和进位链的组合。

- 布局布线:

- FPGA:利用可编程逻辑块(CLB)和互连资源的二维阵列结构动态配置电路。CLB内部包含LUT和触发器,通过开关矩阵(SB)和连接块(CB)实现信号路径的灵活连接。这种“现场可编程”特性源于FPGA的SRAM配置机制——用户通过下载比特流文件实时重构硬件功能,而无需物理修改芯片。

- ASIC:采用固定布局的专用电路,布线需考虑物理效应(如时序收敛、串扰),且无法后期修改。

相较于ASIC,FPGA的核心差异体现在:

- 自由度:FPGA的CLB阵列和互连资源支持动态重构,适合快速迭代;而ASIC功能固化,但可通过定制电路实现更高性能(速度提升2-5倍)和更低功耗(降低50%以上)。

- 成本结构:FPGA无流片费用,适合小批量(<40万片);ASIC流片成本高(数百万美元),但大批量时单片成本显著下降。

- 资源效率:FPGA因通用架构存在冗余(如LUT未充分利用),而ASIC可针对功能优化,面积效率提升5-10倍。

FPGA“现场可编程门阵列”的名称源于其硬件架构:

- 门阵列:早期FPGA由基本逻辑门构成规则阵列,通过熔丝技术编程;现代FPGA采用LUT作为基本逻辑单元,但仍保留阵列式布局。

- 布线资源特性:FPGA的布线通道呈网格状分布,包含全局长线、区域短线和可编程开关,工具通过动态配置这些资源实现信号路径的灵活连接,形成“硬件描述现场生成电路”的效果。

二、STA时序分析基础

静态时序分析(STA)的整个流程可概括为:通过静态建模与路径分析,验证芯片所有信号在目标时钟周期内稳定传输。具体步骤包括:

- 环境初始化:加载网表、工艺库(如单元延迟模型)、时钟定义(频率/不确定度及时序约束文件(SDC);

- 路径识别与延迟计算:提取寄存器间、输入/输出端等四类时序路径,结合工艺库的单元延迟和寄生参数(如SPEF文件中的RC值)计算总延迟;

- 时序检查:对比信号到达时间与时钟周期,检查建立时间(数据提前稳定)和保持时间(数据维持稳定)是否满足要求,并计算时序余量(Slack),若Slack为负则标记违例;

- 优化与签核:针对违例路径调整逻辑结构(如插入缓冲器)或优化布局布线,最终确保所有路径Slack≥0且时钟偏斜在容限内,完成时序收敛。

对于FPGA工程师来说,这一部分都由EDA实现,我们只需要研究软件给出的时序报告对症下药就可以了,这也是本文的主要内容。

三、时序报告分析和问题解决

首先应当明确组合逻辑和时序逻辑的关系,通俗的说时序逻辑就是以时钟边沿为触发条件的逻辑,组合逻辑就是两个器件直接连接与时钟无关,只要信号跳变就会立刻影响到其余的器件,这也是为什么在Verilog中时序逻辑一定要使用reg,组合逻辑要使用wire的直观解释。科学的解释就是如下:

组合逻辑:输出仅由当前输入决定,无记忆功能,通过连续赋值(如Verilog的assign或VHDL的并发语句)实现

时序逻辑:输出由当前输入和电路历史状态共同决定,需通过时钟触发(如always @(posedge clk))和寄存器存储状态。

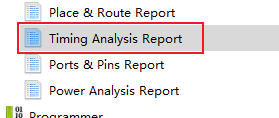

程序编译布线完毕以后进入时序分析报告(因为政策要求,目前工程全部换成国产FPGA,本demo也是某国产FPGA和对应的EDA)

找到违例时序

进入标红处:

![]()

![]()

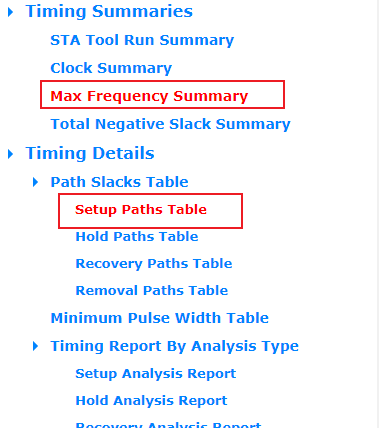

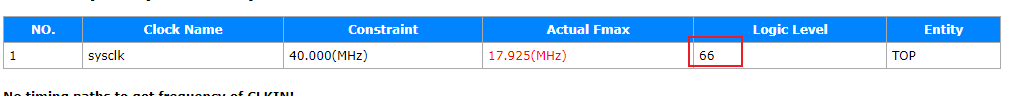

可以清晰的看到哪个寄存器导致时序违例,以及时钟余量等参数,还有主时钟实际能跑到的频率,可以看到十分严重,有重大时序bug。

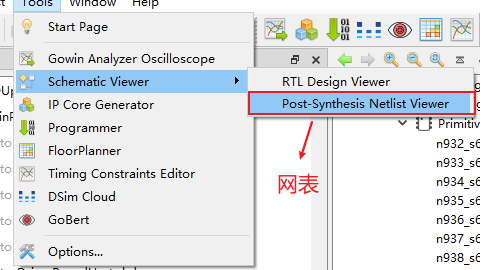

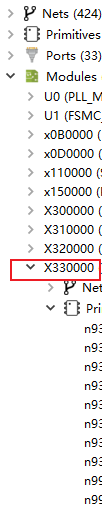

进入网表,找到对应的寄存器

进入网表后找到对应的寄存器(起点)开始分析:

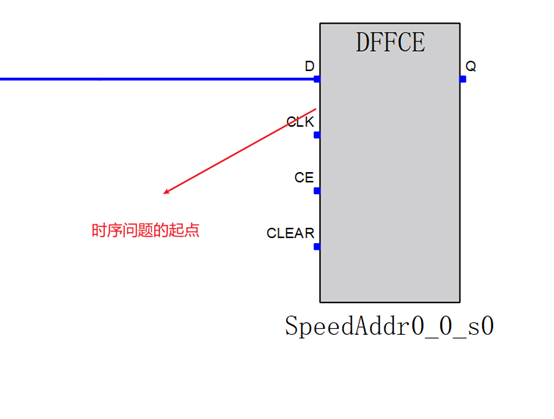

好了,从这里开始分析吧,至于为什么这个时序违例这么严重,请看 :

这还只是起点部分的LUT和寄存器资源已经非常负责嵌套多层,从主时钟看已经嵌套了很多层逻辑了,推断出RTL设计时存在重大bug,需要分析具体代码解决。

以上就是整个分析流程。