【FPGA】Verilog实现RS422通信、UART_fpga rs422

1.RS422通信协议简介

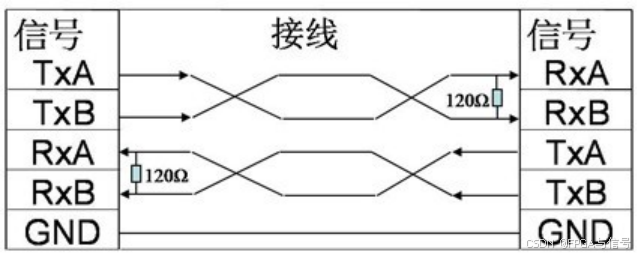

RS422是一种差分串行通信协议,具有抗干扰能力强、传输距离远(最长1200米)、支持全双工通信等特点。全双工工作模式下需要4线(2对差分线),引脚定义如下所示。

接线方式如下所示。

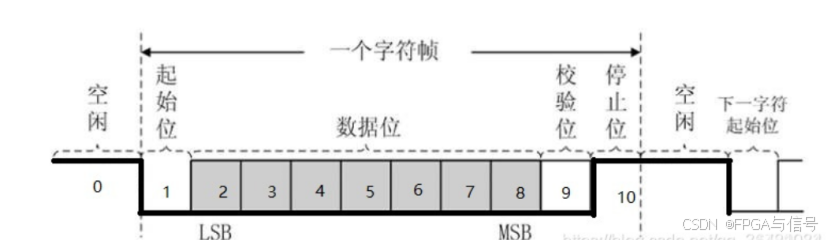

2.RS422时序

具体的时序如下,以发送为例,txd 在不工作时处于空闲状态,即高电平,当有数据需要发送时,使能tx_en后,首先发送一个低电平信号(逻辑0)并保持一个波特率的时间,之后发送8bit有效数据,发送顺序从最低位到最高位,每隔一个波特率的时间会开始发送下一个 bit,直到 8 个 bit 位发送完成。发送完成之后就开始发送校验位(具体为0还是为1需要根据发送的数据即采用的校验方式决定),在经过一个波特率时间后,开始发送停止位(如果停止位设置为 1,则保持一个波特率时长的时间;如果停止位为 2,则保持 2 个波特率时长的时间),至此一帧数据发送完毕。

3.Verilog代码实现

// RS422发送模块module rs422_tx ( input clk, // 系统时钟 input rst_n, // 异步复位(低有效) input tx_en, // 发送使能信号 input [7:0] data_in, // 并行输入数据 output reg tx_p, // 差分正输出 output reg tx_n // 差分负输出);parameter CLK_FREQ = 100_000_000; // 100MHz系统时钟parameter BAUD_RATE = 115200; // 波特率localparam DIVIDER = CLK_FREQ / BAUD_RATE;//868reg [15:0] clk_div; // 波特率分频计数器reg [3:0] bit_cnt; // 数据位计数器reg [7:0] data_reg; // 数据寄存器reg tx_active; // 发送状态标志,busy signal// 状态机定义parameter IDLE = 3\'d0 ;parameter START_BIT = 3\'d1 ;parameter DATA_BITS = 3\'d2 ;parameter STOP_BIT = 3\'d3 ;reg[2:0] state;// 差分信号驱动task drive_diff; input bit_val; begin tx_p = bit_val; tx_n = ~bit_val; endendtaskalways @(posedge clk or negedge rst_n) begin if (!rst_n) begin state <= IDLE; clk_div <= 0; bit_cnt <= 0; tx_active <= 0; drive_diff(1\'b1); // 空闲状态 end else begin case (state) IDLE: begin drive_diff(1\'b1); if (tx_en && !tx_active) begin data_reg <= data_in; tx_active <= 1\'b1; state <= START_BIT; clk_div <= 0; bit_cnt <= 0; end end START_BIT: begin drive_diff(1\'b0); // 发送起始位 if (clk_div == DIVIDER-1) begin clk_div <= 0; state <= DATA_BITS; end else begin clk_div <= clk_div + 1; end end DATA_BITS: begin drive_diff(data_reg[bit_cnt]); if (clk_div == DIVIDER-1) begin clk_div <= 0; if (bit_cnt == 7) begin state <= STOP_BIT; end else begin bit_cnt <= bit_cnt + 1; end end else begin clk_div <= clk_div + 1; end end STOP_BIT: begin drive_diff(1\'b1); // 发送停止位 if (clk_div == DIVIDER-1) begin tx_active <= 0; state <= IDLE; end else begin clk_div <= clk_div + 1; end end endcase endendendmodule4.仿真测试

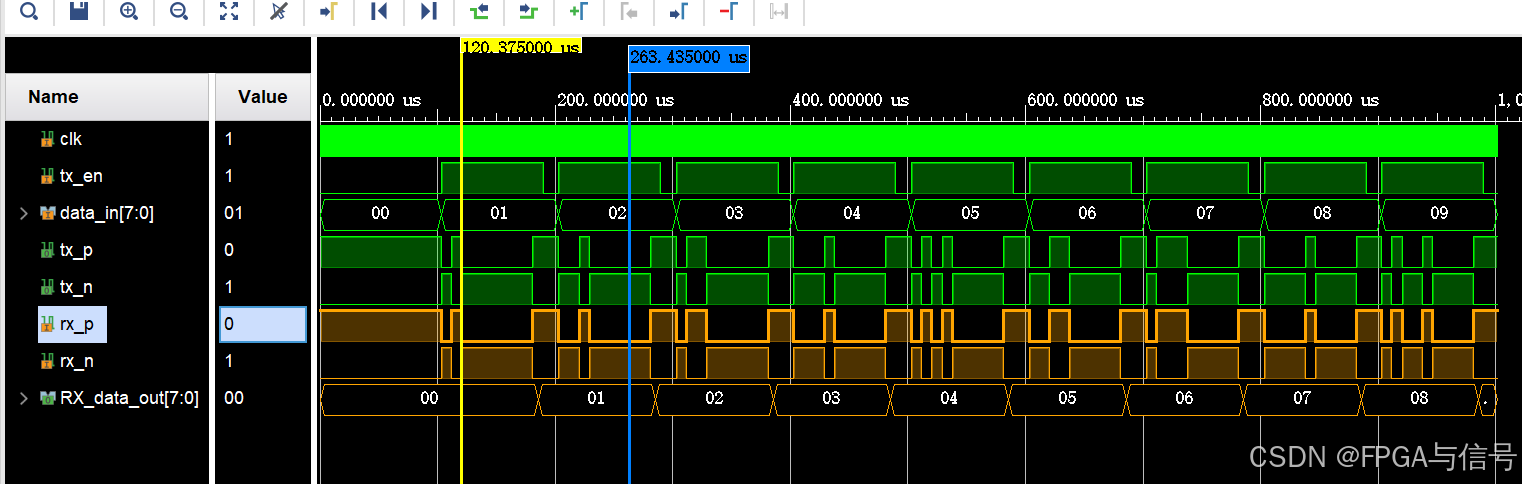

从TX端配置8bit发送数据,波特率采用115200,按照每100us发送一帧数据,测试数据为递增数据,通过RX端进行数据接收,将TX端输出的串行数据转换为并行数据,通过仿真可以看到,TX端发送的数据在RX端被正确解出。

代码下载链接:https://download.csdn.net/download/weixin_42370509/90496300