[小梅哥FPGA] 如何通过动态重配置实现FPGA时钟的实时频率/相位/占空比调整?_xilinx pll 实时调整时钟相位

案例说明

xilinx的7系列FPGA中,提供有高性能的时钟管理单元(CMT),每个CMT中都包含有一个PLL和MMCM。PLL和MMCM是实际存在的硬件电路,用以对输入时钟的负面变化,如抖动、频率变化、相位偏移、占空比失真等进行处理。用户可以通过配置clocking wizard核来控制PLL/MMCM电路,以使其基于输入时钟产生在频率、相位、占空比等方面符合要求的新时钟。clocking wizard核的配置方式有两种,一种是最直观的GUI界面配置,另一种则是本帖要讲的动态重配置。

操作步骤说明

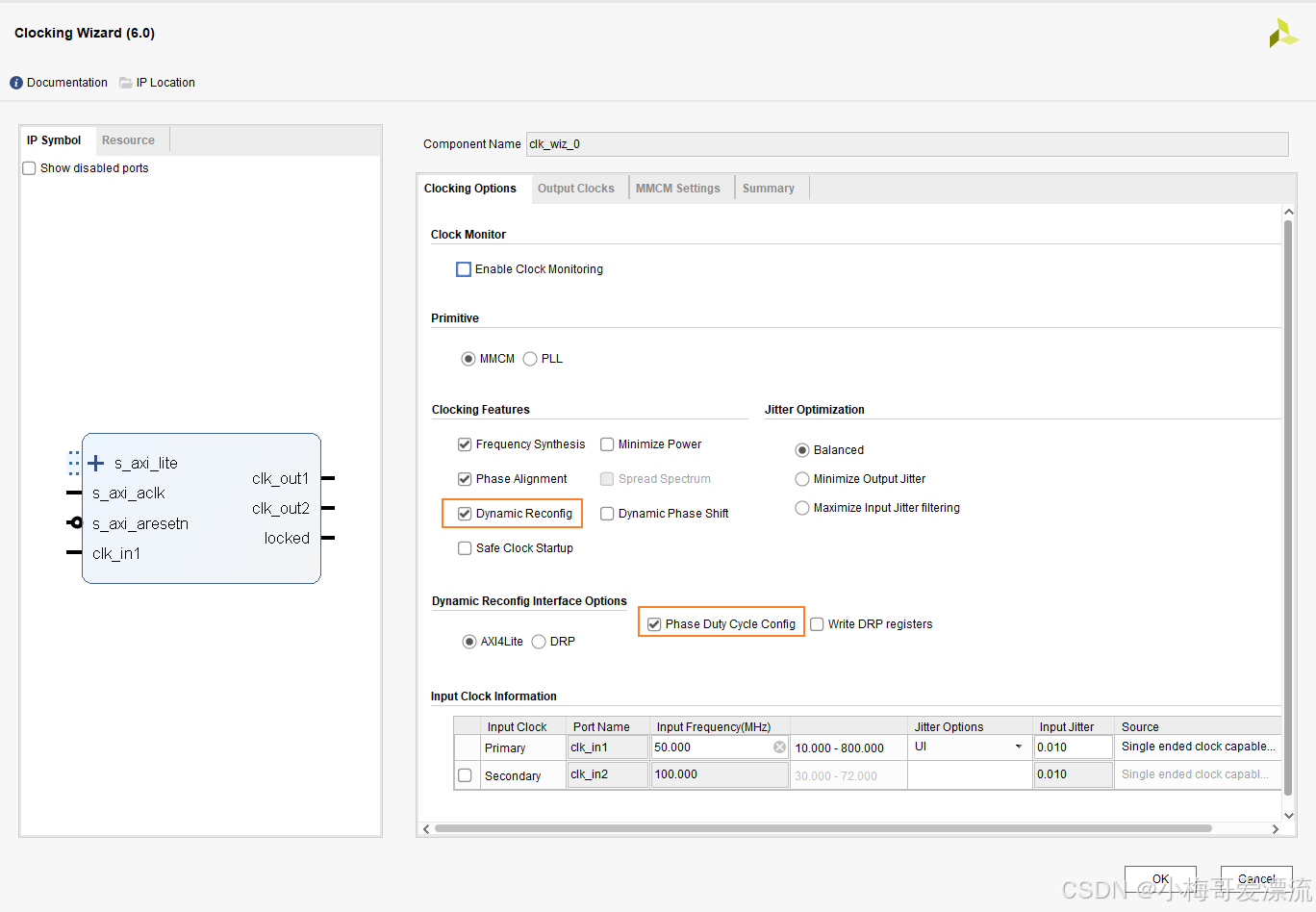

PLL/MMCM的动态重配置需要在GUI界面中勾选Dynamic Reconfig选项,然而该选项只能对时钟频率进行配置,用户如果想要配置相位和占空比,还需要勾选Phase Duty Cycle Config或者Dynamic Phase Shift。勾选Dynamic Phase Shift的情况下,IP核会多出四个引脚,功能如下:

相位偏移完成标志信号

使用该方式配置PLL相位相较复杂,用户需要提供参考时钟以及对应脉冲信号,因此,对于一般的应用场景这里更推荐Phase Duty Cycle Config的方式。

在勾选了Dynamic Reconfig和Phase Duty Cycle Config之后,便可以通过对应的接口配置相关寄存器,接口通常选用AXI4-Lite。配置频率、相位、占空比的相关寄存器如下:

Bit[25:16] = CLKFBOUT_FRAC Multiply(仅MMCM才有,VCO的1/8小数倍频系数)

Bit[15:8] = CLKFBOUT_MULT(VCO整数倍频系数)

Bit[7:0] = DIVCLK_DIVIDE(VCO分频系数)

Bit[31:0] = CLKFBOUT_PHASE

Bit[7:0] = CLKOUT0_DIVIDE

Bit[17:8] = CLKOUT0_FRAC Divide(仅MMCM才有,CLKOUT0的1/8小数倍频系数)

Bit[31:0] = CLKOUT0_PHASE

Bit[31:0] = CLKOUT0_DUTY

Bit[7:0] = CLKOUT1_DIVIDE

......

......

......

Bit[1] = SADDR, 写 0 将默认 GUI 中的参数加载到动态配置中;

写 1 将配置寄存器参数加载到动态配置中

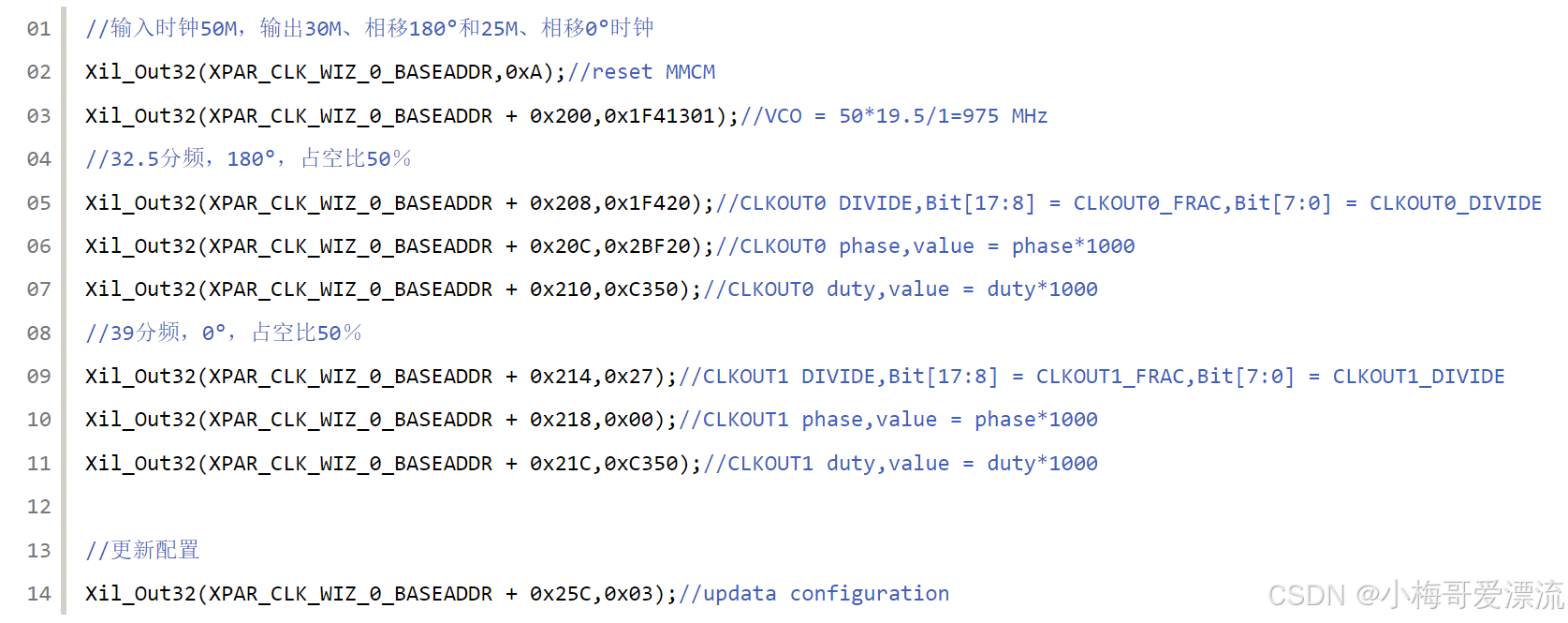

基于该表,用户在初始化Clk_Wiz后,只需要计算好所需的频率、相位、占空比对应的设置值,使用Xil_Out32函数配置对应寄存器即可。配置完成后再向Clock Configuration Register 23中写入0x3即可完成配置的加载,随后等待新时钟的生成。

示例代码如下:

通过上述步骤,在平时的开发调试过程中,亦或是一些对于时钟可能有着实时性要求的设计(如数据采集、图像处理)里,我们便可以在无需重新修改设计的前提下,通过AXI4总线来完成对时钟频率、相位的调控,从而达到缩短设计周期以及让设计适应更多场景的目的。