vivado 学习(0)--- clocking wizard 的使用_vivado clock wizard

文章目录

前言

工程使用的所有时钟都应该尽量避免直接使用板子的晶振,

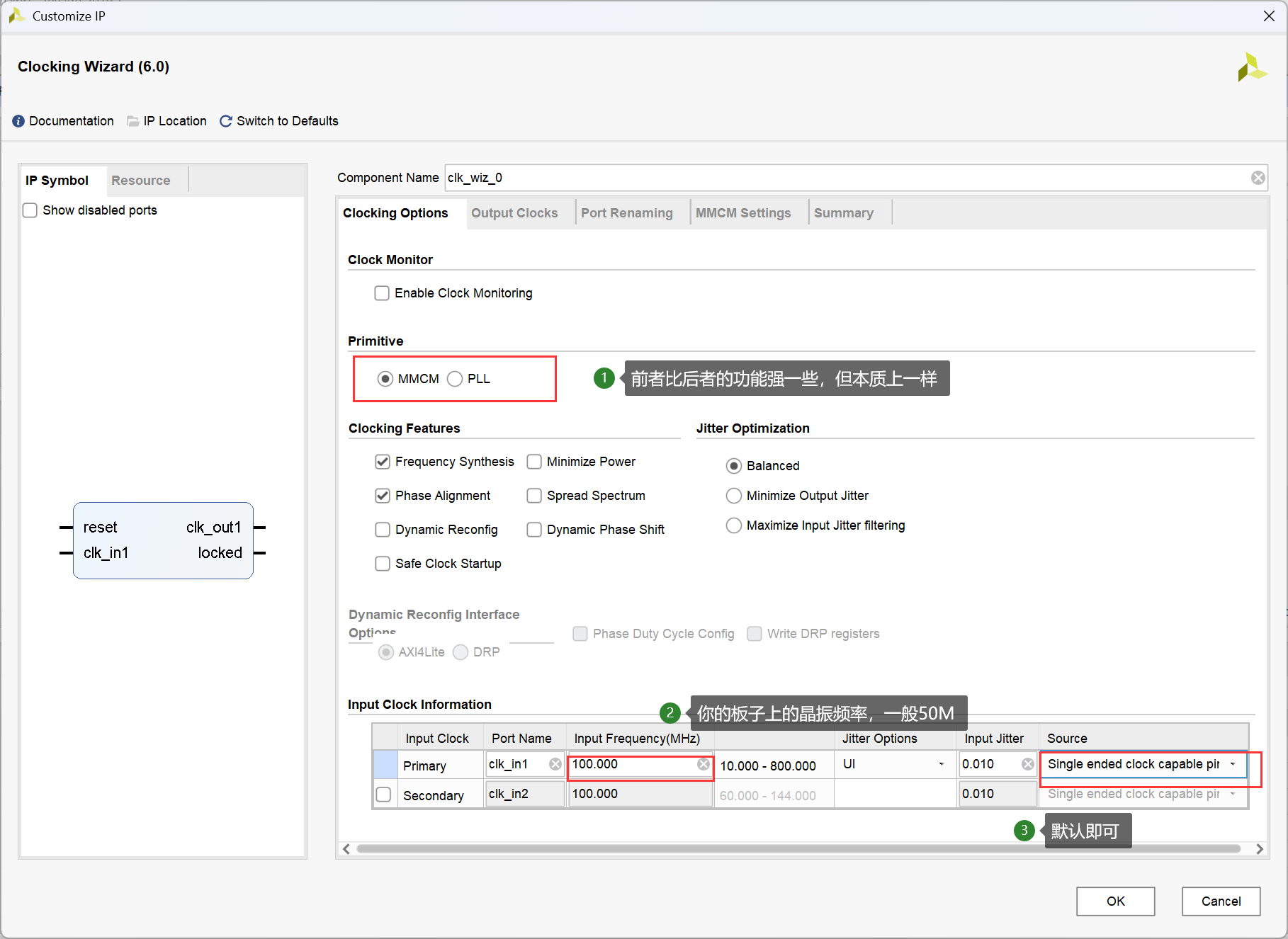

使用clk_wizard ip 核可以:1.使时钟更加稳定;2.可以分频、倍频以获得多种频率的时钟。

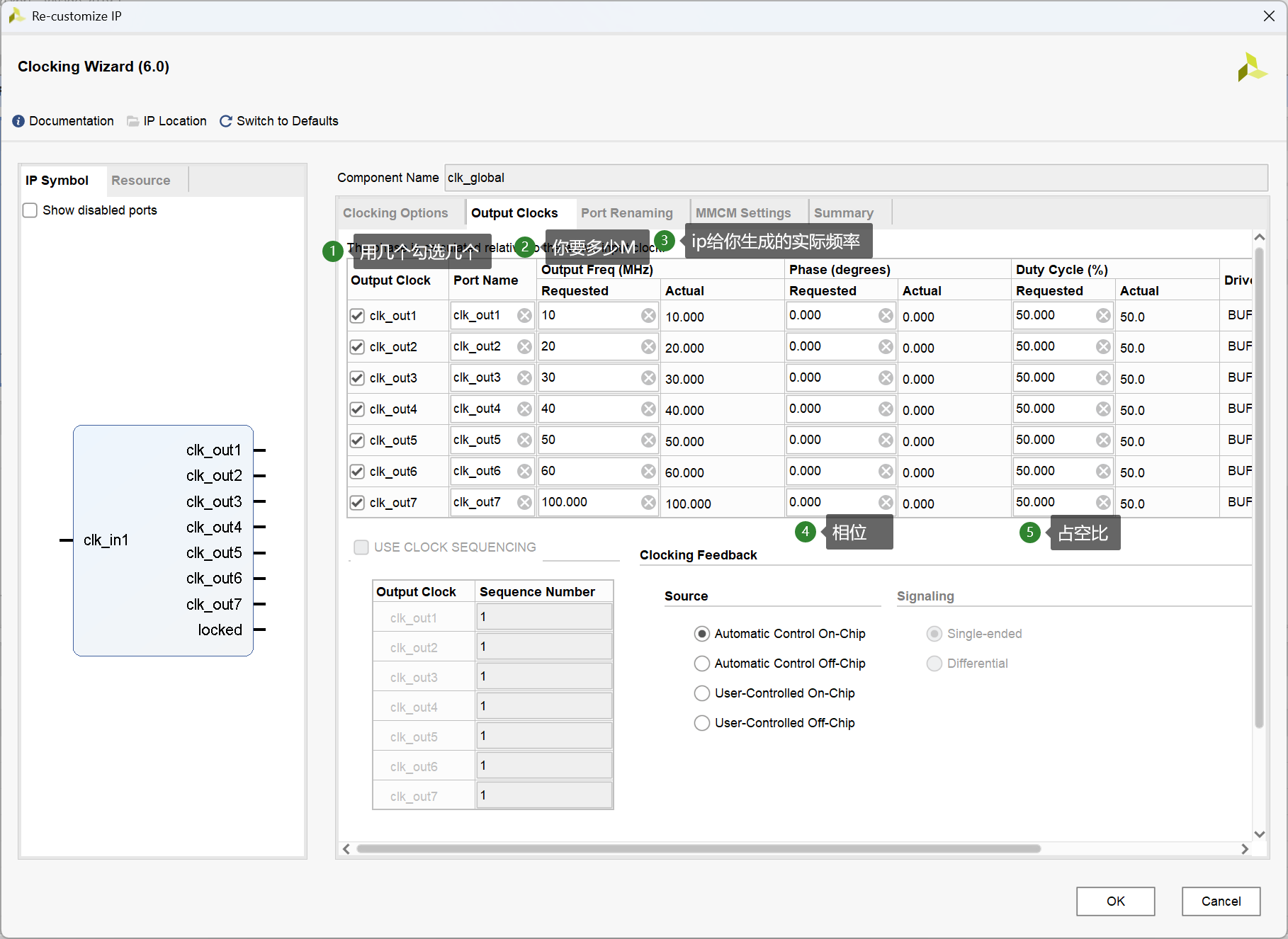

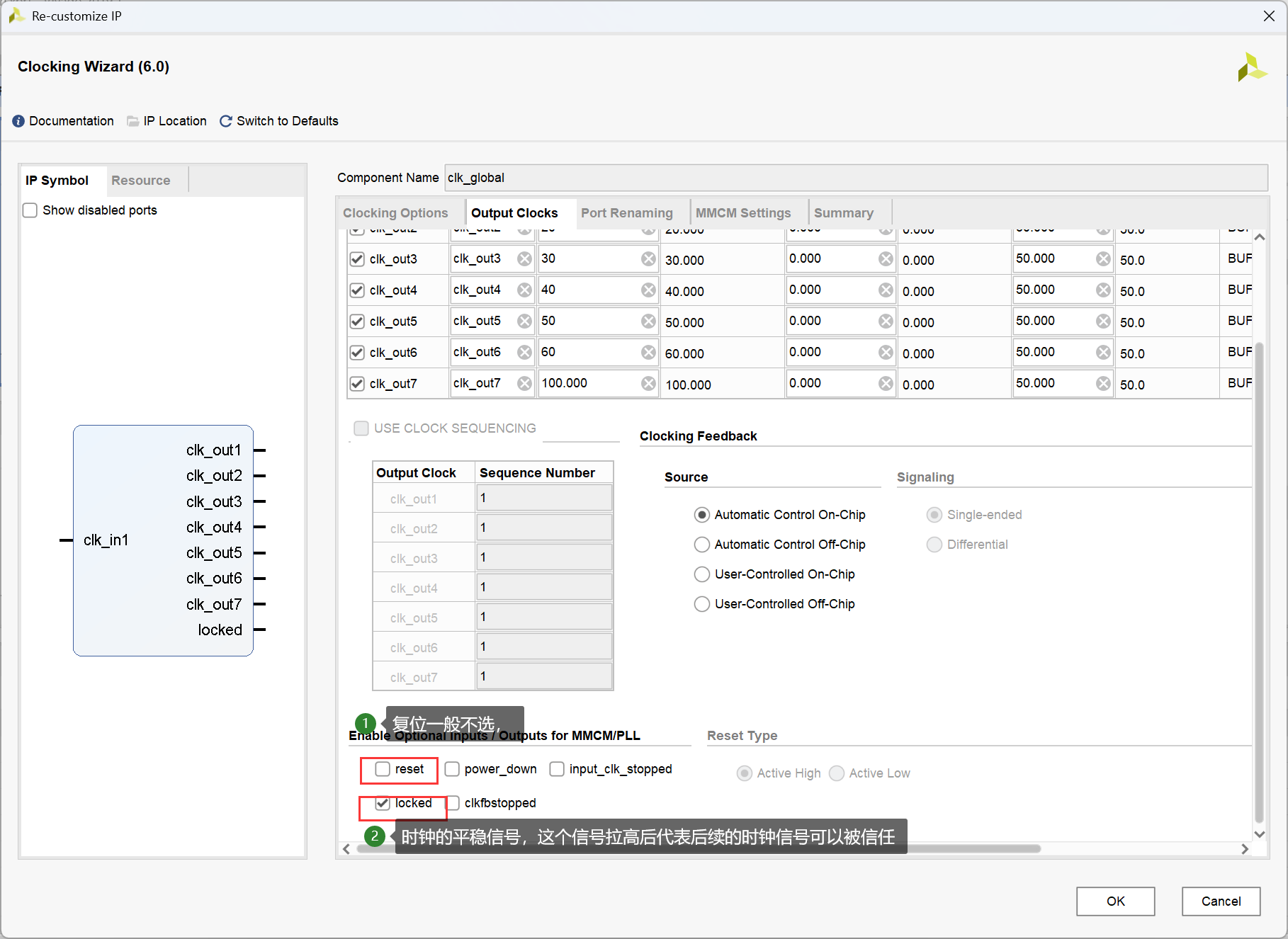

一、目标时钟与实际时钟相同

PLL有时在生成某些频率时并不能生成完全一致的时钟,存在误差。

下面先展示无误差,再展示有误差的情况怎么解决。

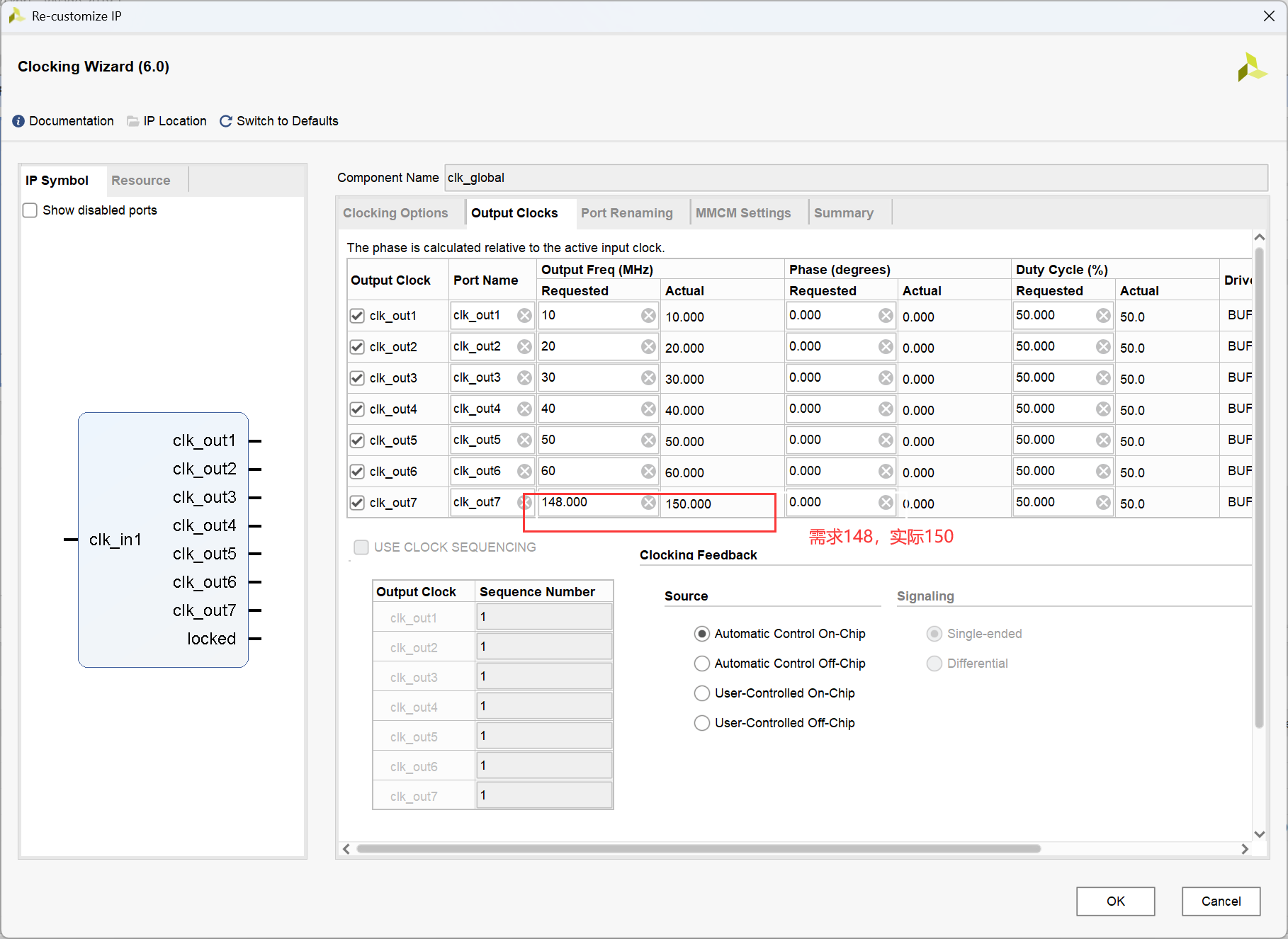

二、目标时钟与实际时钟近似

直接说结论,50Mhz时钟不能生成所有频率的时钟,有时你需要的时钟不能直接由原始晶振生成的时候,需要用中间时钟来辅助生成

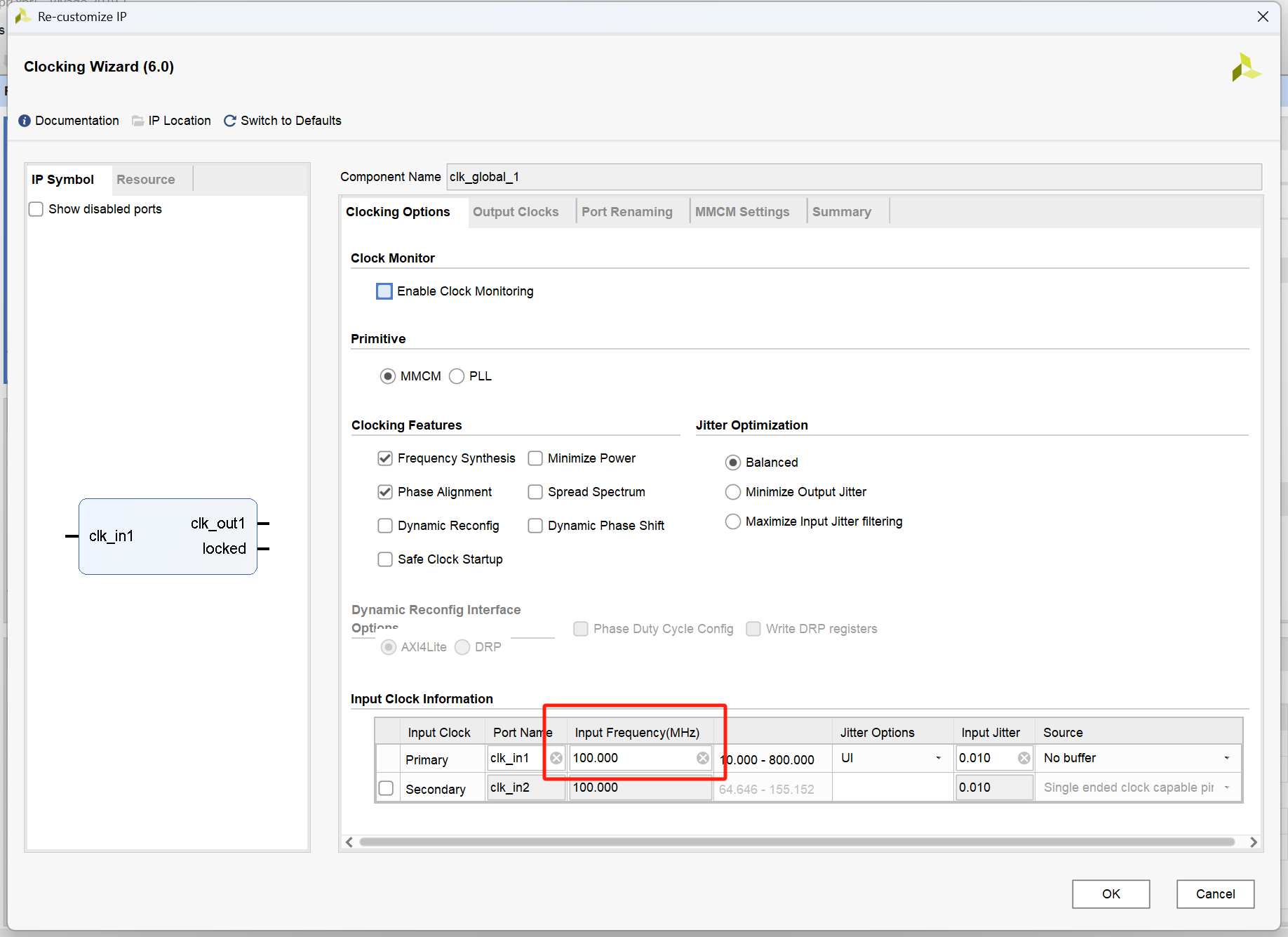

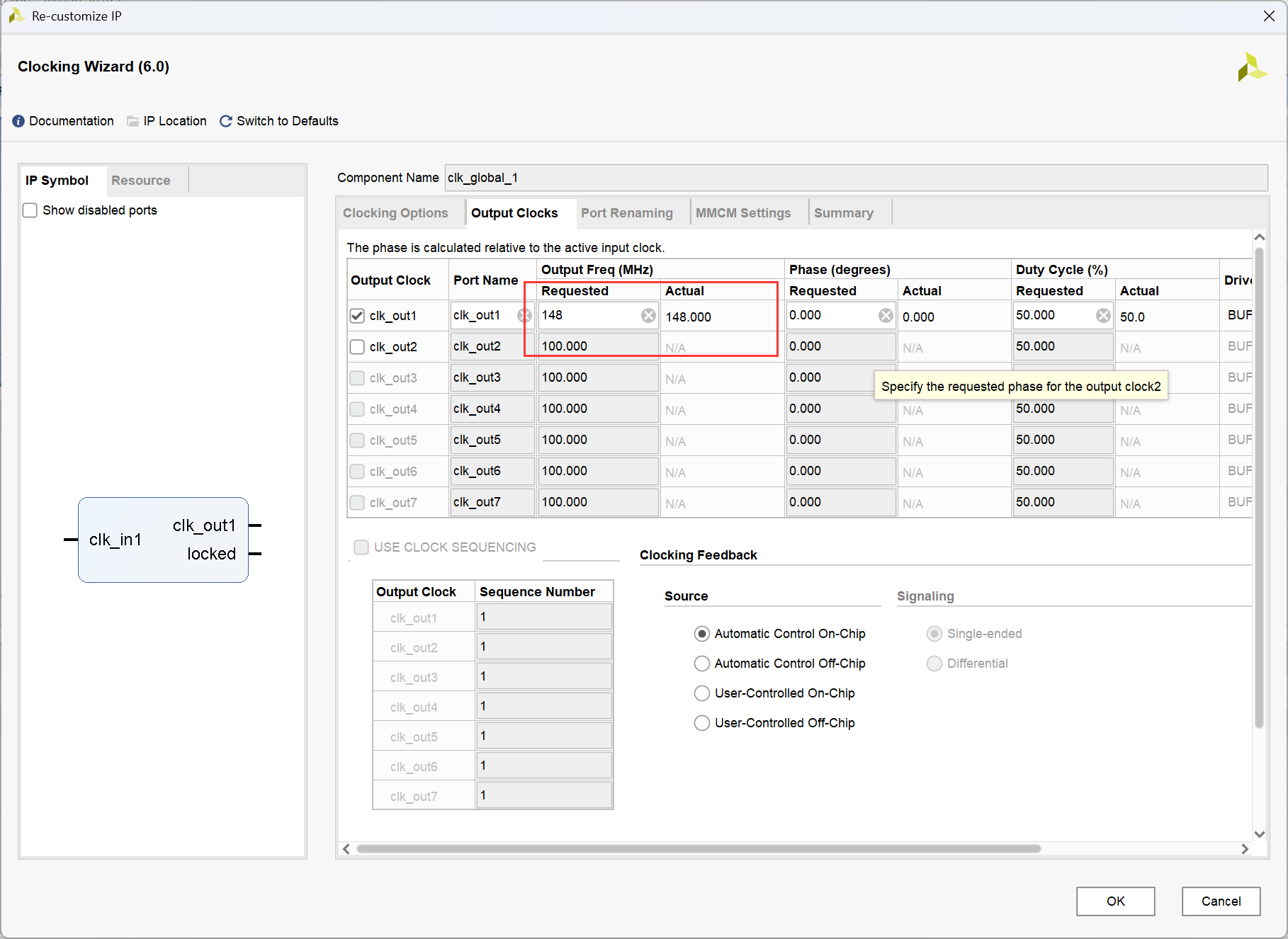

148Mhz 由100Mhz生成时无误差,因此我们需要让clk_in1为100M。

具体操作是使用两个ip,第一个ip输出100M,把这个100M接到第二个ip的输入,第二个ip就可以完美输出148Mhz了。

三、代码实现

顶层文件

`timescale 1ns / 1psmodule clk_wiz( input clk );wire clk_out1 ;wire clk_out2 ;wire clk_out3 ;wire clk_out4 ;wire clk_out5 ;wire clk_out6 ;wire clk_out7 ;wire locked1 ; wire locked2 ;wire clk_out8 ; clk_global u1_clk_global( .clk_in1 (clk ), .clk_out1 (clk_out1 ), .clk_out2 (clk_out2 ), .clk_out3 (clk_out3 ), .clk_out4 (clk_out4 ), .clk_out5 (clk_out5 ), .clk_out6 (clk_out6 ), .clk_out7 (clk_out7 ), .locked (locked1 ) ); clk_global_1 u1_clk_global_1( .clk_in1 (clk_out7) , .clk_out1 (clk_out8) , .locked (locked2) ); endmodule仿真文件

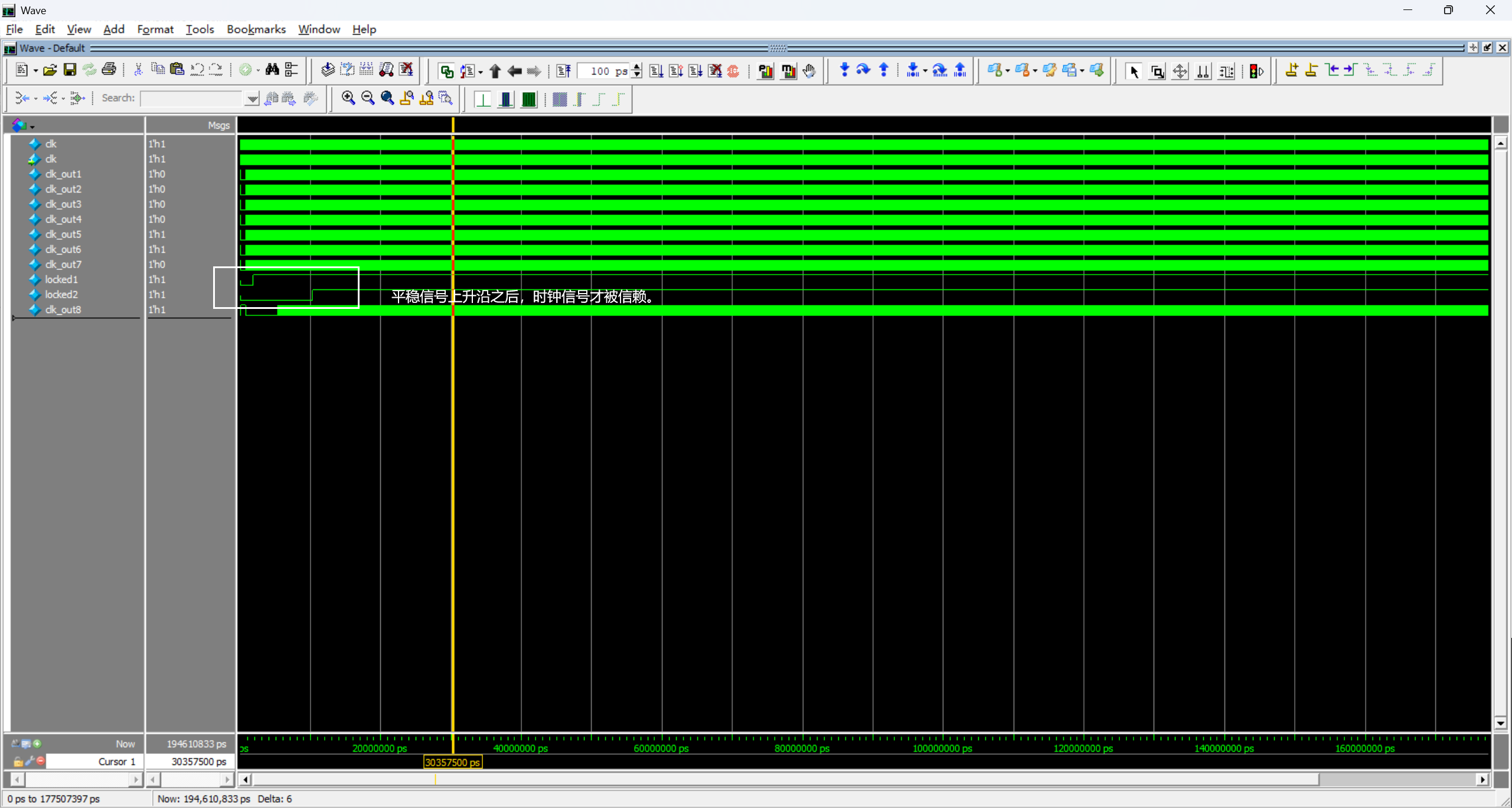

`timescale 1ns / 1psmodule tb_clk_wiz();reg clk ; initial begin clk = 1\'b0;endalways #10 clk = ~clk;clk_wiz u1_clk_wiz( .clk (clk ) );endmodule四、仿真分析

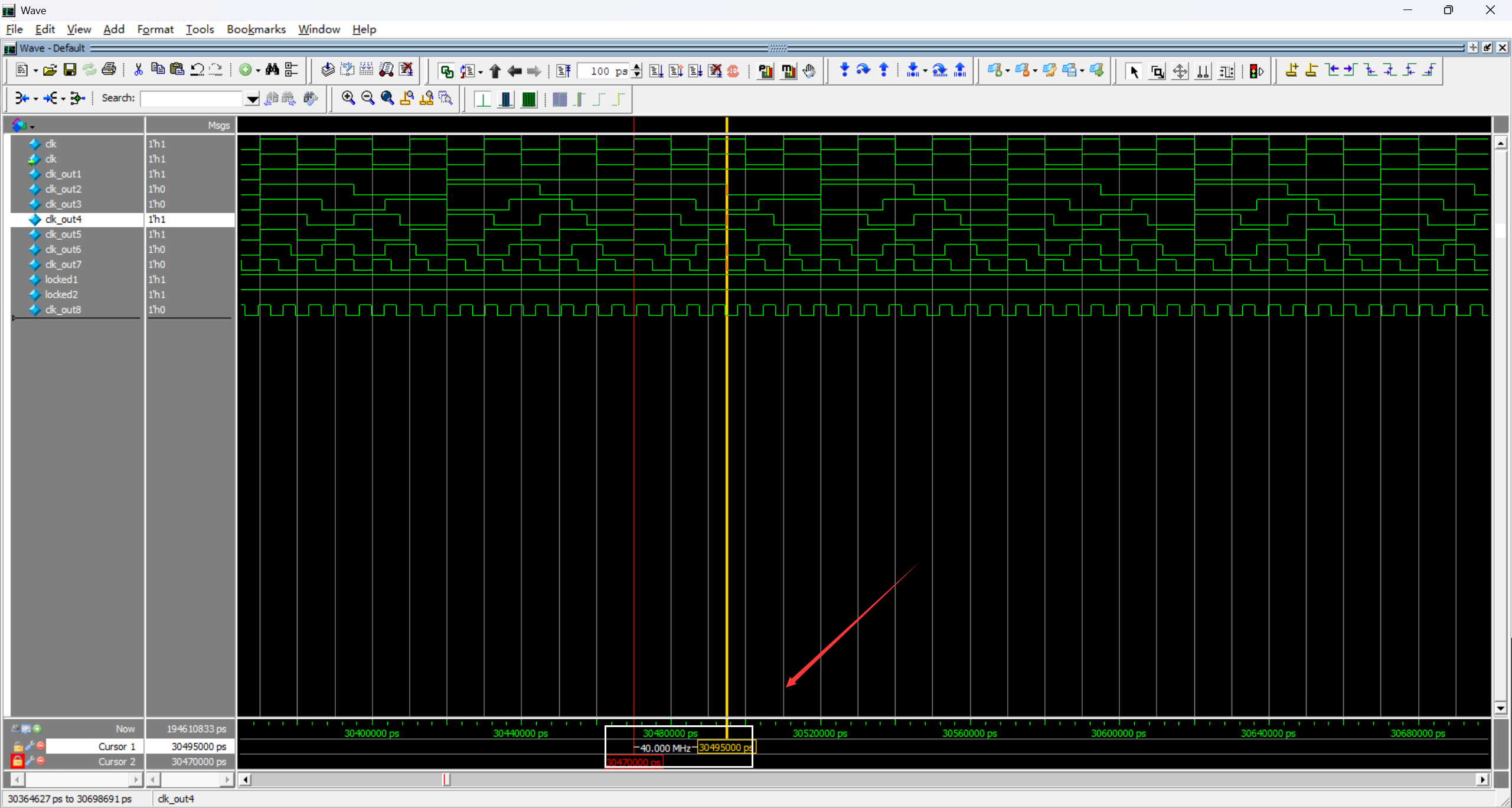

先测试一个4号时钟,从第一节里可以看到我给4号设置了40M,这里看到波形下方的数据确实是40Mhz。

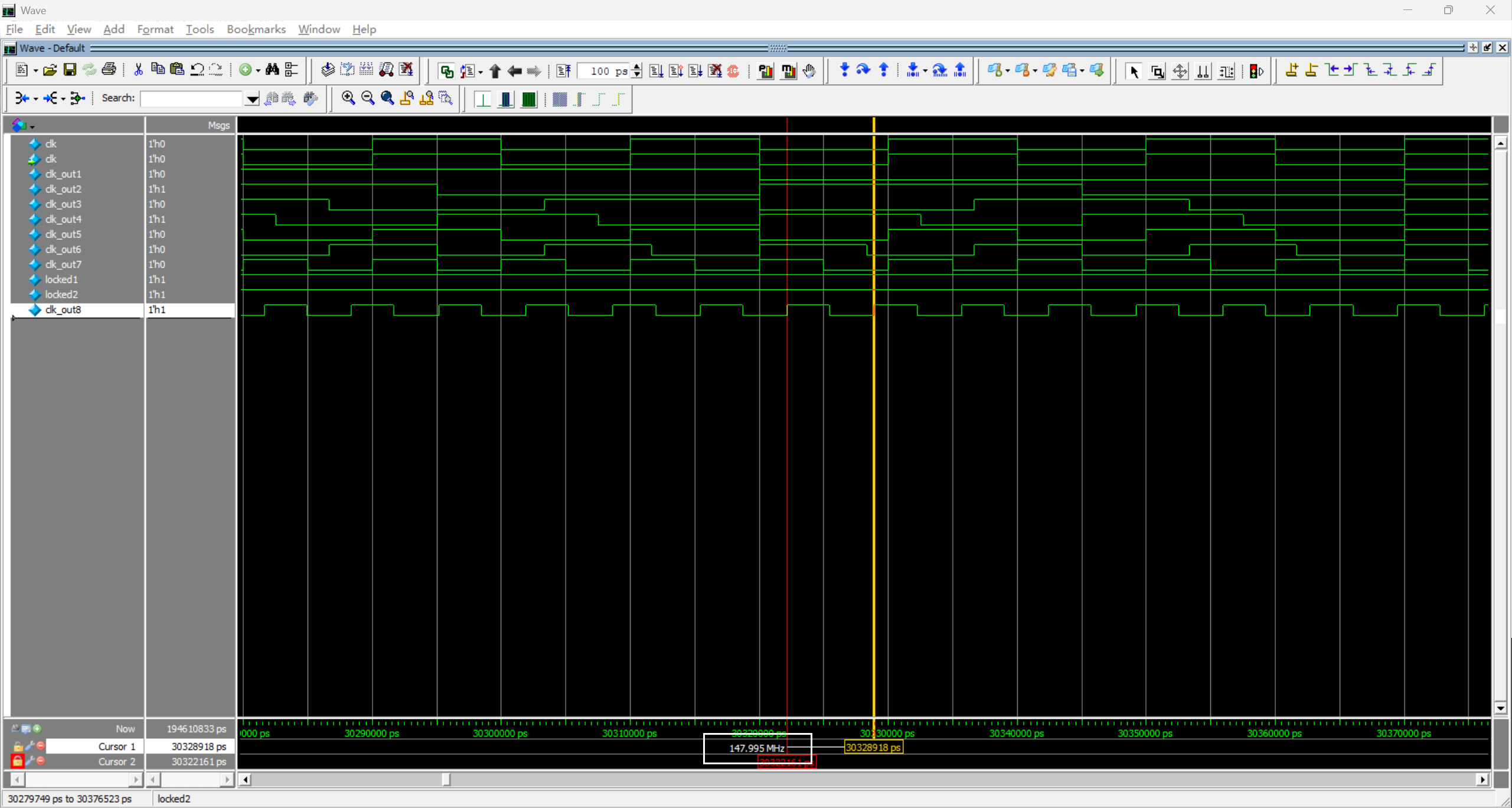

再来测我们的148M。用modelsim抓出来的波形可以看到,频率显示的也不是绝对的148M,但是已经精确到小数点后三位。