FPGA驱动DS18B20温度传感器的Verilog实现

本文还有配套的精品资源,点击获取

简介:本文介绍了如何在FPGA平台上使用Verilog语言设计一个系统来控制和读取DS18B20数字温度传感器的数据。通过这个项目,可以学习到FPGA的编程、数字系统设计以及温度传感器的应用。项目将覆盖DS18B20的初始化、时序控制、数据读取和显示等关键功能,旨在提供一个实际的数字系统设计和硬件编程的学习案例。

1. FPGA平台和Verilog语言介绍

FPGA(Field-Programmable Gate Array)是一种可以通过编程来配置的半导体设备,它包含大量可重配置的逻辑块和互连,允许工程师实现自定义的数字电路设计。与传统的专用集成电路(ASIC)相比,FPGA提供更高的灵活性和较低的设计成本,非常适合原型设计、小批量生产,以及需要快速迭代设计的应用。

FPGA的设计和编程通常依赖于硬件描述语言(HDL),其中最流行的两种语言是Verilog和VHDL。Verilog语言的语法类似于C语言,支持并行逻辑设计,它允许设计师以高级编程语言的方式描述硬件电路的功能和结构。其设计流程涉及模块化设计、仿真测试和综合布局,最终生成可以在FPGA上运行的配置文件。

在进入与DS18B20数字温度传感器的具体应用之前,理解FPGA的基本操作原理和Verilog语言的基础知识是至关重要的。这包括了解FPGA的编程模型、掌握Verilog的基本语法、数据流、结构化和行为化编程概念,以及如何编写简单的测试平台(testbench)。通过这些基础,工程师将能够在后续章节中,针对DS18B20传感器进行高效的数据处理和通信控制。

2. DS18B20数字温度传感器特点和功能

DS18B20的工作原理

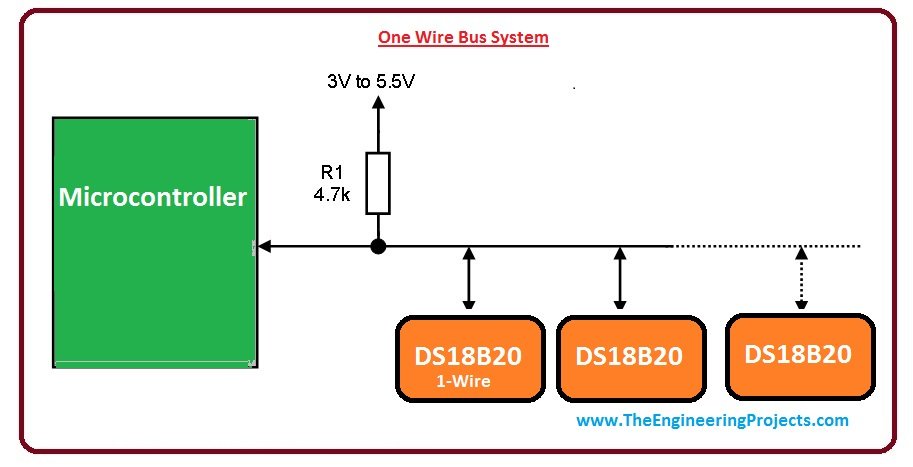

DS18B20是Maxim Integrated生产的数字温度传感器,它提供了一个数字输出信号,包含所测温度的信息,使得数据的处理变得简单且准确。它通过单总线数字通信技术实现,只需要一个数字输入/输出线和地线就可以完成数据的传输。DS18B20内部集成了温度传感器、A/D转换器、控制逻辑等。

工作时,主机设备通过单总线发送复位脉冲,然后发送“跳过ROM”和“转换温度”命令给DS18B20。DS18B20接收到命令后,开始转换过程,转换完成后,通过单总线将温度数据传送给主机。DS18B20可以配置为9位至12位精度,并提供±0.5°C的精度范围(在-10°C至+85°C的温度范围内)。

DS18B20的性能特点

DS18B20的温度测量范围为-55°C至+125°C,它具有多种分辨率选项,允许用户根据需要在精度与转换时间之间做出权衡。通过选择不同的分辨率,用户可以设定转换时间从93.75毫秒(9位分辨率)到750毫秒(12位分辨率)不等。

该传感器具有出色的非线性精度保证,当外部采用适当的防护措施时,可以在各种恶劣环境下使用。并且,DS18B20的尺寸非常小,它使得传感器能够被放置在对空间要求苛刻的应用场合中。

DS18B20与传统温度传感器的对比

传统的模拟温度传感器如热敏电阻和热电偶,需要复杂的模拟信号处理电路,且易受环境干扰。与之相比,DS18B20作为数字传感器,输出的是数字信号,因此不受线路干扰和距离限制,并且通过数字信号可以轻松进行远程读取和记录。

DS18B20相较于传统模拟传感器还有功耗上的优势,其单总线操作可以大大降低传感器的待机功耗,使其非常适合在低功耗系统中使用。

DS18B20的独特数字接口技术

DS18B20的数字接口技术允许在一条线上实现数字信号的双向传输,这在传统的模拟传感器中是不常见的。它仅需要一根数据线和一个地线,即可完成数据的发送和接收,大幅度减少了布线的复杂度,非常适合于复杂的嵌入式系统和多点温度监测网络。

DS18B20在环境监测、工业控制的应用

DS18B20广泛应用于各种环境监测系统、温室、暖通空调系统、工业控制以及消费电子中,例如冰箱、饮水机、热敏打印机等。由于其高精度和数字输出的特性,它可以轻松集成到现有的数字系统中,并且由于其小巧的设计,可以部署在有限空间的应用中。

此外,DS18B20的固件允许它在没有主机的情况下也能执行温度监测任务,这意味着在一些分布式温度监控系统中,即使主机设备故障,DS18B20仍能继续工作,并在主机重新在线时传递数据。

DS18B20在消费电子中的应用案例

一个典型的应用案例是在电子体温计中使用DS18B20。体温计需要快速且准确地读取体温,并且在便携式设备中对功耗和尺寸都有严格限制。DS18B20以其小尺寸、低功耗和高精度的特性,完美满足了这些要求。

使用DS18B20时,只要将传感器放置于口腔内,它就会开始温度转换并存储结果。当用户按下按钮时,体温计通过单总线读取温度数据,并在显示屏上展示结果。在设计中,可利用FPGA来实现单总线协议和温度数据的读取、显示逻辑,进一步降低系统复杂度,提高产品的可靠性。

+----------------+ +----------------+| | | || DS18B20 |---->| FPGA || Temperature | | Controller || Sensor | | Module || | | |+----------------+ +----------------+在上图中,DS18B20作为温度传感器与FPGA控制模块相连接。FPGA模块控制DS18B20,读取温度数据,并根据需要执行进一步的处理,如温度显示、数据记录和报警设置等。

DS18B20在工业控制和消费电子中的广泛应用表明,这种数字传感器能够提供可靠的温度信息,并且易于集成到各种系统中,满足日益增长的温度监测需求。通过下一章节将深入讲解如何利用Verilog语言实现对DS18B20的控制,进一步探索这一潜力巨大的应用领域。

3. Verilog在温度传感器控制中的应用

实现DS18B20通信协议的Verilog模块设计

DS18B20数字温度传感器使用单总线通信协议,这对于FPGA来说是一个独特的挑战,因为需要精确控制时序以保持与传感器的同步。在本节中,我们将探讨如何使用Verilog设计模块以实现与DS18B20的通信。下面是一个简化的Verilog模块设计流程,用来生成和解析数据帧。

首先,我们需要定义一个模块,该模块能够生成DS18B20所需的时序信号。例如:

module ds18b20_communication( input clk, input reset, output reg ds18b20_data_line, input [7:0] data_out, output reg [7:0] data_in, output reg data_ready); 在这里, clk 是时钟信号, reset 是复位信号, ds18b20_data_line 是控制数据线的输出, data_out 是要发送到传感器的数据, data_in 是从传感器接收的数据, data_ready 表示数据是否已经准备就绪。

设计通信协议模块的关键部分

为了实现通信协议,我们需要按照DS18B20的规格书定义精确的时序。这包括初始化序列、写时序和读时序。下面是一个初始化序列的简单实现:

parameter RESET_LOW_TIME = 480; // Reset low pulse time in usparameter RESET_HIGH_TIME = 70; // Reset high pulse time in usparameter PRESENCE_PULSE_TIME = 60; // Presence pulse time in usinteger reset_counter = 0;integer presence_counter = 0;reg presence_detected = 0;always @(posedge clk or posedge reset) begin if (reset) begin // Reset logic reset_counter <= 0; presence_counter <= 0; presence_detected <= 0; ds18b20_data_line <= 1\'b1; end else begin // Reset pulse generation if (reset_counter < RESET_LOW_TIME) begin ds18b20_data_line <= 1\'b0; reset_counter <= reset_counter + 1; end else if (reset_counter < (RESET_LOW_TIME + RESET_HIGH_TIME)) begin ds18b20_data_line <= 1\'b1; reset_counter <= reset_counter + 1; end else begin // Presence pulse detection if (!ds18b20_data_line) begin presence_counter = PRESENCE_PULSE_TIME) begin presence_detected <= 1; presence_counter <= 0; end end else begin presence_counter <= 0; end end endend此代码生成了一个复位低脉冲,并等待DS18B20的响应。成功检测到存在脉冲后,通信协议模块认为DS18B20已被正确初始化。

数据帧生成和解析

一旦DS18B20被初始化,就可以发送和接收数据。数据帧的生成和解析遵循DS18B20的协议要求。以下是写数据帧的基本流程:

// Writing data frame to DS18B20parameter DATA_FRAME_WRITE_TIME = 60; // Time for writing a bit in usinteger write_counter = 0;reg [3:0] bit_counter = 0;reg [7:0] data_out_reg = 0;reg writing = 0;always @(posedge clk) begin if (writing) begin if (write_counter < DATA_FRAME_WRITE_TIME) begin ds18b20_data_line <= data_out_reg[bit_counter]; write_counter <= write_counter + 1; end else begin write_counter <= 0; bit_counter <= bit_counter + 1; if (bit_counter == 8) begin writing <= 0; bit_counter <= 0; end end endend数据帧解析类似,但涉及对数据线的监控以获取传入位值。解析逻辑会根据DS18B20协议的细节来执行。

逻辑分析和参数说明

上述代码逻辑展示了如何使用Verilog实现DS18B20通信协议的关键步骤。每个模块都根据DS18B20的规格进行参数化,这样可以容易地调整时序以适应不同的FPGA板和传感器。逻辑分析涉及初始化序列的生成、数据帧的发送和接收。每个参数都有特定的含义,其中:

-

RESET_LOW_TIME:复位低脉冲时间,根据DS18B20的数据手册,大约需要480微秒。 -

RESET_HIGH_TIME:复位高脉冲时间,通常为70微秒。 -

PRESENCE_PULSE_TIME:DS18B20存在脉冲的期望时长,DS18B20规格书推荐60微秒。 -

DATA_FRAME_WRITE_TIME:写数据帧的时间,每位60微秒。

这些时序参数非常关键,因为DS18B20对时序非常敏感,不正确的时序可能导致通信失败。在实际应用中,可能需要根据实际硬件性能和环境条件调整这些参数。

表格展示模块参数和信号

下面是一个表格,展示了关键的模块参数和信号:

| 参数/信号 | 描述 | 类型 | 位宽 | |-----------|------|------|------| | clk | 时钟信号 | 输入 | 1位 | | reset | 复位信号 | 输入 | 1位 | | ds18b20_data_line | 控制DS18B20的数据线 | 输出 | 1位 | | data_out | 发送到DS18B20的数据 | 输入 | 8位 | | data_in | 从DS18B20接收的数据 | 输出 | 8位 | | data_ready| 数据就绪信号 | 输出 | 1位 |

表格中的每个参数和信号都有助于模块的通信和控制流程。接下来的部分将详细讨论如何在实际环境中部署和测试该模块。

在FPGA中部署和测试模块

在设计并实现上述Verilog模块后,下一步是将其部署到FPGA硬件上进行实际测试。为了验证模块的功能,通常需要编写一个测试平台(testbench),它可以模拟DS18B20传感器的行为,以便在没有实际传感器的情况下进行验证。

测试平台的搭建

一个简单的测试平台可以是这样的:

module testbench();// Generate a clock signalreg clk = 0;always #5 clk = ~clk;// Instantiate the module under testwire ds18b20_data_line;reg reset, data_ready;wire [7:0] data_in;reg [7:0] data_out;ds18b20_communication dut( .clk(clk), .reset(reset), .ds18b20_data_line(ds18b20_data_line), .data_out(data_out), .data_in(data_in), .data_ready(data_ready));initial begin // Initialize inputs reset = 1; data_ready = 0; data_out = 8\'d0; // Wait for global reset #100; reset = 0; // Send some data and check for data ready signal data_out = 8\'hAA; // Example data #1000; if (data_ready) begin $display(\"Data ready! Data_in: %h\", data_in); end else begin $display(\"Data not ready!\"); end // End simulation $finish;endendmodule 在此测试平台中,我们生成了一个时钟信号,并实例化了之前设计的模块。通过在模拟开始时设置 reset 信号,我们模拟了系统复位。然后,我们设置 data_out 以发送数据,并等待 data_ready 信号以确认数据已被接收和处理。

测试和验证

为了验证设计的正确性,测试平台需要能够模拟DS18B20传感器的不同响应,包括存在脉冲和各种通信错误。可以通过编写脚本在仿真软件中自动执行这些测试,这有助于确保设计在各种情况下均能正常工作。

在实际硬件上部署时,需要使用逻辑分析仪来监视通信总线,确保时序正确,并检查数据传输是否准确。在调试过程中,可能需要微调时序参数,以确保与实际DS18B20传感器的通信能够顺利进行。

通过这样的测试流程,我们可以确信设计的模块不仅在理论上能够工作,而且在实际硬件环境中也能可靠地执行其功能。这种验证过程对于确保FPGA系统与传感器良好配合至关重要。

深入讨论测试结果

在测试和验证阶段,仔细分析结果对于发现潜在的设计缺陷和错误非常重要。如果模块未能通过某些测试,那么需要回到Verilog代码,检查模块逻辑和时序设置。一些常见的问题可能包括:

- 初始化序列未能成功初始化传感器。

- 数据帧的写入或读取时序不正确,导致传感器没有收到或没有正确响应数据。

- 存在逻辑错误,如未能正确解析传感器返回的数据。

针对这些问题,可以采取逐步调试的方法,逐行检查代码,并通过仿真或硬件测试来验证每一步的正确性。这可能需要反复迭代,直到所有的测试都通过,确认模块能够可靠地与DS18B20通信。

在解决了所有问题之后,该模块就可以在更复杂的系统中使用了。它可以用作构建温度监测系统的基石,或集成到更广泛的应用程序中,提供关键的温度数据。

在下一节中,我们将深入探讨如何利用Verilog实现DS18B20的初始化、读取温度数据和处理异常情况的程序设计。这将涉及到更高级的模块设计和错误处理机制,以及如何优化这些设计以适应不同的应用场景。

4. 实现DS18B20通信协议的关键功能

在FPGA与DS18B20数字温度传感器的交互中,精确实现通信协议是至关重要的。DS18B20通过单总线协议进行通信,其对时序的要求非常严格,因此本章节将深入探讨通信协议中的关键功能以及如何在Verilog中实现这些功能。

单总线协议基础与时序要求

DS18B20使用的单总线协议是一种多主设备通信系统,允许主机通过单根数据线与一个或多个从设备通信。通信过程中的时序是数据同步的基础,它包括了复位脉冲、写时序和读时序。

复位脉冲和存在脉冲

复位脉冲是通信的开始信号。主机必须先发出一个复位脉冲,才能开始与DS18B20通信。主机拉低数据线至少480微秒,然后释放数据线并提供约15微秒的恢复时间。如果传感器存在,它会在接下来的60微秒至240微秒内,通过拉低数据线来产生存在脉冲,以确认通信。

ROM命令和功能命令

复位和存在脉冲后,主机可以发送ROM命令以及功能命令。ROM命令用于选择特定的传感器,而功能命令则指示DS18B20执行特定的动作,如读取温度或写入配置。

数据传输和时序参数

在发送完功能命令后,传感器将开始发送数据。DS18B20的每次数据传输至少需要70微秒。主机需严格按照时序要求,进行数据位的读取或写入。

在Verilog中实现这些时序要求,需要准确地控制时钟周期和信号的产生。下面是一个简化的代码示例,展示了如何在Verilog中产生复位脉冲和存在脉冲的逻辑:

module ds18b20_reset( input clk, // 主时钟 output reg reset_line, // 复位信号线 input wire bus_release // 总线释放信号);// 参数定义parameter RESET_PULSE_WIDTH = 480; // 复位脉冲宽度,单位微秒parameter PRECOVERY = 15; // 恢复时间,单位微钟parameter PRESENCE_PULSE_WIDTH = 60; // 存在脉冲宽度,单位微秒// 时序逻辑initial reset_line = 1\'b0;always @(posedge clk) begin if (!bus_release) begin reset_line <= 1\'b0; // 拉低复位线 #RESET_PULSE_WIDTH; // 维持复位宽度时间 reset_line <= 1\'b1; // 释放复位线 #PRECOVERY; // 等待恢复时间 endend// 检测存在脉冲reg presence_pulse;always @(posedge clk) begin if (!bus_release && !reset_line) begin #PRESENCE_PULSE_WIDTH; // 存在脉冲宽度时间 if (!reset_line) begin presence_pulse <= 1\'b1; // 存在脉冲 end end else begin presence_pulse <= 1\'b0; // 没有存在脉冲 endendendmodule 在上述代码中,我们使用了参数定义了时序宽度,并通过时钟上升沿触发复位脉冲和存在脉冲的产生。 reset_line 信号用于控制复位脉冲,而 presence_pulse 用于检测存在脉冲。注意,这些时序参数需要根据实际的FPGA时钟频率进行调整。

通信协议的Verilog实现

要在Verilog中实现DS18B20通信协议的其余部分,需要考虑时序控制、信号检测和数据帧的处理。接下来的章节将展开讨论这些实现的细节。

写时序的精确控制

写时序涉及向DS18B20写入数据位。主机需要在每个位的写周期内,精确控制数据线的电平。通常,在总线被拉低后约1微秒开始采样数据,之后总线必须在15微秒内回到高电平状态。

// Verilog代码片段,展示写数据位的逻辑reg write_bit_enable;always @(posedge clk) begin if (write_bit_enable) begin // 拉低数据线以写入数据位 data_line <= 1\'b0; #WRITE_ONE_TIME; // 写1的时间长度 data_line <= 1\'b1; // 释放数据线 #WRITE_ZERO_TIME; // 写0的时间长度 endend读时序的实现

读时序则是在主机读取DS18B20数据位时,对数据线进行精确采样。DS18B20在主机的读周期内将数据线拉低表示逻辑0,在不拉低的情况下释放数据线表示逻辑1。

// Verilog代码片段,展示读数据位的逻辑reg read_bit_enable;wire data_bit;always @(posedge clk) begin if (read_bit_enable) begin // 等待数据线有效 wait (data_line == LOW); #READ_PULSE_WIDTH; // 读脉冲宽度 data_bit = data_line; // 采样数据位 // 释放数据线 endend数据帧的生成和解析

DS18B20发送的数据帧为9至12位的温度数据。根据用户设定的分辨率,数据帧的格式可能会有所不同。为了在Verilog中处理这些数据帧,我们通常需要构建一个模块,该模块能够解析这些数据并转换成温度值。

// Verilog代码片段,展示数据帧解析的逻辑module ds18b20_frame_parser( input wire clk, input wire [7:0] data_frame, // 输入数据帧 output reg [15:0] temperature // 解析后的温度值);// 解析逻辑always @(posedge clk) begin // 根据数据帧格式解析温度值 // 这里需要根据DS18B20的数据手册进行位操作 // 假设温度值的表示为12位的补码形式 temperature <= {{4{data_frame[7]}}, data_frame[7:0]};endendmodule本节的内容涉及到了FPGA中实现DS18B20通信协议的关键技术细节,涵盖了时序控制和数据处理等方面。下一节将介绍如何在FPGA中实现DS18B20通信过程中的信号同步和错误处理。

5. 信号同步和错误处理

在数字系统设计中,确保信号的同步和对错误的处理是至关重要的。这不仅能够保障系统的稳定性,还能避免数据的丢失或错误。本章将深入讨论在FPGA设计中如何实现有效的信号同步机制,以及如何在硬件层面进行错误检测和纠正。

5.1 信号同步机制

在FPGA设计中,异步信号可能导致\"竞争条件\"和\"冒险\",这些问题如果不解决,就可能引发系统错误。信号同步的常用方法包括使用同步寄存器(D型触发器)和FIFO缓冲区。

5.1.1 同步寄存器

同步寄存器用于控制信号的时序,确保在时钟边沿到来时更新信号值。以下是一个简单的Verilog代码示例,展示了如何使用D型触发器同步信号:

module sync_register( input clk, // 时钟信号 input rst_n, // 同步复位信号,低电平有效 input async_signal, // 需要同步的异步信号 output reg sync_signal // 同步后的信号);always @(posedge clk or negedge rst_n) begin if (!rst_n) begin sync_signal <= 1\'b0; end else begin sync_signal <= async_signal; endendendmodule5.1.2 FIFO缓冲区

FIFO(First-In-First-Out)缓冲区常用于缓存数据流,可以有效处理异步数据源和目的设备之间的速率匹配问题。一个简单的FIFO同步设计如下:

module fifo_buffer( input clk, input rst_n, input wr_en, input rd_en, input [7:0] data_in, output reg [7:0] data_out, output reg full, output reg empty);// FIFO存储器数组reg [7:0] mem[255:0];// FIFO的读写指针reg [7:0] wr_ptr;reg [7:0] rd_ptr;// FIFO的计数器reg [7:0] fifo_counter;// FIFO写操作always @(posedge clk or negedge rst_n) begin if (!rst_n) begin wr_ptr <= 0; rd_ptr <= 0; fifo_counter <= 0; full <= 0; end else begin if (wr_en && !full) begin mem[wr_ptr] <= data_in; wr_ptr <= wr_ptr + 1; fifo_counter <= fifo_counter + 1; if (fifo_counter == 255) full <= 1; end endend// FIFO读操作always @(posedge clk or negedge rst_n) begin if (!rst_n) begin rd_ptr <= 0; empty <= 1; end else begin if (rd_en && !empty) begin data_out <= mem[rd_ptr]; rd_ptr <= rd_ptr + 1; fifo_counter <= fifo_counter - 1; if (fifo_counter == 0) empty <= 1; end endendendmodule5.2 错误处理

错误处理在硬件设计中同样重要,特别是在与外部设备如DS18B20传感器通信时。由于可能存在信号干扰或设备故障,所以在通信协议中实现错误检测和处理是必要的。

5.2.1 奇偶校验

奇偶校验是一种简单的错误检测方法,通过在数据中增加一个额外的位(校验位)来使数据的\"1\"的个数达到指定的数量(奇数或偶数)。这里是一个简单的奇偶校验生成模块的代码:

module parity_generator( input [7:0] data_in, output parity_bit);assign parity_bit = ^data_in; // 使用异或运算符实现奇偶校验位的生成endmodule5.2.2 CRC校验

循环冗余校验(CRC)是一种更为复杂且可靠的错误检测方法。CRC通过将数据视为一个长的二进制数,然后用一个预定的多项式除,得到的余数作为校验值。

实现CRC校验的代码如下:

module crc_generator( input [7:0] data_in, input clk, input reset, output reg [7:0] crc_out);always @(posedge clk or posedge reset) begin if (reset) begin crc_out <= 8\'hFF; // 初始值设置为全1 end else begin crc_out <= (crc_out << 1) ^ ((crc_out[7] == 1\'b1) ? 8\'h18 : 8\'h00); // 用预定多项式进行计算 endendendmodule在下一章,我们将探讨如何在FPGA设计中进行功耗分析和优化,特别是在与DS18B20温度传感器交互过程中如何降低功耗。同时,我们将详细解析如何利用Verilog对DS18B20的原始数据进行解析,提取出精确的温度信息,并在FPGA系统中进一步处理这些数据以满足实际应用需求。

本文还有配套的精品资源,点击获取

简介:本文介绍了如何在FPGA平台上使用Verilog语言设计一个系统来控制和读取DS18B20数字温度传感器的数据。通过这个项目,可以学习到FPGA的编程、数字系统设计以及温度传感器的应用。项目将覆盖DS18B20的初始化、时序控制、数据读取和显示等关键功能,旨在提供一个实际的数字系统设计和硬件编程的学习案例。

本文还有配套的精品资源,点击获取